(54) УСТРОЙСТВО ДЛЯ УМНОЖЕРШЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения | 1975 |

|

SU1206773A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| Накапливающий перемножитель | 1981 |

|

SU987618A1 |

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для умножения @ -разрядных чисел | 1984 |

|

SU1256018A1 |

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для умножения п-разрядных чисел | 1978 |

|

SU734683A1 |

I

Изобретение относится к вычислительной технике и может найти применение при реализации скоростных методов умножения в цифровых устройствах.

Известно устройство с одновременным умножением на два н более разрядов множителя, в которых частичное произведение формируется при сдвиге множителя на соответствующее (два или более) число разрядов с одновременным их анализом и исправлением 1.

Наиболее близким техническим решением К предложенному является устройство для умножения, содержащее регистр множимого, выход которого соединен с первым входом коммутатора, второй вход которого соединен с выходом регистра множителя, а - с первым входом накапливающего сумматора, выход которого подключен к входу регистра множителя 2.

Недостатком этих устройств является наличие в них кроме основного арифмет1 ко-логического блока специальной схемы анализа и исправления разрядов множителя, которая срабатывает каждый раз при сдвиге множителя и получеинк частичного произведения в накапливающем сумматоре и, таким образом, ограничивает максимальную частоту работы устройства умножения. Исправление всех разрядов множителя производится последовательно в каждом цикле формиро вания частичного произведения.

Цель изобретение - повышение быстродействия за счет одновременного исправления всех пар разрядов множителя и совмещения этой операции с операцией введения множимого (множителя), а также за счет выполнения этой операции на основном арифметико-логическом блоке.

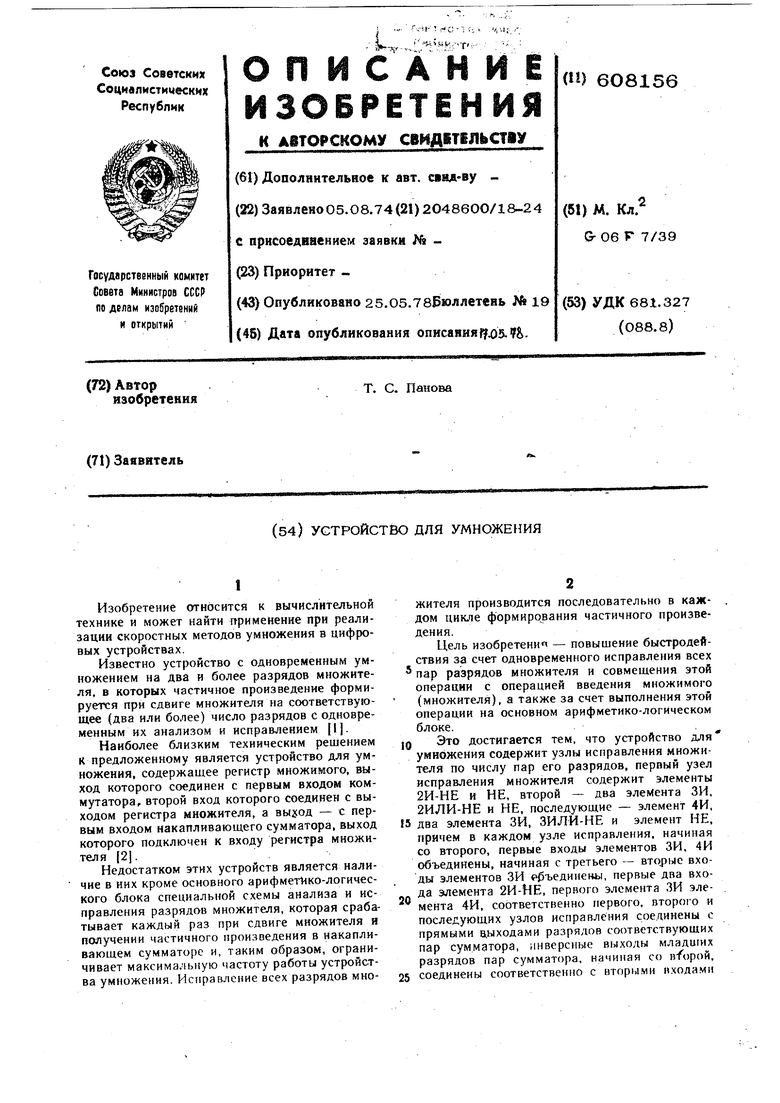

Это достигается тем, что устройство для умиожения содержит узлы исправления множителя по числу пар его разрядов, первый узел исправления множителя содержит элементы 2И-НЕ и НЕ, второй - два элемента ЗИ, 2ИЛИ-НЕ и НЕ, последующие - элемент 4И,

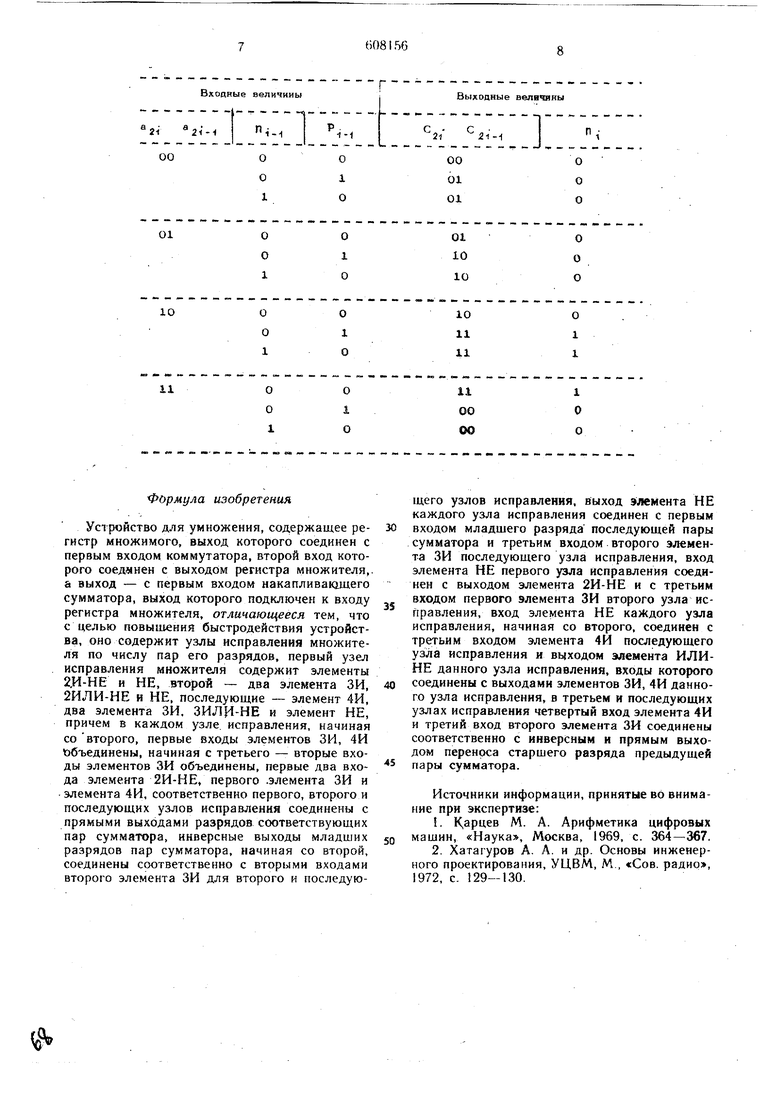

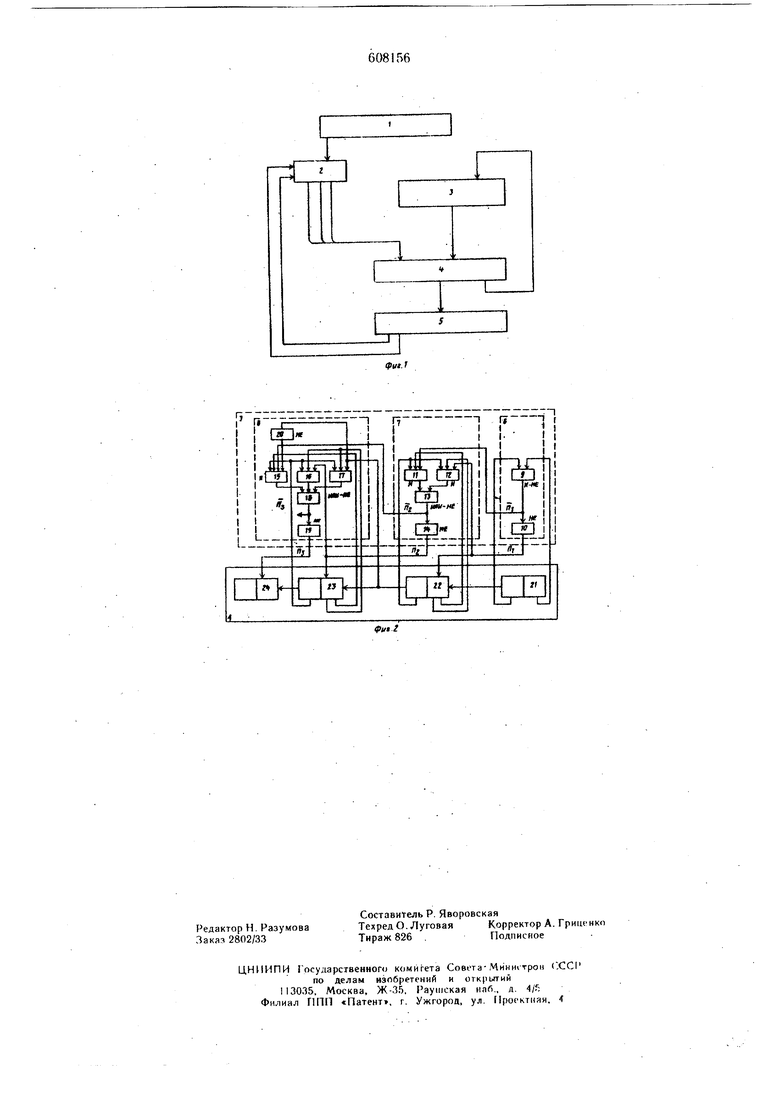

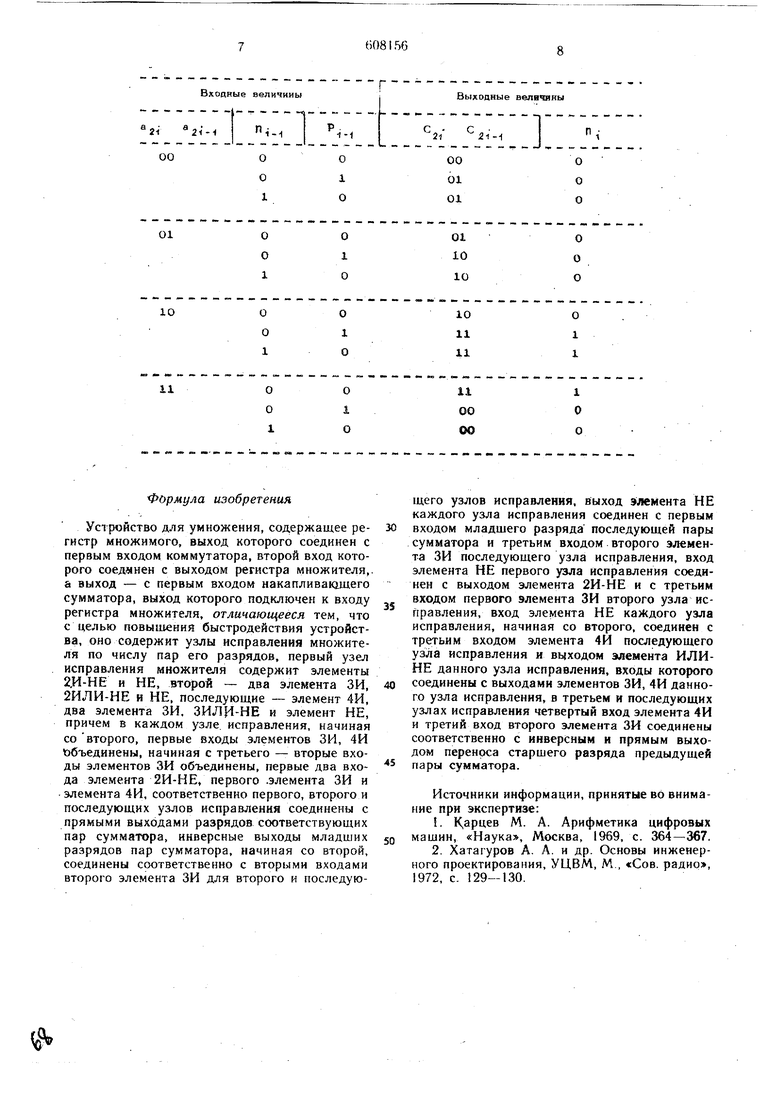

два элемента ЗИ, ЗИЛИ-f-lE и элемент НЕ, причем в каждом узле исправления, начиная со второго, первые входы элементов ЗИ, 4И объединены, начиная с третьего - вторые вхоы элементов ЗИ е0ъединеш 1, первые два вхоа элемента 2И-НЕ, первого элемента ЗИ элемента 4И, соответственно ггервого, второго и последующих узлов исправления соединены с прямыми выходами разрядов соответствующих пар сумматора, инверсные выходы младших разрядов пар сумматора, начиная со вfopoй, оединены соответственно с вторы.мн входами второго элемента ЗИ для второго и последующих узлов исправления, выход элемента НЕ каждого узла иснравления соединен с первым входом младшего разряда последующей пары сумматора н третьим входом второго элемента ЗИ последующего узла исправления, вход элемента ИЕ первого узла исправления соединен с выходом элемента 2И-НЕ и с третьим входом первого элемента ЗИ второго узла исправления, вход элемента НЕ каждого узла исправления, начиная со второго, соединен с третьим входом элемента 4И последующего узла исправления и выходом элемента ИЛИ-PiE данного узла исправления, входы которого соединены с выходами элементов ЗИ, 4И данно1О узла исправления, -в третьем и последующих узлах исправления четвертый вход элемента 4И и третий вход второго элемента ЗИ соединены соответственно с инверсным и прямым выходом переноса старшего разряда предыдущей пары сумматора На фиг. 1 приведена структур1ная схема устройства и схема его включения; на фиг. 2 - структурно-логическая схема исправления разрядов множителя. Устройство состоит из регистра 1 множимого, коммутатора 2, блока 3 коррекции, накапливающего сумматора 4, регистра 5 множителя. Блок 3 коррекций состоит из первого 6, второго 7, третьего 8 и т.д. узлов исправления множителя. Узел 6 исправления содержит элемент 2И-НЕ 9, НЕ iO. Узел 7 исправления содержит два элемента ЗИ И, 12, элемент 2ИЛИ-НЕ 13 и НЕ 14. Узел 8 исправления содержит элемент 4И 15, два элемента ЗИ 16, 17, элемент ЗИЛИ-НЕ 18 и два элемента 19, 20. Накапливающий сумматор 4 содержит пары разрядов 21, 22, 23, 24 и т.д. Исправленный множитель находится в накапливающем сумматоре 4, который в обшем случае представляет собой комбинационную часть сумматора сквозной цепью переноса и/ накапливающую часть. Под управлением одной из микрокоманд множимое записывается в регистр 1 множимого, а неисаравленный множитель поступает из регистра хранения накапливающего сумматора 4 на вход блока 3 коррекции, которая состоит из узлов 6, 7, 8 исправления множителя (по числу пар разрядов множителя). Блоком 3 коррекции вырабатываются сигналы исправления, которыепоступают на соответствующие входы разрядов накапливающего сумматора 4, а затем суммируются с его содержимым, т.е. неисправленными разрядами множителя. Результат суммирования, появляющийся на выходах комбинационной части сумматора и накапливающей части , сумматора, является уже значением всех исправленных разрядов множителя, который записывается в регистр 5 множителя. По окончании процесса записи множимого, формированиям записи исправленных разрядов множителя воздействие выходов схемы 3 коррекции на входы накапливающего сумматора 4 блокируются отсутствием ранее выработанной микрокоманды. Содержимое накапливающего сумматора обнуляется. После этого под действием уже другой микрокоманды происходит формирование частичных произведений. При этом,, с каждым сдвигом разрядов исправленного множителя множимое из регистра 1 через коммутатор 2, который представляет собой набор лог }ческих элементов И, ИЛИ и инверторов, поступает на входы накапливающего сумматора 4 в соответствующей форме в зависимости от кода пары исправленных разрядов множителя. В предлагаемом устройстве для одновременного исправления всех пар разрядов множителя в одном цикле используется известный способ исправления пары разрядов множителя, когда код данной пары разрядов увеличивается на единицу младщего разряда, если код предыдущей пары множителя имел вид 11 (три). Формирование единиц, назовем их сигналами исправления п/, (где i - порядковый номер пары разрядов множителя) осуществляется в предлагаемом устройстве специальным блоком 3 коррекции. Блок коррекции 3 содержит узлы исправления 6, 7, 8 и т.д. по числу пар разрядов множителя.. Процесс суммирования соответствующих сигналов исправления (ni) с младшими разрядами соответствующих пар разрядов неисправленного множителя (a2ia2i-i) осуществляется в комбинационном сумматоре со сквозной цепью переноса (накапливающий сумматор 4), входящем в состав любого арифметико-логического устройства. Исправленные разряды множителя C2i C2i.-i), т.е. увеличенные на единицу младщего разряда, коды, на соответствующих выходах пар разрядов комбинационной части сумматора появляются только в том случае, если предыдущая исправленная пара имела код 11 (три) или код 100 (четыре). Факт появления кода 100 фиксируется автоматически появлением сигнала Р{ на выходе сквозного переноса в старшем разряде соответствующей пары разрядов сумматора. Факт появления исправленного кода 1I в предлагаемом устройстве фиксируется сигналом исправления П;, вырабатываемом соответствующей схемой исправления., Исправленная пара разрядов множителя C2i Cji-i будет иметь код 11 только в том случае, если код исправляемой aji а- -: пары имеет вид 10 (два) и присутствует или сигнал переноса Pi-i или сигнал исправления nj-j, возникающие при испрааленил предыдущей пары разрядов множителя, или если код исправляемой aji a2i-i пары имеет код И (три), а сигналы переноса Pi-i и исправления lij-i отсутствуют при исправлении предыдущей пары разрядов множителя. Таким образом сигнал исправления П; возникав- только тогда, когда исправленная пара €2; Cst-i имеет код П. в таблице приведены истинности для формирования сигналов исправления Ili н исправленных значений любой пары разрядов множителя Cji Czi-i при различных кодах неисправленных разрядов множителя as, s-2,- и различных сочетаниях сигнала исправления П-,-1 и переноса . Из таблицы истинности комбинация Пг-, } и Р,| I исключены, так как одновременное появление сигналов П,,,, и Р; -1 невозможно. Таким об.разом, появление сигнала исправления rii представлено следующим выражением:TTi a2ia2i-,ni-,P,-ivaiiaii-,ni.,vai,a2i-iPi-«При исправлении первой пары разрядов мно жителя i 1 сигнал исправления П1. (схема исправления 6) co лaJCHo выражению (1) будет П| аза |ПoPo a2a|Пo i a2ajPo, так как По РО О и По РО J. следовательно П| ага,. (2) Исправленный код первой пары разрядов множителя CjCi формируется на первой паре разрядов сумматоров путем суммирования первой неисправленной пары разрядов множителя а за i с нулевыми несуществующими значениями сигналов По и РО. Следовательно, при исправлении первой пары разрядов множителя исправленный код будет появляться без измейения, а сигнал переноса Р| из старшего (второго) разряда первой пары разрядов сумматора будет всегда отсутствовать (Р| 0). При исправлении второй пары разрядов множителя i 2 сигнал исправления П2 (схема исправления 7) согласно выражению () будет, Пг а4азП|Р|(а4аяП1Уа4азР1, так как 1, следовательно Па а4азП (. (3) Исправленный код второй пары разрядов множителя формируетсяна второй паре разрядов сумматора путем суммирования второй неисправленной пары разрядов множителя а 43 а с сигналом исправления П| и переноса Р| О, возникших при исправлении первой пары разрядов множителя. Исправленный код второй пары разрядов множителя будет появглиться без изменения, ecviH i О и бу.ит увеличиваться на единицу младшего разряда, если Oj . Сигнал переноса Р при исправлении второй пары разрядов множителя может иметь как нулевое, так и единичное значение. Следовательно, при исправлении третьей пары разрядов множителя i 3 сигнал исправления Пз (узел исправления 8) согласно выражению () будет: Пз айа5П2Р2 ава5П2маваоР (4) Исправленный код третьей пары разрядов множителя CfiCs формируется на третьей паре разрядов сумматора путем сложения третьей неисправленной пары разрядов множителя agSj с сигналами исправления Пг и переноса Рг, возникших при исправленин второй пары разрядов множителя. Исправление последующих пар разрядов множителя (после третьей) и формирование сигналов исправления осуществляется также, как при исправлении третьей пары разрядов множителя. На фиг. 2 узлы исправления 6, 7, 8, н т.д. реализованы -согласно выражениям 2, 3 н 4. Следует отметить, что время распространения сигналов исправления (Fit) в блоке 3 коррекции соизмеримо со временем распространення сигналов переноса (Pi) в сумматоре 4. Работу схемы также рассмотрим на прнмере исправления восьмиразрядного кода множителя ООП 10 1. Исправление разрядов производится попарно с младщнх разрядов, т.е. справа налево. На выходе элементов 10 н П возникают сигналы исправления П| н Па соответственно по элементам 9 и 12. Сигнал исправления Пз на выходе элемента 9 отсутствует, так как элемент 15 запрещен выходами элемента 13, а элементы 16 и 17 инверсным выходом пары сумматора 23. Таким образом, исправление второй и третьей пары множителя осуществляется соответственно в 22 н 23 паре сумматора по сигналам исправления (П,, Пг), а исправленне четвертой пары - а 24 паре сумматора по сигналу переноса из 23 пары сумматора. Исправленный множитель имеет вид 0100 1П; Кроме того, достоинством предложенного устройства является то исправление множителя, которое Во времй приема множимого приводит к упрощению устройства управления.

00

О о 1.

о 1 о Формула изобретения Устройство для умножения, содержащее регистр множимого, выход которого соединен с первым входом коммутатора, второй вход которого соединен с выходом регистра множителя,. а выход - с первым входом накапливакицего сумматора, выход которого подключен к входу регистра множителя, отличающееся тем, что с целью повышения быстродействия устройства, оно содержит узлы исправления множителя по числу пар его разрядов, первый узел исправления множителя содержит элементы 2.И-НЕ и НЕ, второй - два элемента ЗИ, 2ИЛИ-НЕ и НЕ, последующие - элемент 4И, два элемента ЗИ. ЗИЛИ-НЕ и элемент НЕ, причем в каждом узле, исправления, начиная со второго, первые входы элементов ЗИ, 4И объединены, начиная с третьего - вторые входы элементов ЗИ объединены, первые два входа элемента 2И-НЕ, первого .элемента ЗИ и элемента 4И, соответственно первого, второго и последующих узлов исправления соединены с прямыми выходами разрядов соответствующих пар сумматора, инверсные выходы младших разрядов пар сумматора, начиная со второй, соединены соответственно с вторыми входами второго элемента ЗИ для второго и последую00 О1

о о о О1 щего узлов исправления, выход элемеита НЕ каждого узла исправления соединен с первым входом младшего разряда последующей пары сумматора и третьим входом второго элемента ЗИ последующего узла исправления, вход элемента НЕ первого узла исправления соединен с выходом элемента 2И-НЕ и с третьим входом первого элемента ЗИ второго узла исправления, вход элемента НЕ каждого узла исправления, начиная со второго, соединен с третьим входом элемента 4И последующего узла исправления и выходом элемента ИЛИНЕ данного узла исправления, входы которого соединены с выходами элементов ЗИ, 4И данного узла исправления, в третьем и последующих узлах исправления четвертый вход элемента 4И и третий вход второго элемента ЗИ соединены соответственно с инверсным н прямым выходом переноса старшего разряда предыдущей пары сумматора. Источники информации, принятые во внимание при экспертизе: . К,арцев М. А. Арифметика цифровых машин, «Наука, Москва, 1969, с. 364-367. 2. Хатагуров А. А. и др. Основы инженерного проектирования, УЦВМ, М., «Сов. радио, 1972, с. 129-130.

Авторы

Даты

1978-05-25—Публикация

1974-08-05—Подача