1208536

сравнения подключен к выходу второго регистров являются управляющими вхо- ре.гнстра, входы первого и второго

дами контроллера.

«

Изобретение относится к автоматическим дискретным управляющим системам и может быть использовано для логического управления по заданным программам техническими объектами.

Цель изббретения - расширение функциональных возможностей путем обеспечения многопрограммного режима работы.

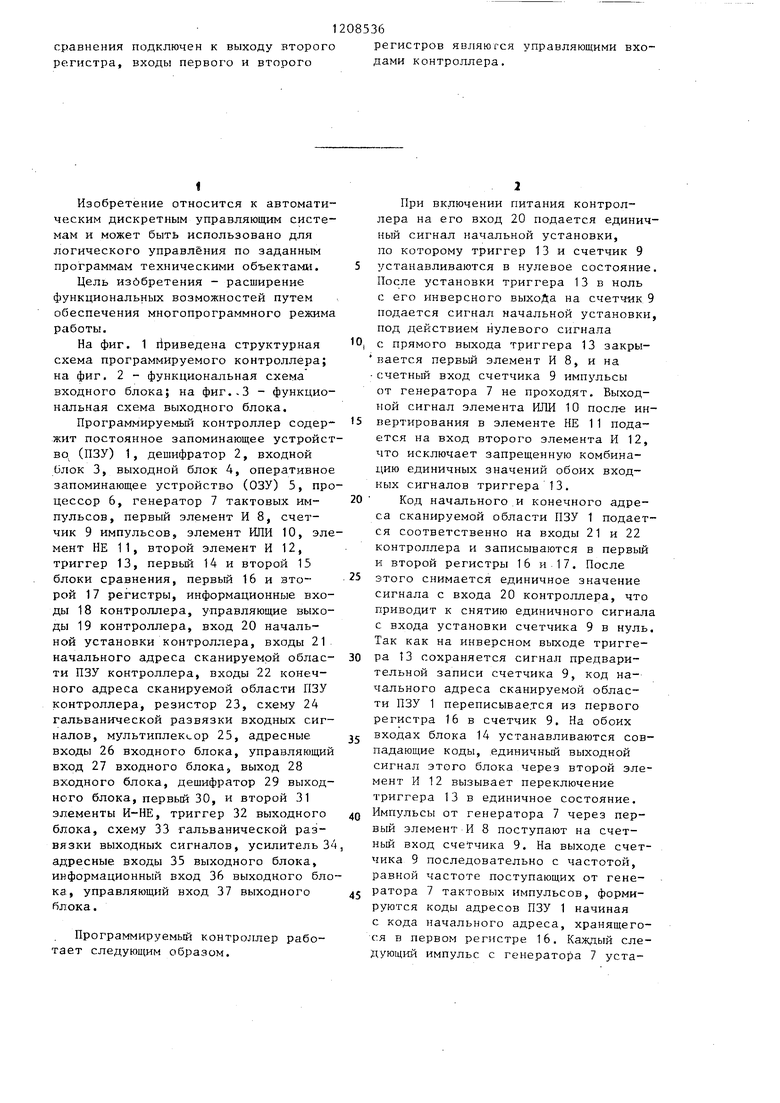

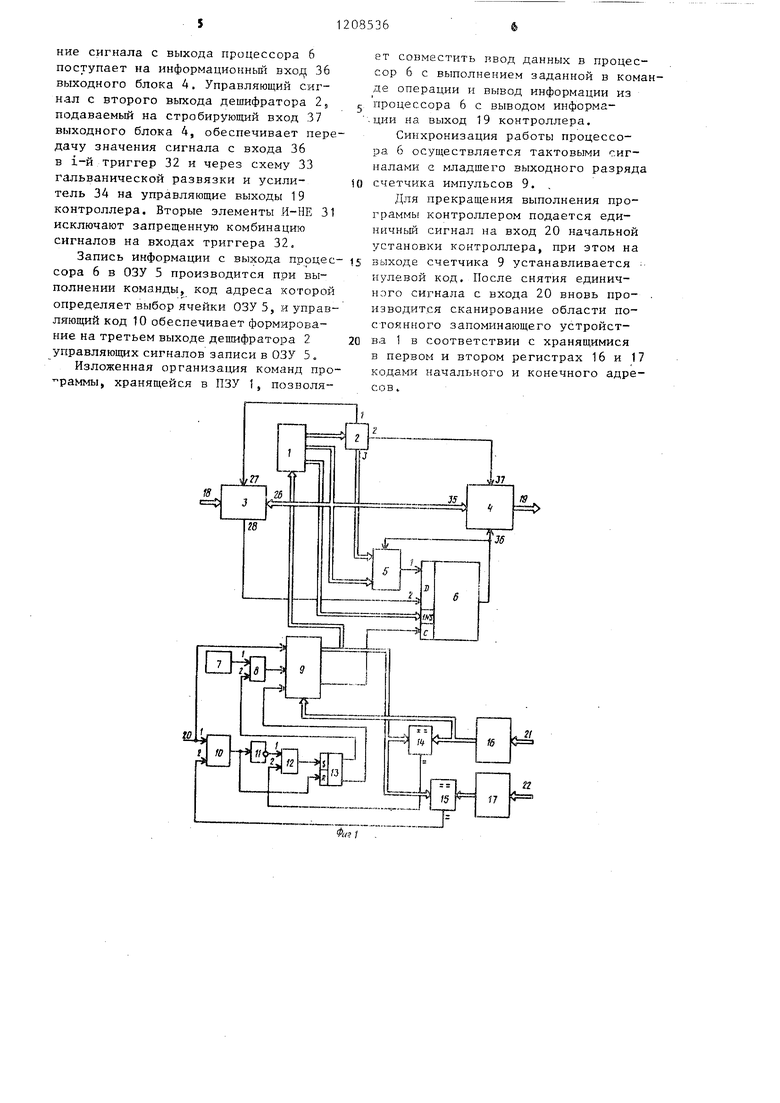

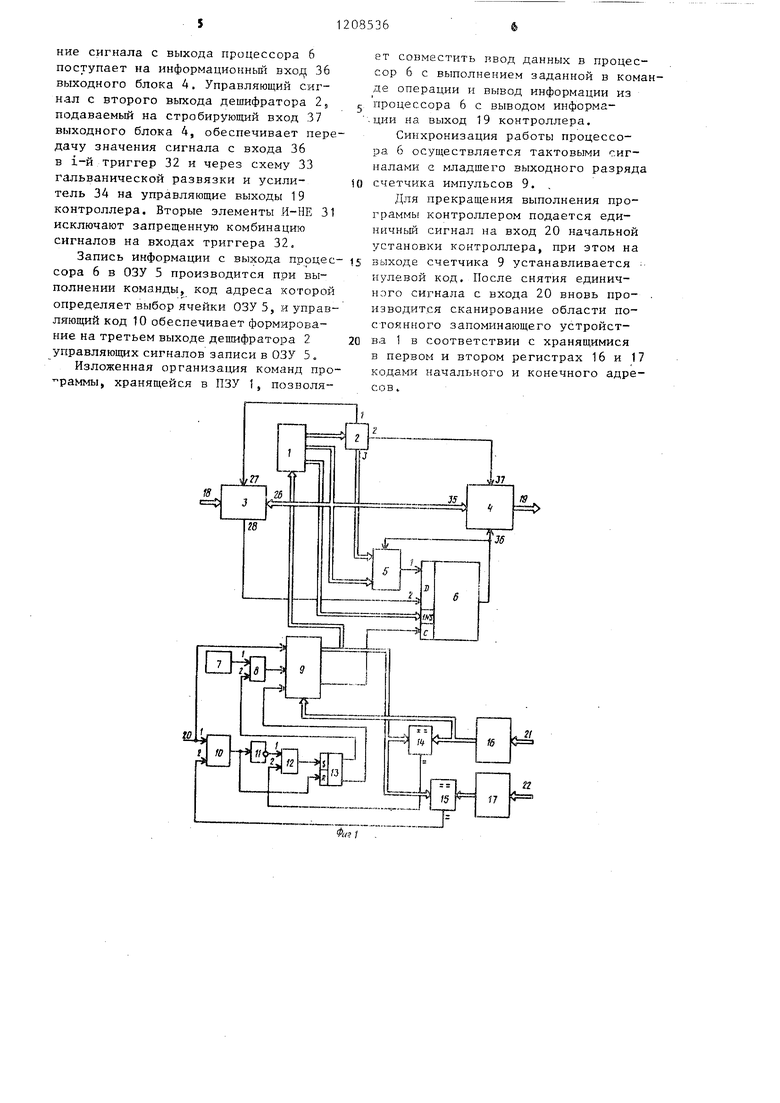

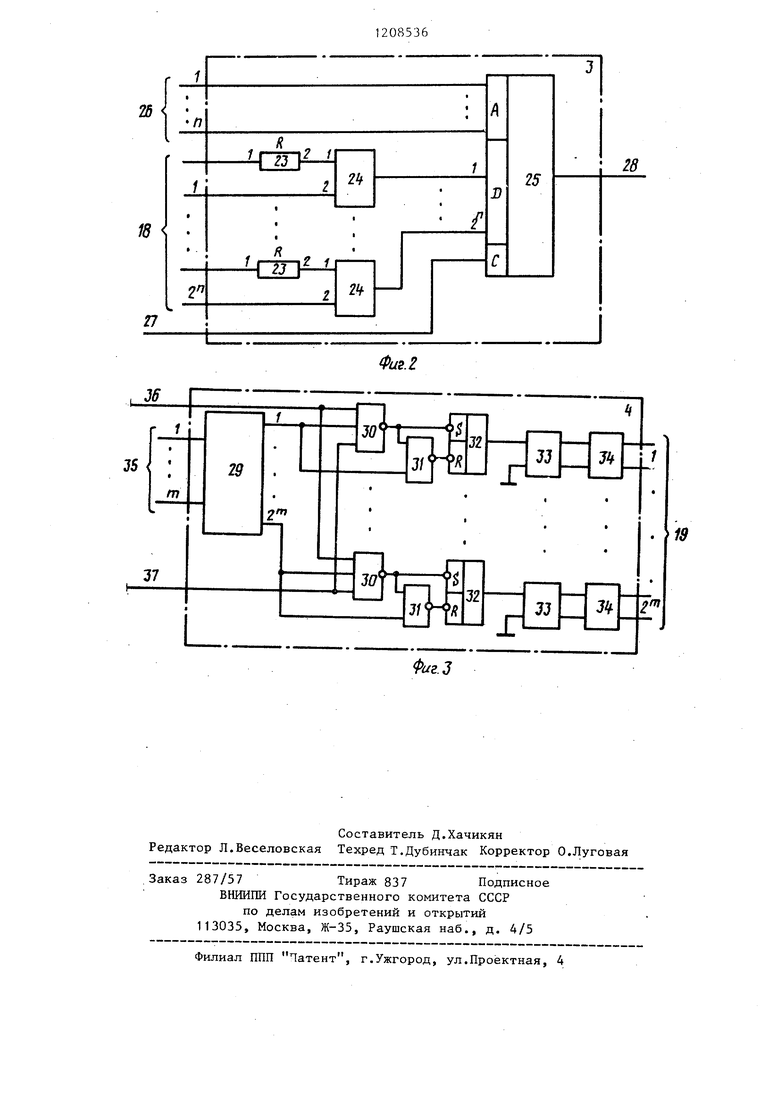

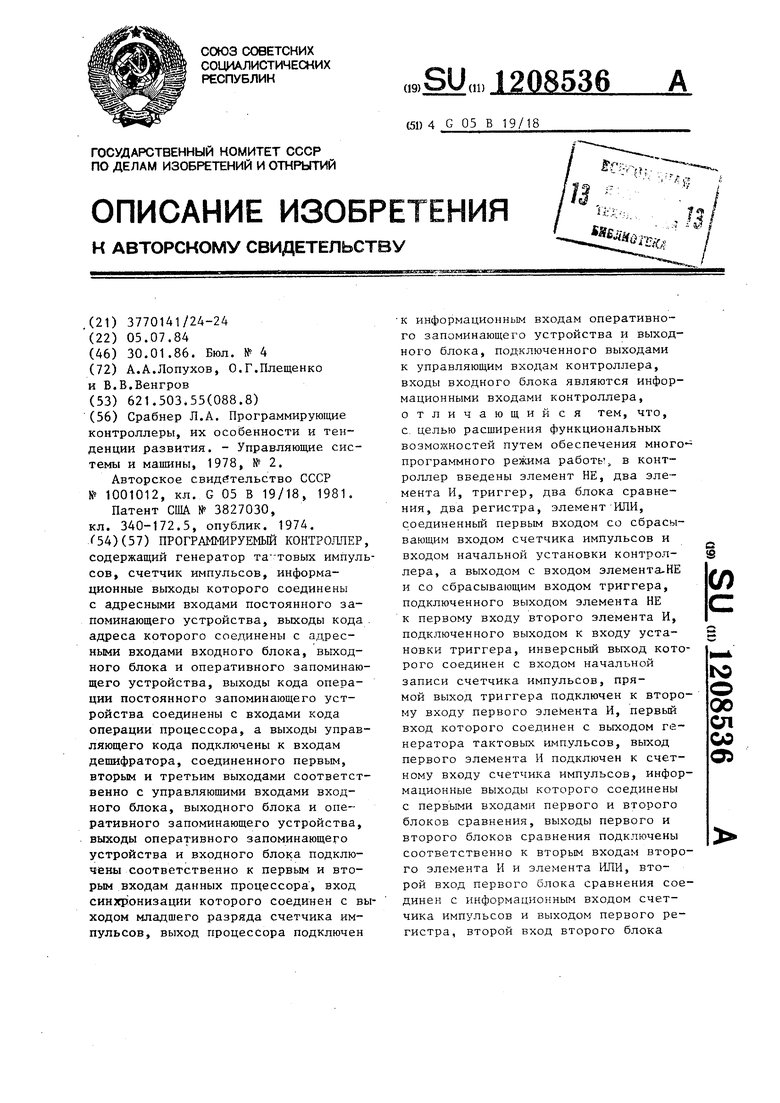

На фиг. 1 приведена структурная схема программируемого контроллера; на фиг. 2 - функциональная схема входного блока; на фиг.-З - функциональная схема выходного блока.

Программируемый контроллер содер жит постоянное запоминающее устройство (ПЗУ) 1, дешифратор 2, входной блок 3, выходной блок 4, оперативное запоминающее устройство (ОЗУ) 5, процессор 6, генератор 7 тактовых импульсов, первый элемент И 8, счетчик 9 импульсов, элемент ИЛИ 10, элемент НЕ 11, второй элемент И 12, триггер 13, первьм 14 и второй 15 блоки сравнения, первый 16 и второй 17 регистры, информационные входы 18 контроллера, управляющие выходы 19 контроллера, вход 20 начальной установки контроллера, входы 21 начального адреса сканируемой области ПЗУ контроллера, входы 22 конечного адреса сканируемой области ПЗУ контроллера, резистор 23, схему 24 гальванической развязки входных сигналов, мультиплексор 25, адресные входы 26 входного блока, управляющий вход 27 входного блока, выход 28 входного блока, дешифратор 29 выходного блока, первый 30, и второй 31 элементы И-НЕ, триггер 32 выходного блока, схему 33 гальванической развязки выходных сигналов, усилитель 34 адресные входы 35 выходного блока, информационный вход 36 выходного блока, управляющий вход 37 выходного блока.

Программируемый контроллер работает следующим образом.

регистров являютс

дами контроллера.

При включении питания контроллера на его вход 20 подается единичный сигнал начальной установки, по которому триггер 13 и счетчик 9

устанавливаются в нулевое состояние. После установки триггера 13 в ноль с его инверсного выхоДа на счетчик 9 подается сигнал начальной установки, под действием нулевого сигнала

с прямого выхода триггера 13 закры- вается первый элемент И 8, и на счетный вход счетчика 9 импульсы от генератора 7 не проходят. Выходной сигнал элемента ИЛИ 10 посл-е инвертирования в элементе НЕ 11 подается на вход второго элемента И 12, что исключает запрещенную комбинацию единичных значений обоих входных сигналов триггера 13.

Код начального и конечного адреса сканируемой области ПЗУ 1 подается соответственно на входы 21 и 22 контроллера и записываются в первый и второй регистры 16 и 17. После

этого снимается единичное значение сигнала с входа 20 контроллера, что приводит к снятию единичного сигнала с входа установки счетчика 9 в нуль. Так как на инверсном выходе триггера 13 сохраняется сигнал предварительной записи счетчика 9, код начального адреса сканируемой области ПЗУ 1 переписывается из первого регистра 16 в счетчик 9. На обоих

входах блока 14 устанавливаются совпадающие коды, .единичный выходной сигнал этого блока через второй элемент И 12 вызывает переключение триггера 13 в единичное состояние.

Импульсы от генератора 7 через первый элемент И 8 поступают на счетный вход счетчика 9. На выходе счетчика 9 последовательно с частотой, равной частоте поступающих от генератора 7 тактовых импульсов, формируются коды адресов ПЗУ 1 начиная с кода начального адреса, хранящегося в первом регистре 16. Каждый следующий импульс с генератора 7 устанавливает на выходе счетчика У новый адрес, который на единицу больше предыдущего, и так до тех пор, пока не будет установлен адрес, равный конечному адресу сканируемой области ПЗУ 1, хранящемуся во втором регистре 17. При совпадении кода на выхр- де счетчика 9 с кодом конечного адреса, находящегося во втором регистре 17, блок 15 формирует сигнал, который через элемент ИЛИ 10 устанавливает триггер 13 в нулевое состояние. После этого закрывается первьш элемент И 8 и генератор 7 отключается от счетного входа счетчика 9. Одновременно единичный сигнал с инверсного выхода триггера 13 обеспечивает начальную установку счетчика 9 по коду начального адреса хранящемуся в регистре 16. При этом формируется единичное значение сигнала на выходе блока 14, нулевое - на выходе блока 15. Указанные сигналы вызывают переключение триггера 13 в единичное состояние, и цикл счета адресов ячеек ПЗУ 1 повторяется.

В соответствии с кодами адресов, поступающих с выхода счетчика 9 на адресные входы ПЗУ 1, на выходах последнего формируются коды команд, записанных в его ячейки (производится считывание команд, хранящихся в сканируемых ячейках). Каждая команда содержит: код адреса входного или выходного сигнала процессора 6, код операции, выполняемой процессором 6; код управления режимами передачи информации, входного блока 3, выходного блока 4 и ОЗУ 5.

Код адреса поступает на адресные входы входного блока 3, выходного блока 4, ОЗУ 5 и обеспечивает выбор определенного входа на информационных входах 18, определенного выхода из управляющих выходов 19 контроллера или выбор ячейки ОЗУ 5.

Управляющий код команды, поступающий на вход дешифратора 2, является двухразрядным и означает: 00 - считывание сигнала с входного блока 3; 01 .- считывание сигнала из ОЗУ 5; 10 - запись в ОЗУ 5 выходного сигнал процессора 6; 11 - запись в выходной блок 4 выходного сигнала процессора 6.

Дешифратор 2 в соответствии со значением разрядов управляющего кода формирует сигналы на управляющие входы входного блока 3, выходного блока 4 и ОЗУ 5.

Код операции с выходов ПЗУ 1 поступает в процессор 6. Операндами являются содержимое внутренних регистров процессора 6 и сигналы, поступающие на вход процессора 6 с вход- . ного блока 3 и ОЗУ 5 в соответствии с кодом адреса в команде.

Ввод дйнных в процессор 6 реализуется следующим образом.

В команде, код адреса в которой определяет обращение к входному блоку 3, задается управляющий код 00,

обеспечивающий единичное значение сигнала на первом выходе дешифратора 2. После считывания данной команды из ПЗУ 1 код адреса, подаваемый на адрес- ные входы 26 мультиплексора 25, определяет выбор i-й пары информационных входов 18 контроллера; управляющий сигнал cjiepBoro выхода дешифратора 2 подается на стробирующий вход 27 мультиплексора 25, обеспечивая передачу

сигнала с i-й пары информационных входов 18 через ограничивающий входной ток резистор 23 и схему ггуьва- нической развязки 24 на выход 28 мультиплексора 25, информационньй выход входного блока 3 и второй вход данных ..процессора 6. Ввод данных : в процессор 6 из ОЗУ 5 производится при выполнении команды, код адреса которой определяет выбор ячейки ОЗУ 5 и управляющий код 01 команды обеспечивает формирование на третьем выходе дешифратора 2 управляющих сигналов зап СИ в ОЗУ 5.

Коды операций, поступающие в процессор 6, обеспечивают вьтолнение одноместных и двуместных операций, запись результатов операций во внутренние регистры процессора 6, пересылку содержимого определенного внутреннего регистра на выходные шины

процессора 6.

Вывод информации на управляющие выходы 19 контроллера реализуется следующим образом.

В команде, код адреса в которой

определяет обращение к выходному блоку 4, задается управляющий код 11, обеспечивающий единичное значение сигнала на втором выходе дешифратора 2. Код адреса, поступающий на

входы 35 дешифратора 29, формирует единичный сигнал на соответствующем (i-м) выходе дешифратора 29 и втором входе i-го элемента И-НЕ 30. Значе

ние сигнала с выхода процессора 6 поступает на информационньш BXO;J 36 выходного блока А. Управляющий сигнал с второго выхода дешифратора 1 подаваемый на стробирующий вход .37 выходного блока 4, обеспечивает передачу значения сигнала с входа 36 в i-й триггер 32 и через схему 33 гальванической развязки и усилитель 34 на управляющие выходы 19 контроллера. Вторые элементы И-НЕ 31 исключают запрещенную комбинацию сигналов на входах триггера 32,

Запись информации с выхода процессора 6 в ОЗУ 5 производится при выполнении команды, код адреса которой определяет выбор ячейки ОЗУ 5, и управляющий код 10 обеспечивает формирование на третьем выходе дешифратора 2 управляющих сигналов записи в ОЗУ 5.

Изложенная организация команд про- раммы, хранящейся в ПЗУ 1, позволяет совместить пвод данных в процессор 6 с выполнением заданной в команде операции и вывод информации из процессора 6 с выводом информа- ции на выход 19 контроллера.

Синхронизация работы процессора 6 осуществляется тактовыми сигналами е младшего выходного разряда

счетчика импульсов 9. ,

Для прекращения выполнения программы контроллером подается единичный сигнал на вход 20 начальной установки контроллера, при этом на

выходе счетчика 9 устанавливается нулевой код. После снятия единичного сигнала с входа 20 вновь про- . изводится сканирование области постоянного запоминающего устройстна 1 в соответствии с хранящимися в первом и втором регистрах 16 и 17 кодами начального и конечного адресов.

Л

10

36

19

т

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Селекторный канал | 1982 |

|

SU1053096A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

Составитель Д.Хачикян Редактор Л.Веселовская Техред Т.Дубинчак Корректор 0.Луговая

Заказ 287/57Тираж 837 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП Патент, г.Ужгород, ул.Проектная, 4

| Срабнер Л.А | |||

| Программирующие контроллеры, их особенности и тенденции развития | |||

| - Управляющие системы и машины, 1978, № 2 | |||

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США № 3827030, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1986-01-30—Публикация

1984-07-05—Подача