3. Устройство по п. 1, отличаю щ е е с я тем, что генератор тестов выполнен в виде блока ввода информации, блока памяти, формирователя импульса и счетчика адреса, при этом первая и вторая группы выходов, а также выходы с третьего по шестой генератора тестов соедине.ны с соответствующими выходс1ми блока памяти, первый вход которого соединен с первым входом счетчика адреса и вторым входом генератора тестов, первый вход которого соединен с пер-т выми входом счетчика адреса и входом формирователя импульса, выход которого соединен с вторым входом блока памяти, третий вход которого соединен с первым выходом блока ввода информации, второй выход которого-соединен с третьим входом счетчика адреса, выход которого соединен с четвертым входом блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных схем | 1983 |

|

SU1171795A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1479899A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1430914A1 |

| Устройство контроля интегральных схем | 1986 |

|

SU1370634A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1348835A1 |

| Устройство для контроля контатирования интегральных схем | 1982 |

|

SU1049912A1 |

| Устройство для параметрического контроля интегральных схем | 1981 |

|

SU985755A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство параметрического контроля интегральных схем | 1985 |

|

SU1287060A1 |

| СПОСОБ КОНТРОЛЯ КОНТАКТИРОВАНИЯ КМОП-БИС И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2009518C1 |

1. УСТРОЙСТВО КОНТРОЛЯ. ИНТЕГРАЛЬНЫХ СХЕМ, содержащее генератор тестов, первая группа .выходов которого подключена к входам интегральной схемы, а первый его вход соединен с первым выходом генератора тактовых импуль.сов, многоканальный компаратор, выход которого соединен с первым входом регистра индикации, отличающеес я тем, что, с целью повышения Нс1дежности контроля путем дополнительного контроля тока потребления выходных ключей интегральных схем, в него введены блок электронных ключей, блок нагрузок, компаратор, многоканальный генератор напряжений, первый и второй инверторы, элемент ИЛИ, первый и второй элементы И и шина Пуск, при этом вторая группа выходов rebiepaTO- pa тестов соединена с первой группой входов многоканального компаратора, вторая группа входов которого соединена с первыми группами входов блока нагрузок выходов блока электронных ключей, второй выход которого соединен с вторыми-- входами блока нагрут зок и компаратора, первый вхрд которого соединен с первым выходом многоканального генератора напряжений, : второй выход кЪторого соединен с третьим входом многоканального ком- i паратора, четвертый вход которого соединен с выходом второго элементд И, первый вход которого соединен с первым входом первого элемента И и вторым выходом генератора тактовых импульсов, первый вход которого соединен с вторым входом генератора тестов и шиной Пуск, а второй вход соединен с выходом элемента ИЛИ, первый вход которого соединен с выхог дом многоканального компаратора, второй вход соединен с вторым .входом регистра индикации и выходом компаратора , а третий вход соединен с третьим выходом генератора тестов и третьим входом регистра индикации, четвертый вход которого соединен с шиной Пуск, четвёртый выход генератора тестов соединен с вторым входом блока электронныхключей и входом первого инвертора, выход которо- g го соединен с уретьим входом блока (Л электронных ключей, пятый вьЬсод генератора тестов соединен.с третьим входом компаратора, четвертый вход )которого соединен с .выходом первого элемента И, второй вход которого со- g единен с шестым выходом генератора тестов и входом второго инвертора, выход которого соединен с вторым входом второго элемента И, первая труппа входов блока электронных ключО чей соединена с выходами интеграль,ной схемы. эо 2. Устройство по п. 1, -о т 00 |чающееся тем, что,блок электронных ключей выполнен в виде первой и второй групп электронных ключей, входы которых соединены с йервой группой входов блока электронных ключей, выходы первой группы электронных ключей соединены с вторым выходом блока электронных ключей, первая группа выходов которого соединена с выходгми второй группы электронных ключей, управляющие входы . которых соединены с третьим входом блока электронных ключей , второй вход которого соединен с управляюшлми в:(содами первой группы электронных ключей.

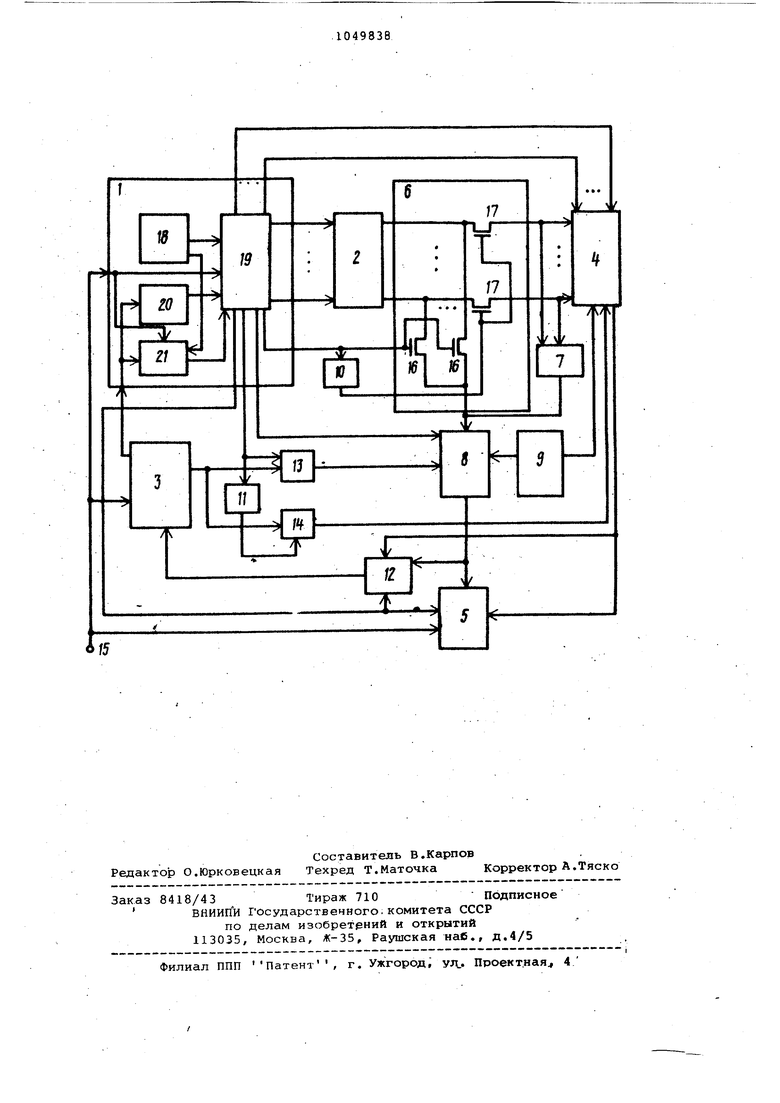

Иэ.обретение относится к контролю электронных схем и может быть испол зовано для контроля интегральйых схем, в частности микрокалькуляторо Известно устройство для контроля интегральных ехал, содёржсццее блок памяти, соединенный с первой и второй груидайи,элёктррн;ных ключей, уп рав л яющие входе к отсфых соединены с вы) блсжа управлей 1я, выходы группы ключ-ей соединены с . рбъек том койтроля и входом а мпЛитуд ного дискримдаатрра у первый вход , сравнения которого соединен с выходом блока управления, а второй вход сравнения - е выходами вторрй группы электрон1йых ключей, а вькод ;- с первы1)4 входом элемента ИЛИ l , Однако устройство не позволяет достаточно подао оценить потребление трка испытуемой: схемы Наиболее близким к изобретению ПО технической сущности является устройство для контроля интегральны схем, содержащее гён1ератор тестов, первая группа выходов которого подключена к входам коатрулируемой интегральной схемы, а Первый его вход соединен с первым выходом генератор тактовых импульсов,: многоканальный компаратор, выход которого соединен i с первым входом регистра индикации Однако устройство контроля не позволяет достаточно полно оценить потребление тока испытуемой схемы, что важно для схем, работающих от автономных источников напряжений, например, аккумуляторов. Оценка тока потребления схемы лишь по шине источника напряжения на этой схеме не дает полной оценки, так как потребление тока по выходным шинам ИС ианагруз1 и,находящиеся за пределами самой схемы, что превышает потребление тока схемой по шине питакядего напряжения Так для схемы К 145 ИК1 ток по шине напряжения не должен превышать 2 мА, а суммарный ток через выходные шины схемы, подключен-i ные к дисплею, не должен превышать 40 мА. Превышение же тока потребления автономного источника приводит к его ускоренному износу (разряду). Время работы устройства без перезарядки является основной характеристикой и вносится в технические условия на эти устройства. Превышение тока потребления, в частности, микрокалькуляторов (работающих в основном от аккумуляторов) может быть в том случае, когда выходные ключи микросхемы, нагруженные непосредственно на внешнюю нагрузку (для микрокалькулятора-дисплей), имеют слишком низкое сопротивление в открытом состоянии, что увеличивает потребляемый ток всем устройством. Известное устройство контррля осуществляет про верку выхрдов ИС по заданным порогам напряжений, а именно: во-первых величина выходного нуля не превышает порогового напряжения нуля. в6 вторых, величина выходной единицы не меньше порогового напряжения единицы. Превышение нормы тока потребления ИС по выходам означает, что сопротивление выходов ИС в открытом состоянии меньше предела по нулю. Одиако эти сопротивления (суммарно) настолько малы, что это приводит к нарушению требования ограничения по току потребления ИС, а иввестное устройство контроля ИС не сможет зафиксировать это отклонение. Кроме того, ток потребления определяется значением не одного сопротивления выходного ключа ИС в открытом состоянии, а суммариьм сопротивлением ключей ИС в открытом состоянии. Это тем {ролее важно учитывать, когда в реальньи условиях КС может не иметь ситуации, при которой все выэСоды могут « быть в открытом состоянии. Цепью изобретения является повышение надежности контроля за счет внедения контроля тока потребления выхрдных ключей интегральных схем. Поставленная цель достигается тем, что устройство контроля интегральных схем, содержащее генератор тестов, первая группа выходов которого подключена к входам интегральной схагал, а первый его вход соединен с первым выходом генератора. izaKTOBBX импульсов, многоканальный компара тор, выход которого соединен с первым входом регистра индикации, введе ны блок электронных ключей, блок нагрузок, компаратор, многоканальный генератор напряжений,.первый и второй инверторы, элемент ИЛИ, первый и второй элементы И и шина Пуск при этом, вторая группа выходов генератора тестов соедииена с первой группой входов шогоканальнрго компаратора, вторая группа входов которого соединена с первыми группами входов блока нагрузок и выходов блока электронных клк(чей, второй выход которого соединен с вторыми1-входами блока нагрузок и компаратора, пер.вый вход которого соединен с первым выходом многоканального генератора напряжений, второй выход которого соединен с третьим входом многоканального компаратора, четвертый вход которого соединен с выходом второго элетлента И, первый вход которого соединен с первым входом первого элемента И и вторым выходом генератора тактовых импульсов, первый . вход которого соединен с вторым входсм генератора тестов ишинойПуск а второй вход соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом многоканального компаратора, второй вход соединен с вторым входом регистра индикации и выходом )aTopa, а третий вход соединен с третьим выходом генератора тестОв и третьим входом регистра индикации, четвертый вход которого соединен с шиной Пуск, четвертьШ выход генератора тестов .соединен с вторым входом блока электронных ключей и входом первого инвертора, выхо которого соединен с третьим входом блока электронных ключей, пятый выход генератора тестов соединен с третьим входом компаратора, четвертый вход которого соединен с выходом первого элемента И, второй вход кото рого- соединен с шестым выходе генератора тестов и входсм второго ин-г вертора, выход которого ооединен с вторал входом второго элемента И, первая группа входов блока электронных ключей соединена с выходами интегральной схемы. При этом блок электронныхключей выполнен в виде первой.и второй груп пы электронных ключей, входы которых соединены с первой труппой входов блока электронных ключей, выходы первой группы электронных ключей соединены с вторым выходом блока электронных ключей, первая группа выходов которого соединена с выходами второй группы электронных ключей, упрсшляющие входы которых соединены с третьим входом блока электронных ключей, второй вход которого соединен с управляющими входами первой , группы элек±ронных ключей. Кроме того, генератор, тестов выполнен а виде блока ввода информации, блока памяти. Формирователя импульса и счетчика адреса, при этом первая и вторая группы выходов,а также выходы с третьего по шестой генератора тестов соединены с соотвествующими выходами блока памяти, первый вход которого соединен с первым .входом счетчика адреса и вторым входом генератора тестов, первый вход которого соединен с первым входом счетчика адреса и входом формирователя импульса, выход которого соединен с вторым входом блока памяти. Третий вход которого соединен с первым выходом блока ввода информации, второй выход которого соединен . с третьим вх.одрм счетчика адреса, выход которого соединен с четвертым входом блока памяти. На чертеже представлена структурная схема устройства. Устройство содержит генератор 1 тестов, первая группа выходов которого подключена к входам интегральной схемы 2, а первый его вход сое- . . динен с первым выходом генератора 3 тактовых импульсов, многоканальный компаратор 4, выход которого соединен с первым входом регистра 5 индикации, блок.6 электронных ключей, блок 7 нагрузок, компаратор 8, многоканальный генератор 9 напряжений, первый и второй инверторы 10 и 11, элемент 12 ИЛИ, первый .и второй элементы 13 и 14 И, шина 15Пуск , при этом вторая группа выходов генератора 1 тестов соединена с первой группой входов многоканального компаратора 4,- вторая группа входов которого соединена с первыми группами входов блока 7 и выходов блока 6, эторой выход которого соединен с.вторыми :входами блока 7 нагрузок и компаратора 8, первый вход которого соединен с первым выходом многЬканального генератора .9 , второй выход которого соединен с третьим входом многоканального компаратора 4, четвертый вход которого соединен с выводом второго элемента 14 И, первый вход которого соединен с первым вхо- . дом первого элемента 13 И и вторым выходом генератора 3, первый вход , которого соединен с вторым входом генератора 1 и шиной 15 Пуск , а второй входсоединен С выходом .элемента 12, первый вход которого соединен с выходом многоканального компаратора 4, второй вход соединен с вторым входом регистра 5, выходом компаратора 8, а третий вход соединен с третьим вБИОдом генератора 1 и третьим входом регистра 5, четвер тый вход которого соединен с шиной 15, четвертый ёыход генератора 1 соединен с вторым входом блока 6 и входом первого инвертора 10, выход которого соединен с третьим входом блока б, пятый выход генератора 1 соединен с третьим входом компаратора 8, четвертый вход которого сое динен с выходе первого эле1 1ента 13 И, второй вход которог.о соединен с шестым выходом генератора IJH входо второго инвертора 11, выход которого соединен с вторым входом второго элемента 14, аервая группа входов блока б соединен с выходами интегральной схемы 2. Блок 6 содержит первую группу электронных ключей 16, входы которы соединены с входами второй группы электронных ключей 17 и первой груп пой входов блока б, управляющие входы первой группы электронных клю чей 16 соединены с вторым входом блока б, а их выходы объединены и соединены с вторым выходом блока б. Выходы второй группы элекТгронных ключей 17 соединены с первой группой выходов блока б, а управляющие их входы соединены с третьим входом блока б. Генератор 1 тест9В содержит блок 18 ввода информации, блок .19 памя-ти формирователь 20 импульса и счетчик 21 адреса, при этом первая и вторая группы выходов, а также выходы гене ратора 1 с третьего по шестой соединены с соответствукяцими выходами .блока 19, первый вход которого соед нен с первым входом счетчика 21 и . вторым входом генератора 1, первый, вход которого соединен с первым входом счетчика 21 и входом форми- рователя 20, выход которого соедийе с вторым входом блока 19, третий вход которого соединен с первым выходом блока 18, второй выход которо го соединен с третьим входом счетчика 21, выход которого соедийен с четвертым входом блока 19, Устройство работает следующим образом. Сигналом, .поступающим с шины i5 Пуск запускается генератор 3 и приводитсяв исходное состояние генератор 1, так как счетчик 21 при(ходит в исходное состояние. В блоке 19 хранится информация, записанная из блока 18. Генератор 3 начинает вырабатывать тактовые импульсы, кото рые наращивают содержимое счетчика 21, которые поступают через формирователь 20 на блок 19, памяти. Формирователь 20 согласует временную диаграмму работы блока 19 и счетчика 21. Информация, снимаемая с блока 19, поступает на входы испытуемой интегральной схемы 2, на входы многоканального компаратора 4 (ожидаемые комбинаций), на входы блока б (управляя переключениями измерений), , а также на входы инверторов 10 и 11, элемента 13 И (управляя моментами измерений комраратором 8 и многоканальннм. ксжпаратором 4) . Распределение информации на выходе блока памяти представляется следующим образом: 1 разряд - признак окончания контроля (связь на элемент ИЛИ. 12 и на регистр 5); II разряд признак включения стробов на компаратор 8 либо на многоканальный компаратор 4 в зависимости от режима измерений выходных сигналов интегральный схемы 2 (связь на элемент 13 И и инвертор 11) гШразряд - признак переключения измерительных цепей на измерение тока потребления по всем выхода ИС 2 либо на измерение логических уровней Выходных сигналов ИС2 (связь на инвертор 10 и на группу электронных ключей 16); IV разряд признак, задающий порог (нуль I либо единица- ) на компаратор 8, при измерениях тока потребления по всем выходам НС 2 значение этого разряда равно единице;V группа разрядов - входные тесты на ИС 2(связь с входами ИС 2);VI группа разрядов ожидаемые.комбинации выходных реакций на входы многоканального компаг jDaTopa 4 . Компаратор 4 осуществляет сравнение выходных уровней с испытуемой ИС 2 (через электронные ключи 17) с порогами, задаваемыми с многоканального генератора 9 напряжений и ожидаемыми комбинациями, поступакицими с блока 19. Многоканальный компаратор 4 работает в моменты, определяемые временем.поступления стробирующих сигналов с генератора тактовых сигналов через элемент 14 И,что позволяет, кроме того, согласовать во времени сигналы,поступающие на вход Многоканального компаратора 4, Это соответствует Функционно- параметрическому контролю ИС 2. При разбраковке выходных сигналов по уровням, выходы ИС 2 подключаются через группу электронных ключей 17 к входам многоанального компаратора 4 и к эквивалентным нагрузкам в блоке 7 нагрузок. При проверке тока потребления выходт ных ключей ИС 2 в блоке, 19 изменяется значение разряда, поступающего на входы элемента 13 и инвертора 11. При этом стробирующие сигналы на многоканальный компаратор 4 прекращаютспоступать с элемента 14 И, закрытого по сигналу с инвертора 11. , Стробы на компаратор 8 начинают поступать с генератора 3 через элемент 13 И по разрешению с блока 19. Измерительные цепи переключаются варанее по сигналу с блока 19 на управля щие входы группы электронных ключей 16 и через инвертор 10- 4на управляю щие входы блока электронных ключей 6. В этом режиме измернтельйай цепь компаратора 8 нагружена йа нагрузку находящуюся в блоке 7 нагрузок, кото рая является общей для всех выходных ключей ИС 2, так как все выходы ИС 2 соединены между собой с псялсяцью группы электронных ключей 16, вклю- ченных сигналом с блока 19 ранее, чем произошло включение строба на компаратор 4, чтобы режим измерения тока потребления выходных ключей ИС 2 успед установиться после подключения нагрузки,которая представляет собой резистивную нагрузку на заданное напряжение.При зтом в много канальном компараторе 4 не произойдет ложных срабатываний, так как отключение выходов ЙС 2 не приводит к отключению нагрузок, а это обеспечивает однозначность уровней на вхог дах компаратора 4, на который ожида мые комбинации поступают в том виде (т.е.код),который соответствует обрыву. Компаратор 8 аналогичным образом не вьшаст ложных срабатываний, так как и он имеет вход ожидаемой комбинации с блока 19 памяти, а также нагрузка этой измерительной цепи не отключается при отключении группы электронных ключей 16. Значения порогов компараторов 4 и 8 задаются с многоканального генератора 9. . Выходы компаратора 8 и многоканального компаратора 4 фиксируют браки раздельно в регистре 5, который сбрасывается перед каждым конролем с шины 15 Пуск. В случае брака эти сигналы прекращают работу генератора 9 через элемент 12 ИЛИ. В случае годной ИС 2 пройдут все тесты конроля и в соответствующем разряде блока 19 памяти появится сигнал, который зафиксируется в регистре 5, и через элемент 12 ИЛИ прекратится работу устройства. Параллельное включение выходных ключей ИС 2 через группу ключей 16 осуществляется лишь в определенные , моменты, задаваемые с генератора 1 тестов, а это зн-ачит моментами вклю чения управлять можно при составлении тестов. Блок 7 нагрузок обеспечиваетпод- ключение требуемых нагрузок к входам компаратора 8 или многоканального компаратора. Перестройка с одного типа схемы на другой осуществляется с псяиощью генератора 9 напр;яжений. Таким образом, применение предлагаемого устройства позволяет выявить схеки с высоким потреблением тока по выходнЁВ ключам. При этом разбраковка таких схем производится в автоматическом режиме, совместно с функ- . циональным контролем. В конечном итоге это позволяет сократить трудоемкость сборки микрокалькуляторов за счет снижения числа потенциально ненадежных ИС,. поступаквдих на этап сборки.

| l | |||

| Устройство контроля интегральных схем | 1975 |

|

SU532830A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля интегральных схем | 1978 |

|

SU744579A1 |

Авторы

Даты

1983-10-23—Публикация

1982-04-16—Подача