pa является вторым входом блока, второй вход триггера соединен с первым входом узла контроля четности, третьим входом узла синхронизации, вторым входом шинного фор - мирователя и является третьим входом блока, входы группы шинного формирователя соединены с входами группы узла контроля четности-и регистра и являются входами группы блока, первый и второй выходы узла синхронизации и выход регистра являются соответственно четвертым, вторым и третьим выходами блока, третий вход триггера соединен с первым входом узла синхронизации и является первым входом блока, выход узла контроля четности соединен с вторым входом узла синхронизации и является первым выходом блока, входы-выходы группы узла контроля четности являются входами-выходами первой группы блока, выход триггера соединен с первым входом шинного формирователя, третьим входом синхронизации и первым входом регистра, второй вход которого соединен с пятьм входом узла синхронизации и является; четвертым входом блока.

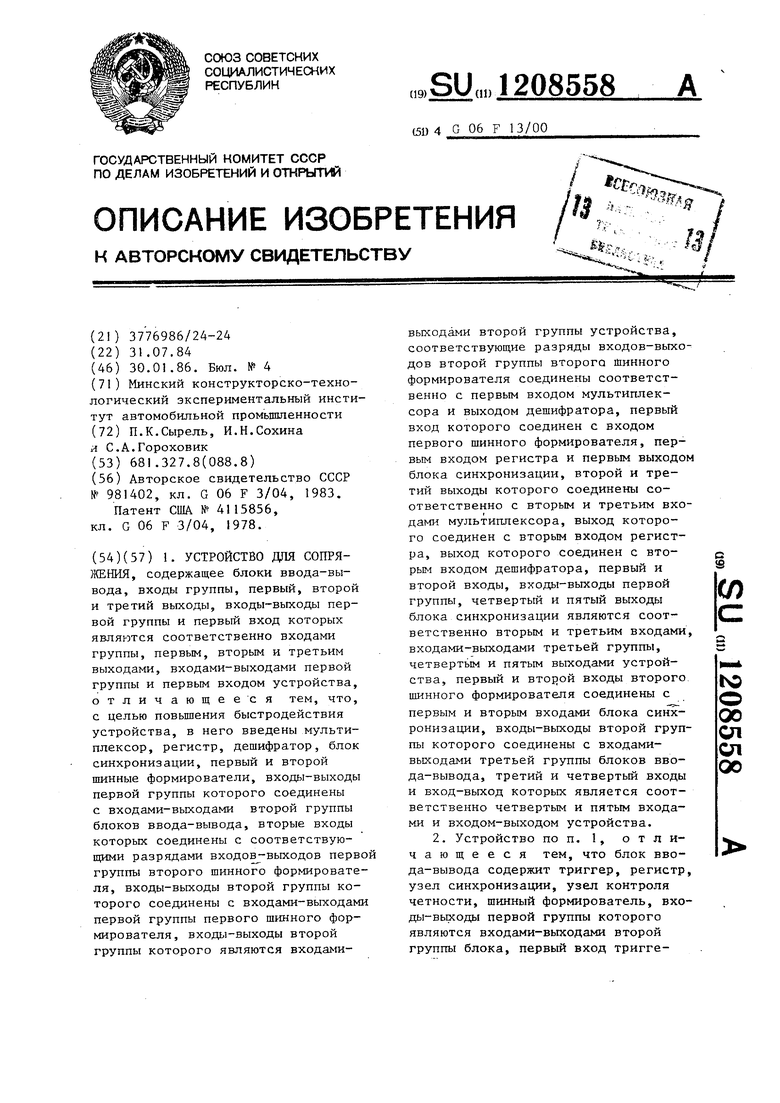

3. Устройство по п. 1, отличающееся, тем, что блок синхронизации содержит первый и второй триггеры, элемент задержки, первый и второй одновибраторы первый и второй элементы ИЛИ, шинный формирователь, первый, второй, третий, четвертый и пятый элементы И, первые входы четвертого и пятого элементов И являются первым входом блока, второй вход четвертого элемента .И является вторым входом блока, первьш и второй входы второго элемента ИЛИ являются соответственно четвертым и пятым входами бло208538

ка, третий вход первого триггера соединен с третьим входом первого элемента И и вместе с входами-выходами первой группы шинного формирователя являются входами-выходами второй группы блока, первый вход первого одновибратора, выходы первого элемента И и входы-выходы второй группы шинного формирователя являются входами-выходами первой группы блока, выход четвертого элемента И соединен с вторым входом первого элемента И, вторым входом второго триггера,. третьим вхо- . дом первого триггера, вторым входом первого одновибратора и первым входом второго одновибратора, первый выход которого соединен с первым входом второго триггера, выход которого соединен с первыми входами первого элемента ИЛИ, первого и третьего элементов И и является третьим выходом блока, первый выход первого триггера соединен с входом элемента задержки, выход которого соединен с вторым входом второго одновибратора, второй выход которого соединен с вторым входом третьего элемента И, выход которого является пятым выходом блока, первый выход первого одновибратора соединен с первым входом первого триггера, второй выход которого соединен с вторыми входами второго элемента И к первого элемента ИЛИ и является вторым выходом блока, второй выход первого одновибратора соединен с первым входом второго элемента И, выход которого является четвертым выходом блока, выход первого элемента ИЛИ является первым выходом блока, выход второго элемента ИЛИ соединен с вторьм входом пятого элемента И, выход которого соединен с входом шинного формирователя.

Изобретение относится к области вычислительной техники, предназначено для управления обменом информации в вычислительной системе иможет быть использовано для сопряжения в системах управления технологическими процессами, автоматическими линиями, робото-техническими комплексами.

Целью изобретения является повы- тел ме быстродействия устройства.

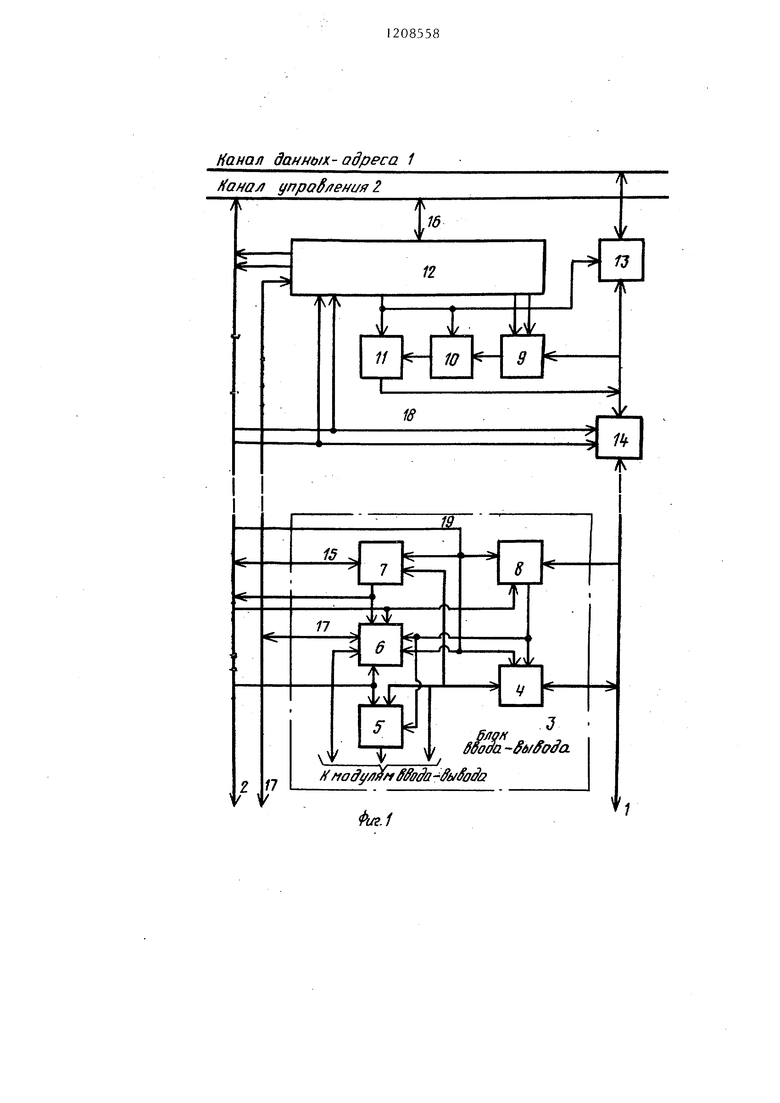

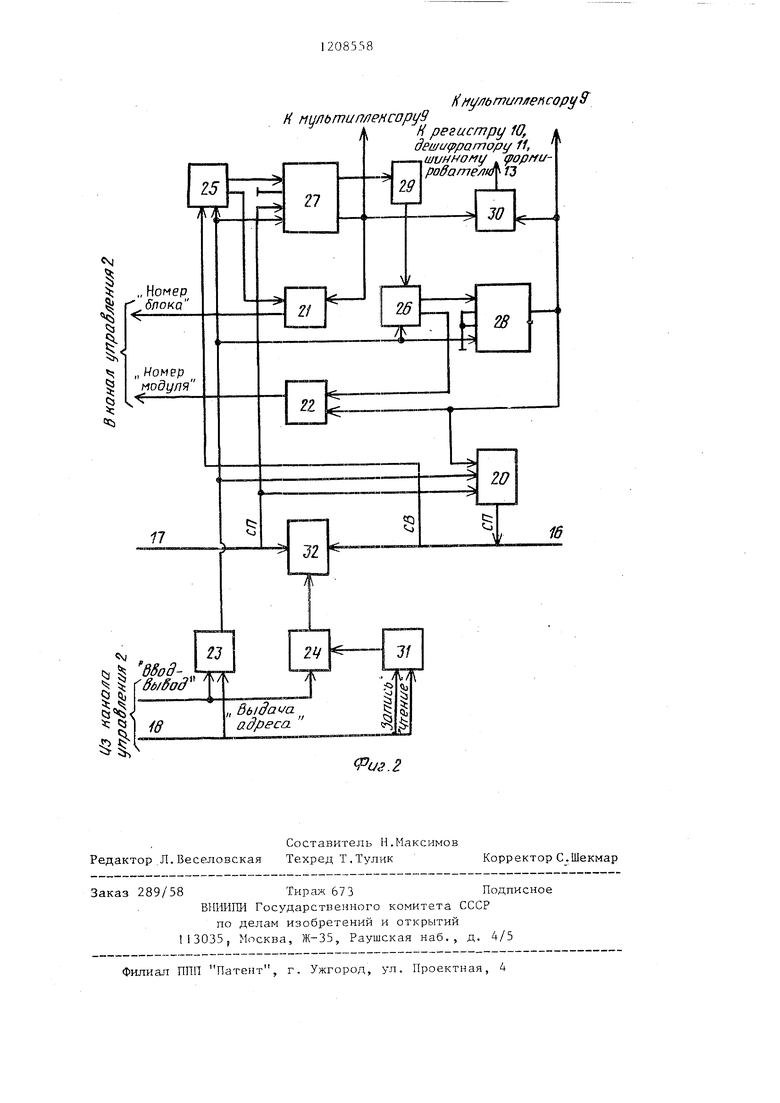

На фиг. представлена структурная схема устройства; на фиг. 2 - структурная схема блока синхронизации.

Устройство для сопряжения содержит входы-выходы 1 адреса-данных входы-выходы 2 управления, блоки 3 ввода-вывода, состоящие из шинного формирователя 4, регистра 5, узла 6 синхронизации, узла 7 контроля четности, триггера 8, мультиплексор 9, регистр 10, дешифратор 11, блок 12 синхронизации, первый 13 и второй 14 шинные формирователи входы и выходы 15-19 блоков. Блок 12 синхронизации содержит первый - пятый элементы И 20-24, первый 25 и второй 26 одновибраторы, первый 27 и второй 28 триггеры, элемент 29 задержки, первый 30 и второй 31 элементы ИЛИ, шинный формирователь 32.

Устройство для сопряжения работает следующим образом.

Обмен информацией между управляющими процессором (не показан) и блоками 3 ввода-вывода осуществляется в асинхронном режиме. Цикл обмена информацией начинается с выдави адреса.

Процессор вьадает сигнал Выдача адреса и сигнал Ввод-вывод, указывающий на то, что происходит обмен информацией между про ;ессором и блоками 3 ввода-вывода, а на входы-выходы I (данных-адреса) - адресное слово, которое через второй . шинный формирователь 13 поступает на вход мультиплексора: 9.

Сигнал Выдача адреса поступает на вход элемента 23 И блока 12, на второй его вход подается сигнал Ввод-вывод. Выходной сигнал этого элемента снимает блокировку элемента 20 И, одновибраторов 25 и 26, и триггеров 27 и 28. Запуск одновиб ратора 25 осуществляется сигналом Синхронизация выдачи, который сопровозкдает адресное слово, выдаваемое процессором.

На выходе одновибратора 25 появляется импульс, который своим передним фронтом устанавливает триггер 27 в состояние 1. Сигнал с прямого выхода триггера 27 поступает ка входы элемента 30 ИЛИ, элемента 21 и на вход мультиплексора 9 на третьем входе которого уже присутствует адресное слово. По сигналу Номер бпока мультиплек08558

сор 9 выбирает из адресного слова с 6-го по 9-й разряды, указывающие номер выбираемого блока 3. Запись выбранной информации в регистр г 10 производится сигналом, поступающим с выхода элемента 30 ИЛИ, Этот же сигнал подается на вход шшч ного формирователя 13, который переводится в нейтральное высо10 коимпедансное состояние, деблокируя тем самым входы-выходы 1 (данных- адреса) , и на вход дешифратора 11, разрешая дешифрацию информации, записанной в регистре 10, С выхода

15 дешифратора 1 1 сигнал, несуш й информацию о номере выбранного блока 3, через шинный фсрмирователь 14 поступает на выбранный блок 3 ввода-вывода. Блоки 3 ввода-вывода подJ ключаются таким образом, что каждый блок 3, имеющий определенный номер от О до 15 подключен к соответствующим входам-выходам, имеющим такой же номер. Этот сигнал

25 заведен на вход триггера 15, а на

другой его вход поступает сигнал Номер блока с входов-выходов 2 (управления), на которые этот сигнал поступает с выхода элемента 21 И, причем задержка его относительно сигнала, поступившего на вход триггера 15, несущего информацию о номере блока, определяется длительностью блокирующего импульса, поступающего на вход элемента

35 21 с выхода одновибратора 25.

Таким образом, наличие в триггере I5 подключения этих двух сигналов производит его установку в состояние 1, а сигнал на его выхо40 да выводит шинный формирователь из отключенного состояния, давая тем самым разрешение на обмен информацией между процессором и выбранным блоком 3 ввода-вывода.

5 Далее сигнал с выхода триггера 15 подключения попадает на вход узла 6 синхронизации, снимая с него блокировку. На другом входе узла 6 синхронизации присутствует сигнал

50 Номер блока из входов-выходов 2 (управления). На выходе узла 6 формируется сигнал Синхронизации приема, указывающий на то, что выбранный блок подключен. Триггер

55 27 переходит в исходное состояние. При этом снимается блокировка с шинного формирователя 13, адресное слово поступает на вход мультиплек30

сора 9, блокируется элемент 21 И, снимается сигнал Номер блока, а следовательно, и сигнал Синхро- - низация приема. Выбор блока осуществлен.

Сигнал с выхода триггера 27 через элемент 29 задержки, запускает одновибратор 26, импульс на выходе которого своим передним фронтом устанавливает триггер 28 в единич- ;ное состояние. Далее сигнал с выхода триггера 28 поступает на входы элементов 30 ИЛИ, 22 И, 20 И и на вход мультиплексора 9, который выбирает из адресного слова с 3-го по 5-й разряды, указывающие номер выбираемого модуля. В регистре 10 запись выбранной информации производится сигналом, поступающим с элемента 30 ИЛИ.

Как и в цикле выбора номера блока этот сигнал блокирует шинный формирователь 13 и разрешает дешифрацию информации, записанной в регистре Ю, С лыхода дешифратора 11 через шинный формирователь 14 сигнал с дешифрованным номером модуля поступает в выбранный блок 3 ввода-вьгаода на шинный формирователь 4. Далее сигнал поступает на вход регистра 5, на другом входе которого присутствует уже сигнал Номер модуля с выхода элемента 22 И. Причем задержка сигнала Номер модуля, поступившего на вход регистра 5, относительно сигнал на его другом входе определяется длительностью блокирующего импульса, поступающего на вход элемента 22 И с выхода одновибратора 26. Одновре- м€;нно этот же сигнал Номер модуля поступает и на вход узла 6 синхронизации. На выходе узла 6 формируется

0

5

0

5

сигнал Синхронизация приема, указывающий на то, что модуль выбран. Этот сигнал подается в блок 12 на вход элемента 20 И, который вьщает сигнал Синхронизация приема, из-, вещающий процессор о том, что выдача адреса закончена. Процессор снимает адресное слово и сигналы Выдача адреса и Синхронизация выдачи. Снятие сигнала Выдача адреса блокирует одновибраторы 25 и 26, триггеры 27 и 28 и элемент 20 И. При этом снимается сигнал Номер модуля Синхронизация приема и блокируется шинный формирователь 13. ,

После окончания цикла вьщачи адреса следует цикл записи ин- формации-в выбранный модуль или цикл чтения информации из выбранного модуля.

в цикле записи информация .сопровождается разрядом контроля по паритету, выдаваемым процессором. Через шинный формирователь 4 информация поступает на вход узла 7 контроля на четность, проверяется на четность, сравнивается с контроль. ным разрядом и в случае несовпадет НИН узел 7 вьщает сигнал Сбой, который блокирует узел 6 синхронизации .

В цикле чтения информация, выдаваемая выбранным модулем процессору, дополняется узлом 7 контрольным паритетным разрядом.

Таким образом, предлагаемое изобретение обеспечивает значительное повьш1ение быстродействия за счет того, что шина данных-адреса всегда находится под постояннорг нагрузкой только одного выбранного блока ввода-вывода.

Наиал данных.-адреса 1

Нана/1 ynpod/feHL/ff 2

15

17

f

/7

)/

/ffiody/ fiffffo a- i / o a Фиг.1

1

12

/J

I

fff

гЦТ

У J

Влон , - Soooa -ffA/ffffffa

l{ М(//)ьтип/гепсору 3 И пильтипленсоруЭ

Н регистру 10, , дешид ратору 11,

ujvHHOfiy ipopfiu- ровате/гю /J

«М

регистру 10, шид ратору 11,

ujvHHOfiy ipopfiu- ровате/гю /J

(Риг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для управления обменом информацией между управляющим процессором и внешним устройством | 1988 |

|

SU1594552A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для сопряжения датчиков с ЭВМ | 1985 |

|

SU1282108A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для управления обменом информацией | 1990 |

|

SU1783525A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для сопряжения датчиков с электронной вычислительной машиной | 1984 |

|

SU1208557A2 |

Составитель Н.Максимов Редактор,Л.Веселовская Техред Т.ТуликКорректор С.Шекмар

Заказ 289/58Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

| Способ нагрева крупных деталей с осевым отверстием | 1980 |

|

SU981402A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4115856, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-30—Публикация

1984-07-31—Подача