12

дом Установка исходного состояния устройства,

2, Устройство по п. 1, о т л и - чающееся тем, что блок управления содержит два триггера, пять элементов ИЛИ, тринадцать элементов И, три элемента НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, подключенный выходом к первому входу первого элемента И, первы входом к первому управляющему входу блока управления, к первому входу второго элемента ИЛИ, к первым входам второго, третьего-И четвертого элементов И, а вторым входом - к второму управляющему входу блока управления, к второму входу второго элемента ИЛИ, к первым входам пятого и шестого элементов И и через первый элемент .НЕ к первому входу третьего элемента ИЛИ, соединенного выходом с первым входом седьмого элемента И, а вторым входом - с третьим управ ляющим входом блока управления и через второй элемент НЕ с первым входом восьмого элемента И, подключен- ного вторым входом через третий эле мент НЕ к пятому управляющему входу блока управления и к второму входу шестого элемента И, а выходом - к первому входу четвертого элемента ИЛИ и к второму входу второго элемента И, а выходом - к первому входу пятого элемента ИЛИ, связанного вторым входом с выходом пятого Элемента И, а выходом - с первым входом девятого элемента И, подключенного выходом к второму информационному выходу блока управления, а вторым входом - к выходу десятого элемента И и к первому входу одиннадцатого эле- мента И, связанного вькодом с пятым информационным выходом блока управления, а вторым входом - с вькодом четвертого элемента ИЛИ, подключенного вторым входом к выходу четвертого

Изобретение относится к технике автоматизированного управления производственными процессами, а именно к устройствам для использования в системах числового программного

695

элемента И, соединенного вторым входом с прямым выходом первого триггера, с вторым входом пятого элемента И и с вторым входом седьмого элемента И, подключенного вькодом к первому входу шестого элемента ИЛИ, соединенного вторым входом с седьмым управ- лякяцим входом блока управления, а вькодом - с нулевым входом второго триггера, подключенного eдинич ым входом к шестому.управляющему входу блока управления, инверсным выходом к нулевому входу первого триггера, а прямьм выходом - к первому входу десятого элемента И и к первому входу двенадцатого элемента И, связанного вторым входом с первым информационным входом блока управления, а вькодом - с третьим информационным клходом блока управления и с третьим входом шестого элемента И, подключенного вькодом к шестому информационному выходу блока управления, а четвертым входом - к первому управляющему/ выходу блока управления, к второму входу третьего элемента ИЛИ и к инверсному входу первого триггера, соединенного единичным входом с четвертым управляющим входом блока управления, причем второй информационный вход блока управления подключен к второму входу десятого .эле- мента И, второй управлякнций выход блока управления - к выходу третьего элемента И, первый и четвертый информационные выходы блока управления - к вькодам соответственно первого и тринадцатого элементов И, а третий информационный вход блока управления - к второму входу первого элемента И и к первому входу тринадцатого элемента И, соединенного вторьпу входом с выходом второго элемента ИЛИ..

управления станками, является частью цифрового интерполятора, и предназначено для преобразования кода скорости подачи в частоту импульсов в различных режимах работы интерполятора.

3

Цель изобретения - повьшение точности устройства за счет определения момента начала торможения.

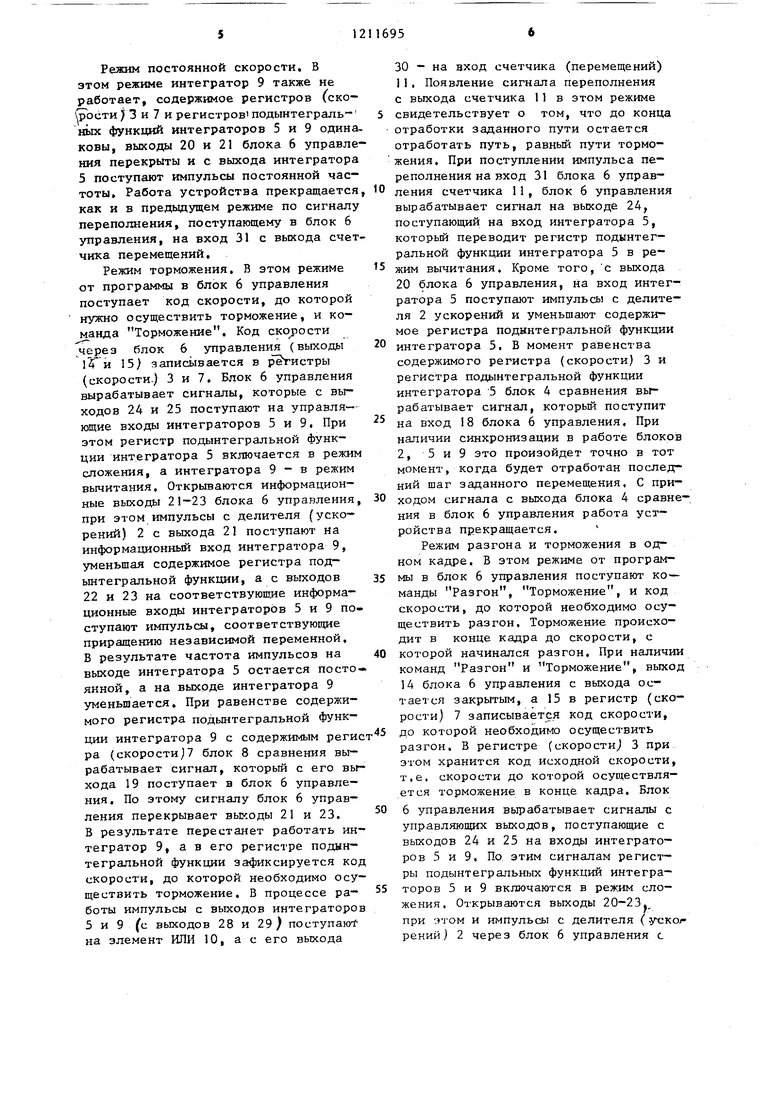

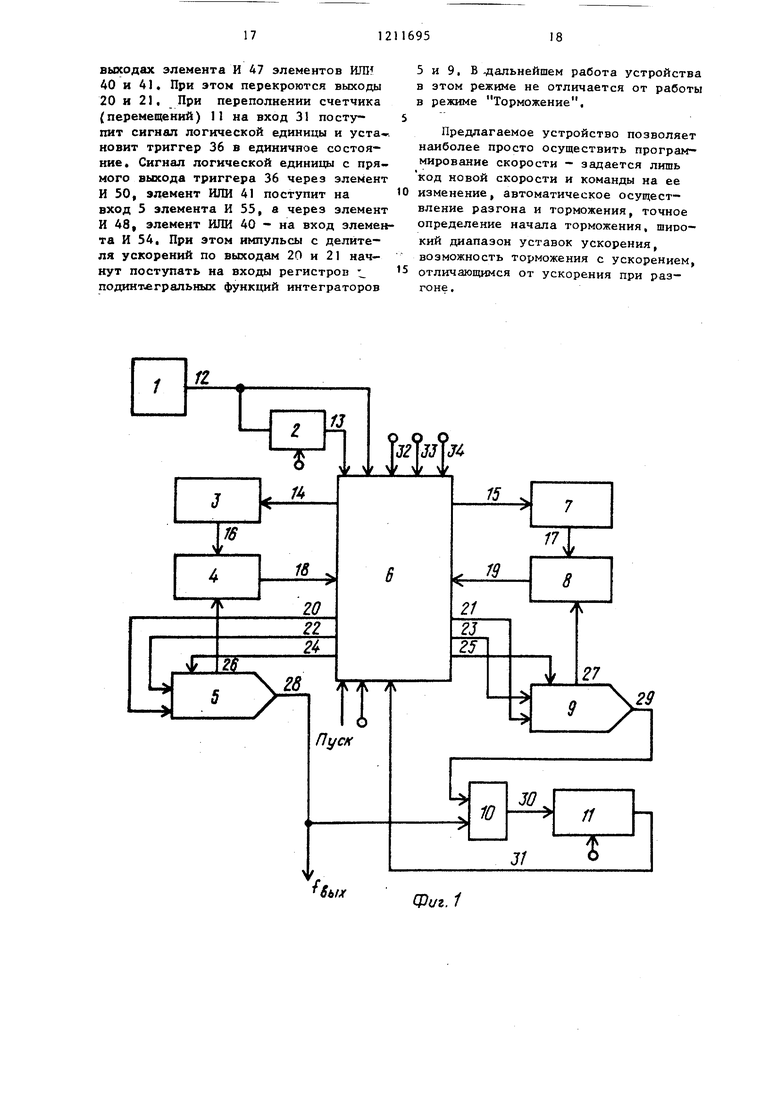

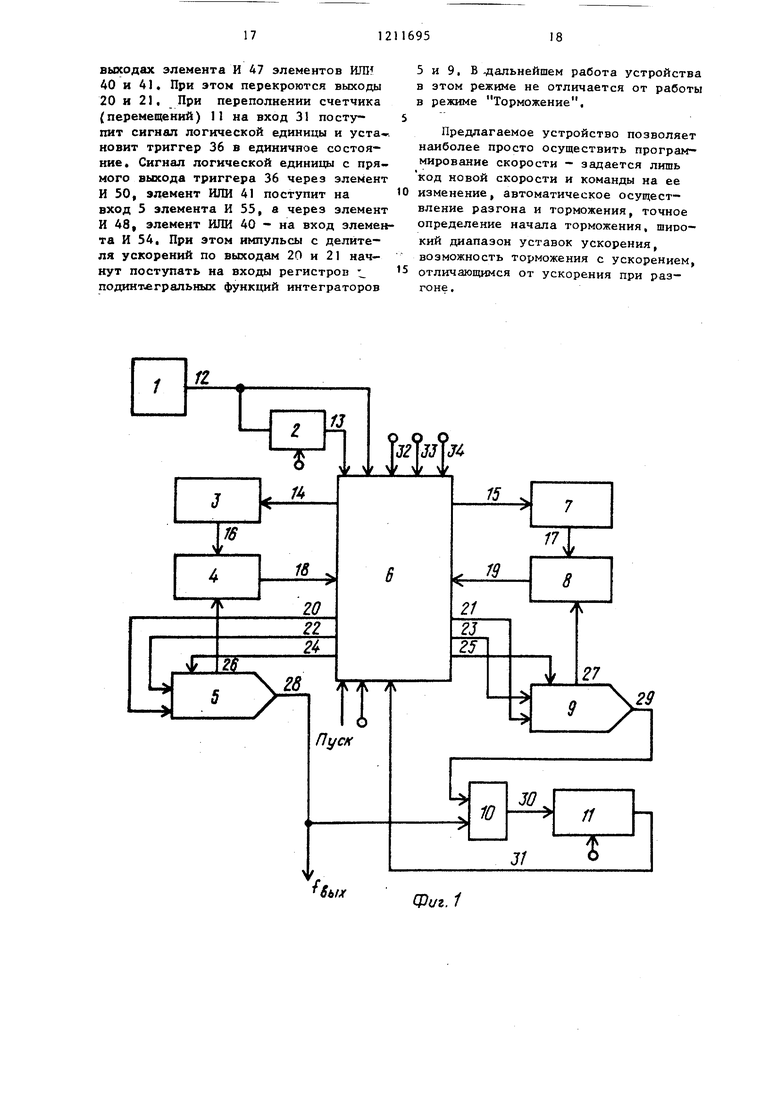

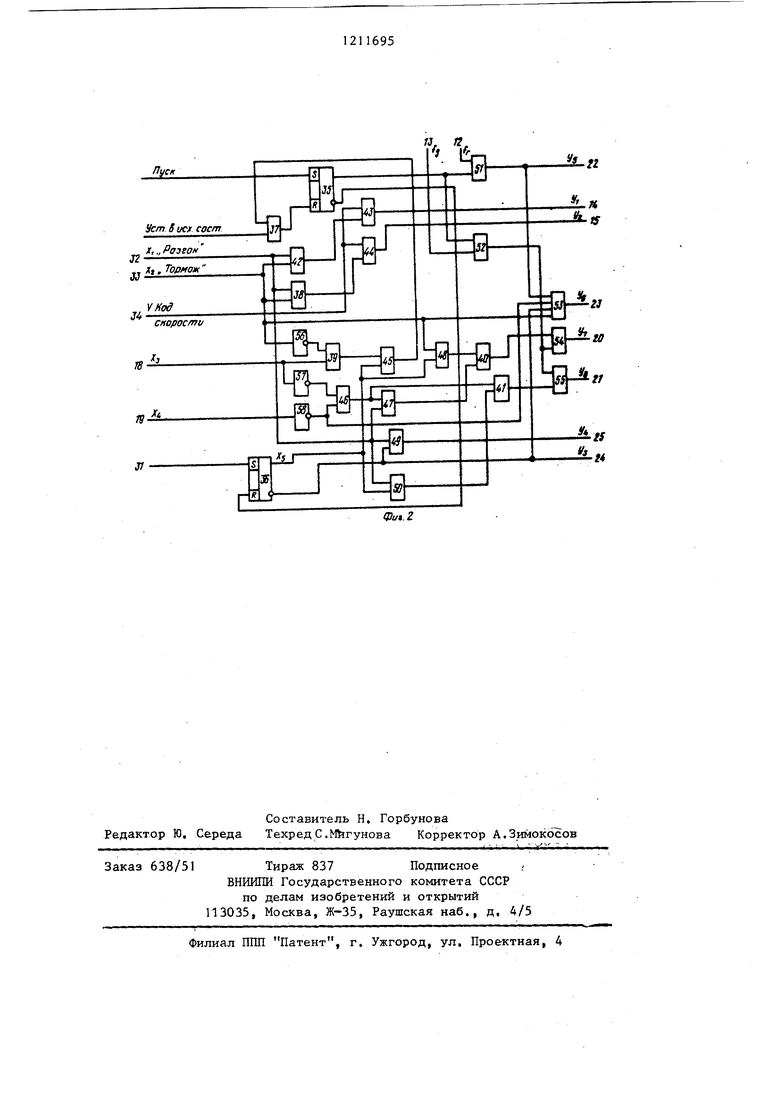

На фиг. 1 представлена блок-схема устройства; на фиг, 2 - функциональная схема блока управления.

Устройство содержит генератор I, импульсов, управляемый делитель 2 частоты, первьй регистр 3, первый блок 4 сравнения, первый интегратор 5, блок 6 управления, второй регистр 7, второй блок 8 сравнения, второй интегратор 9, элемент ИЛИ 10 счетчик 11 импульсов. Первый и второй информационные входы 12 и 13. первый и четвертый информационные выходы 14 и 15 блока управления, выход 16 первого регистра, выход 17 второго регистра, третий и пя- тьй управляющие входы 18 и 19, второй, пятый, третий, шестой, инЛор- мационные выходы 20-23, блока управления, первый и второй управляющие выходы 24 и 25 блока управления, первые информационные выходы 26 и 27 и вторые информационные выходы 28 и 29 соответственно первого и второго интеграторов, выход 30 второго элемента ИЛИ, четвертый управляющий вход 31 блока управления, первьй и второй управляющие входы 32 и 33 блока управления, третий информационньм вход 34 блока управления.

Блок 6 управления содержит второй и первый триггеры 35 и 36, шестой, второй, третий, пятый, четвертый элементы ИЛИ 37-41, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 42, первый, тринадцатый, седьмой, .восьмой, второй, пятый, третий, четвертый, двенадцатый, десятый, шестой, девятый и одиннадца- тьй элементы И 43-55, первый, второй и третий элементы НЕ 56-58, выход 20 соединяет соответствующий выход приращения подынтегральной функции блока 6 управления с входом приращения подынтегральной функции цифрового интегратора 5, Выход 21 соединяет соответствующий выход приращения подынтегральной функции блока 6 управления с входом приращения подын- тегральной функции цифрового ратора 9, а выход 22.соединяет соответствующий выход приращения незави- СИМОЙ переменной блока 6 управления с входом приращения независимой переменной цифрового интегратора 5, вы1695

ход 23 соединяет соответствующий выход приращения независимой переменной блока 6 управления с входом приращения независимой переменной второ5 го цифрового интегратора 9,

Устройство работает следующим образом,

Режим разгона, В этом режиме код предыдущей скорости хранится в регистf pax подынтегральных функций (не показано) интеграторов 5 и 9, а код скорости, до которой нужно осуществить разгон, через блок 6 управления, с выходов 14 и 15 поступает в регистры

5 (скорости) 3 и 7. По команде Разгон блок 6 управления вырабатывает сигнал, который с Выходов 24 и 25 поступает в интеграторы 5 и 9 и переводит регистры подынтегральных функций в

0 режим сложения, С выходов 20 и 21 в интеграторы 5 и 9 поступают импульсы с частотой, определяемой установкой ускорения. При этом величина кода подынтегральных функций интеграторов

5 5 и 9 будет возрастать, В этом режиме выход 23 перекрыт и импульсы при- ращения независимой переменной с генератора 1 импульсов через блок 6 управления (выход 22) поступают только

0 на вход интегратора 5, а интегратор.

9 не работает. Поскольку увеличивает- ся содержимое регистров подынтегральных функций интеграторов, то частота импульсов, поступающих с выхода 28

5 интегратора 5, будет также возрастать, В момент совпадения кодов в регистре подынтегральной функции интегратора

;5 и в регистре (скоростиЗ 3 блок А 1. ..

сравнения вьфабатывает сигнал, кото0 рый поступит на вход 18 в блок 6 управления. По этому сигналу блок 6 управления перекроет выходы 20 и 21, ив регистрах подынтегральных функций интеграторов 5 и 9 зафикси-

5 руется код конечной скорости, а частота на выходе интегратора 5 перестанет изменяться. Импульсы с выхода интегратора 5 поступают через элемент ИЛИ 10 на счетный вход счетчика

0 11 импульсов ( перемещений), который включен на вычитание. Появление импульса переполнения на выходе счетчика 11 свидетельствует в этом режиме об отработке заданного пути. Импульс

5 переполнения с выхода счетчика 11 поступает на вход 31 блока 6 управления и работа устройства прекращается ,

Режим постоянной скорости, В этом режиме интегратор 9 также не работает, содержимое регистров (ско- ости) 3 и 7 и регистров подынтеграль- ных функций интеграторов 5 и 9 одинаковы, выходы 20 и 21 блока 6 управления перекрыты и с выхода интегратора 5 поступают импульсы постоянной частоты. Работа устройства прекращается как и в предыдущем режиме по сигналу переполнения, поступающему в блок 6 управления, на вход 31 с выхода счетчика перемещений.

Режим торможения, В этом режиме от программы в блок 6 управления поступает код скорости, до которой нужно осуществить торможение, и команда Торможение, Код скорости через блок 6 управления (выходы 1 и 15) запись1вается в р истры (скорости.) 3 и 7, Блок 6 управления вырабатывает сигналы, которые с выходов 24 и 25 поступают на управля- ющие входы интеграторов 5 и 9, При этом регистр подынтегральной функции интегратора 5 включается в режим сложения, а интегратора 9 - в режим вычитания. Открываются информационные выходы 21-23 блока 6 управления, при этом импульсы с делителя (ускорений) 2 с выхода 21 поступают на информационный вход интегратора 9, уменьшая содержимое регистра под- ьштегральной функции, ас выходов 22 и 23 на соответствующие информационные входы интеграторов 5 и 9 поступают импульсы, соответствующие приращению независимой переменной, В результате частота импульсов на выходе интегратора 5 остается постоянной, а на выходе интегратора 9 уменьшается. При равенстве содержимого регистра подынтегральной функции интегратора 9 с содержимым регис ра (скорости 7 блок 8 сравнения вырабатывает сигнал, который с его выхода 19 поступает в блок 6 управления. По этому сигналу блок 6 управления перекрывает выходы 21 и 23, В результате перестанет работать интегратор 9, а в его регистре подынтегральной функции зафиксируется код скорости, до которой необходимо осуществить торможение, В процессе работы импульсы с выходов интеграторов 5 и 9 fc выходов 28 и 29) поступают на элемент Ш1И 10, ас его выхода

15

20

25

5 10

30

5

0

5

0

5

30 - на вход счетчика (перемещений) I1, Появление сигнала переполнения с выхода счетчика 11 в этом режиме свидетельствует о том, что до конца отработки заданного пути остается отработать путь, равный пути тормо- жения. При поступлении импульса переполнения на вход 31 блока 6 управления счетчика 11, блок 6 управления вырабатывает сигнал на выходе 24, поступающий на вход интегратора 5, который переводит регистр подынтегральной функции интегратора 5 в режим вычитания. Кроме того, с выхода 20 блока 6 управления, на вход интегратора 5 поступают импульсы с делителя 2 ускорений и уменьщают содержимое регистра подынтегральной функции интегратора 5, В момент равенства содержимого регистра (скорости) 3 и регистра подынтегральной функции интегратора 5 блок 4 сравнения вырабатывает сигнал, который поступит на вход 18 блока 6 управления. При наличии синхронизации в работе блоков 2, 5 и 9 это произойдет точно в тот момент, когда будет отработан последний шаг заданного перемещения, С приходом сигнала с выхода блока 4 сравнения в блок 6 управления работа устройства прекращается,

Режим разгона и торможения в одном кадре, В этом режиме от программы в блок 6 управления поступают команды Разгон, Торможение, и код скорости, до которой необходимо осуществить разгон. Торможение происходит в конце кадра до скорости, с которой начинался разгон. При наличии команд Разгон и Торможение, выход 14 блока 6 управления с выхода остается закрытым, а 15 в регистр (скорости) 7 записывается код скорости, до которой необходимо осуществить разгон, В регистре (скоростиj 3 при этом хранится код исходной скорости, т.е. скорости до которой осуществляется торможение в конце кадра. Блок

6 управления вырабатывает сигналы с управляющих выходов, поступающие с выходов 24 и 25 на входы интеграторов 5 и 9, По этим сигналам регистры подынтегральных функций интеграторов 5 и 9 включаются в режим сложения. Открываются выходы 20-23. при этом и импульсы с делителя (уско/- рений) 2 через блок 6 управления с

выходов 20 и 21 поступают на информационные входы интеграторов 5 и 9, увеличивая сод ержимое их регистров подынтегральных функций, с выходов 22 и 23 на соответствующие информационные входы интеграторов поступают с генератора 1 импульсы, соответствующие приращению независимой переменной, В результате частота импульсов на выходах интеграторов увеличивается ,

При равенстве содержимого регистра 7 и регистра подынтегральной фун№ ции интегратора 9 блок 8 сравнения вырабатывает сигнал, которьш с выхода 19 поступит в блок 6 управления. По этому сигналу блок управления перекроет выходы 20, 21 и 23, перестанет работать интегратор 9 и в регистрах подынтегральной функции интеграторов 5 и 9 зафиксируется код

скорости, до которой необходимо было Осуществить разгон,

В дальнейшем работа- устройства не отличается от работы в режиме торможения, В этом режиме путь, необходимый для торможения, принимается равным пути разгона, а переполнение.

счетчика 11 происходит в тот момент, когда до конца отработки заданного пути остается отработать путь, равный пути разгона.

Этот режим используется при переходах от рабочего хода к холостому и обратно, а также при выполнении разгона от нуля до некоторой скорости в начале кадра и торможения до нуля в конце,

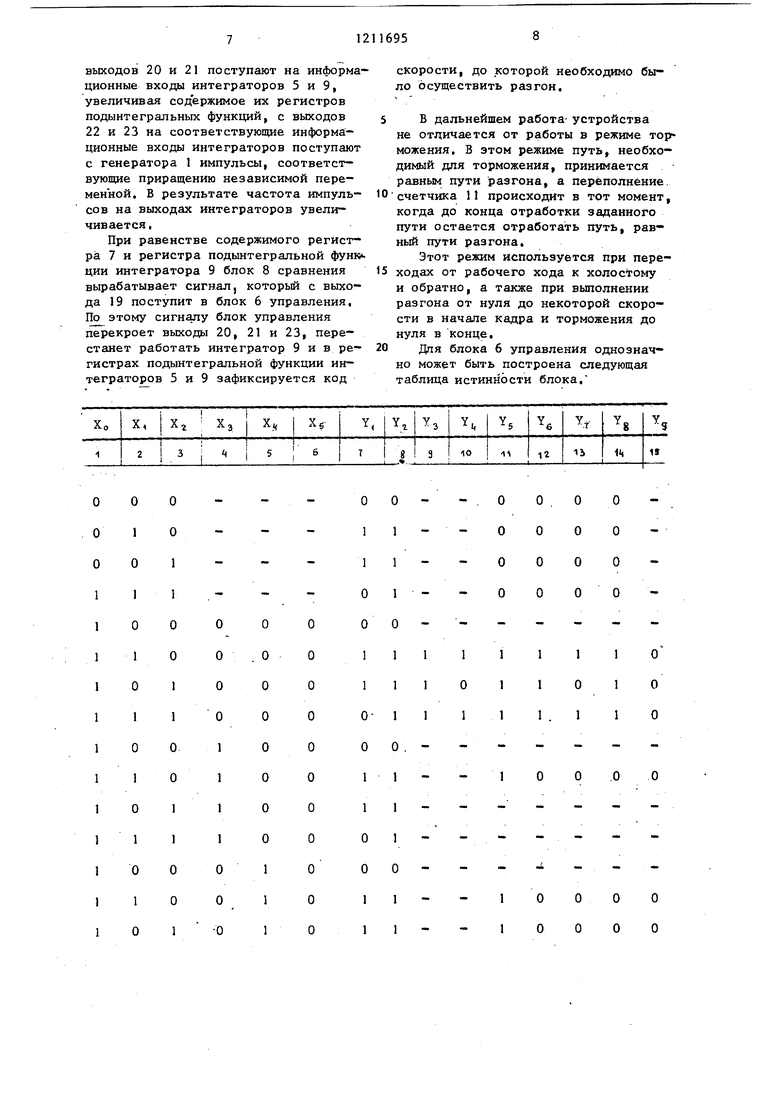

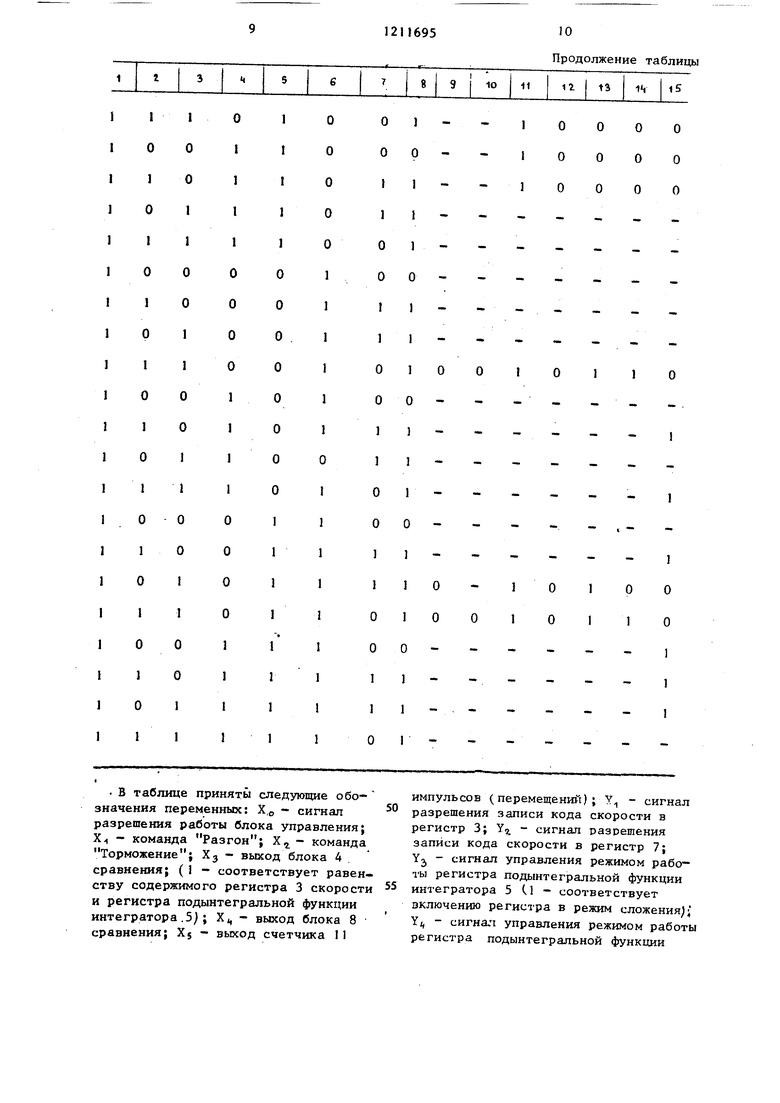

Для блока 6 управления однозначо может быть построена следующая аблица истинности блока,

. В таблице приняты следующие обозначения переменных: Х.о - сигнал разрешения работы блока управления; Х - команда Разгон ; Х - команда Торможение } Х - выход блока 4 сравнения; (1 - соответствует равенству содержимого регистра 3 скорости и регистра подынтегральной функции интегратора .5); Xj, - выход блока 8 сравнения; Xs выход счетчика 11

Продолжение таблицы

импульсов (перемещений); У - сигнал разрешения записи кода скорости в регистр 3; У - сигнал разрешения записи кода скорости в регистр 7; У - сигнал управления режимом работы регистра подынтегральной функции интегратора 5 (,1 - соответствует включению регистра в режим сложения ; У;, - сигна. управления режимом работы регистра подынтегральной функции

интегратора 9; 5 - разрешение приращения независимой переменной в ин тегратор 5; Yg - разрешение прираще кия независимой переменной в интегра- тор 9; Y - разрешение изменения содержимого регистра подынтегральной функции интегратора 5; Yg - разрешение изменения содержимого регистра подынтегральной функции интегратора 9} Yg - конец отработки кадра управ- лякицей программы.

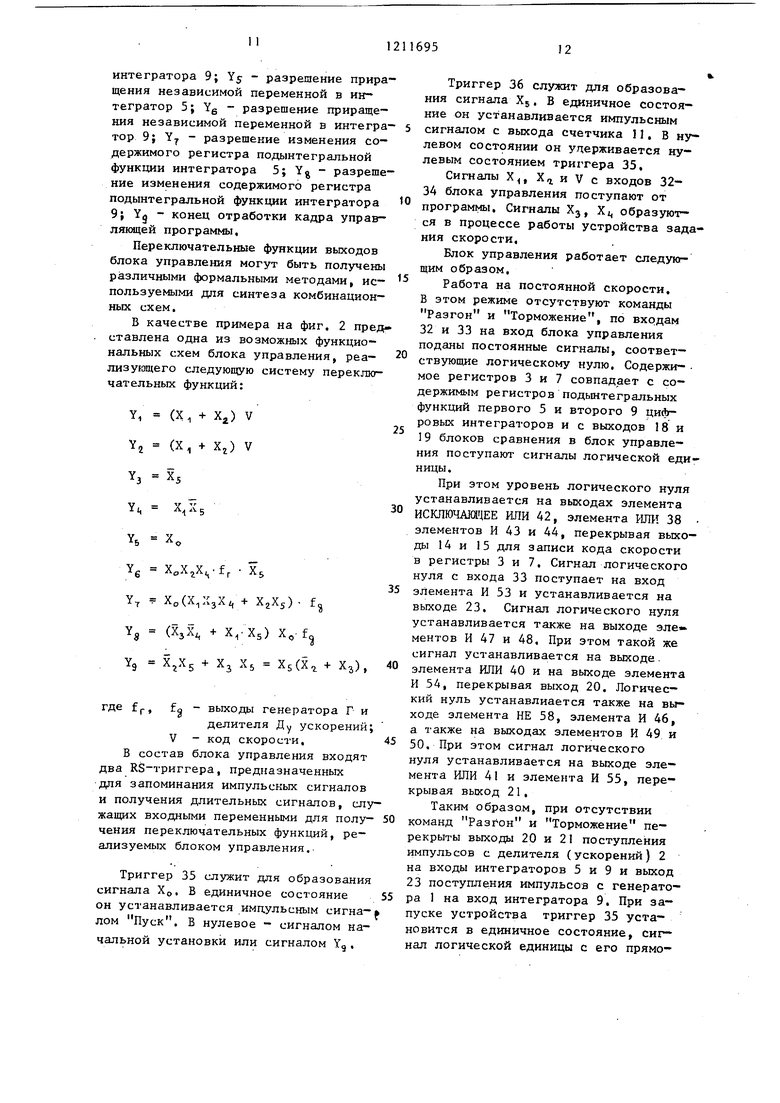

Переключательные функции выходов блока управления могут быть получены различными формальными методами, используемыми для синтеза комбинационных схем.

Б качестве примера на фиг. 2 представлена одна из возможных функциональных схем блока управления, pea- лизующего следующую систему переклю чательных функций:

-

-

25

30

(X, + X) V (X, + Xj) V Хз

Xr ТГ

A л 5

Xo

XoXjX If X

Х(,(, + X2X5) f

(XjX + Х. Хз)

+ Хз Xs XsCX + Xj), 40

35

где fp, fg выходы генератора Г и делителя Ду ускорений; V - код скорости. В состав блока управления входят два К8 триггера, предназначенных дпя запоминания импульсных сигналов и получения длительных сигналов, служащих входными переменными для полу- чения переключательных функций, реализуемых блоком управления.

Триггер 35 служит для образования сигнала XQ. В единичное состояние он устанавливается имдульсным сигналом Пуск. В нулевое - сигналом начальной установки или сигналом Yg.

0

5

5

5

0

0

5

5 0

5

Триггер 36 служит для образования сигнала Xj. В единичное состояние он устанавливается импульсным сигналом с выхода счетчика II, В ну левом состоянии он удерживается нулевым состоянием триггера 35,

Сигналы Х, Хг и V с входов 32- 34 блока управления поступают от программы. Сигналы Xj, Х/, образуются в процессе работы устройства задания скорости.

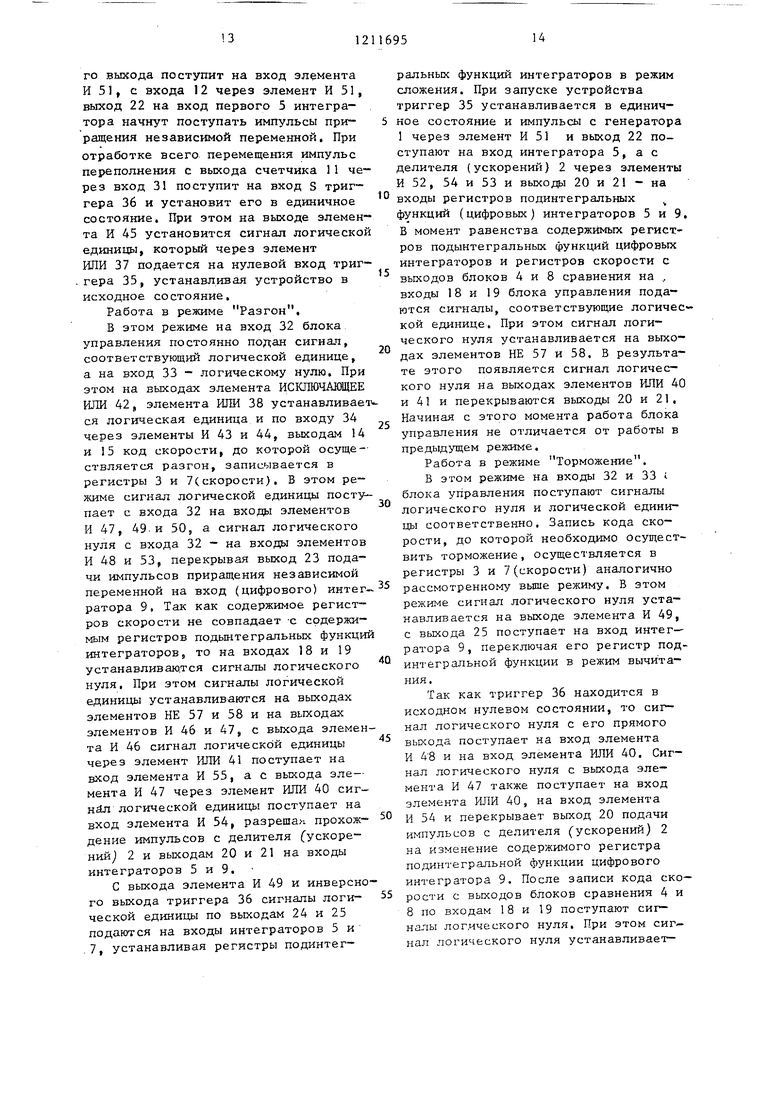

Блок управления работает следующим образом.

Работа на постоянной скорости. В этом режиме отсутствуют команды Разгон и Торможение, по входам 32 и 33 на вход блока управления поданы постоянные сигналы, соответствующие логическому нулю. Содержи- мое регистров 3 и 7 совпадает с содержимым регистров подынтегральных функций первого 5 и второго 9 циф ровых интеграторов и с выходов 18 и 19 блоков сравнения в блок управления поступают сигналы логической единицы.

При зтом уровень логического нуля устанавливается на выходах элемента ИСКЛЮЧАМЦЕЕ ИЛИ 42, элемента РШИ 38 элементов И 43 и 44, перекрывая выходы 14 и 15 для записи кода скорости в регистры 3 и 7, Сигнал логического нуля с входа 33 поступает на вход элемента И 53 и устанавливается на выходе 23. Сигнал логического нуля устанавливается также на выходе эле-- ментов И 47 и 48. При этом такой же сигнал устанавливается на выходе. элемента ИЛИ 40 и на выходе элемента И 54, перекрывая выход 20. Логический нуль устанавлиается также на выходе элемента НЕ 58, элемента И 46, а также на выходах элементов И 49 и 50, При этом сигнал логического нуля устанавливается на выходе элемента ИЛИ 41 и элемента И 55, перекрывая выход 21.

Таким образом, при отсутствии команд Разгон и Торможение перекрыты выходы 20 и 21 поступления импульсов с делителя (ускорений) 2 на входы интеграторов 5 и 9 и выход 23 поступления импульсов с генератора 1 на вход интегратора 9. При запуске устройства триггер 35 установится в единичное состояние, сигнал логической единицы с его прямо

го выхода поступит на вход элемента И 51, с входа 12 через элемент И 51, выход 22 на вход первого 5 интегратора начнут поступать импульсы при- ращения независимой переменной. При отработке всего перемещения импульс переполнения с выхода счетчика 11 через вход 31 поступит на вход S триг гера 36 и установит его в единичное состояние. При этом на выходе элемента И 45 установится сигнал логической единицы, который через элемент ИЛИ 37 подается на нулевой вход триг-

.гера 35, устанавливая устройство в исходное состояние,

Работа в режиме Разгон, В этом режиме на вход 32 блока. управления постоянно подан сигнал, соответствующий логической единице, а на вход 33 - логическому нулю. При этом на выходах элемента ИСКЛЮЧАЩЕЕ ИЛИ 42, элемента ИЛИ 38 устанавливает ся логическая единица, и по входу 34 через элементы И 43 и 44, выходам 14 и 15 код скорости, до которой осуще-- ствляется разгон, записывается в регистры 3 и 7(скорости), В этом ре жиме сигнал логической единицы поступает с входа 32 на входы элементов И 47, 49.и 50, а сигнал логического нуля с входа 32 - на входы элементов И 48 и 53, перекрывая выход 23 подачи импульсов приращения независимой переменной на вход (цифрового) интегратора 9, Так как содержимое регистров скорости не совпадает -с содержимым регистров подьштегральных функций интеграторов, то на входах 18 и 19 устанавливаются сигналы логического нуля. При этом сигналы логической единицы устанавливаются на выходах элементов НЕ 57 и 58 и на выходах элементов И 46 и 47, с выхода элемента И 46 сигнал логической единицы через элемент ИЛИ 41 поступает на вход элемента И 55, ас выхода элемента И 47 через элемент ИЛИ 40 сиг- HSLn логической единицы поступает на вход элемента И 54, разрешав прохож- дение импульсов с делителя (ускоре- ний 2 и вьЕсодам 20 и 21 на входы интеграторов 5 и 9,

С выхода элемента И 49 и инверсного выхода триггера 36 сигналы логи- ческой единицы по выходам 24 и 25 подаются на входы интеграторов 5 и

.7, устанавливая регистры подинтег-

15

20

5

0

5

0

5

Q

5

ральных функций интеграторов в режим сложения. При запуске устройства триггер 35 устанавливается в единичное состояние и импульсы с генератора 1 через элемент И 51 и выход 22 поступают на вход интегратора 5, а с делителя (ускорений) 2 через элементы И 52, 54 и 53 и выхода 20 и 21 - на входы регистров подинтегральнь:х функций (цифровых) интеграторов 5 и 9, В момент равенства содержимых регистров подынтегральных функций цифровьгх интеграторов и регистров скорости с вьшодов блоков 4 и 8 сравнения на „ входы 18 и 19 блока управления подаются сигналы, соответствующие логической единице. При этом сигнал логического нуля устанавливается на выходах элементов НЕ 57 и 58, В результате этого появляется сигнал логического нуля на выходах элементов ИЛИ 40 и 41 и перекрываются выходы 20 и 21, Начиная с этого момента работа блока управления не отличается от работы в предыдущем режиме,

Работа в режиме Торможение, В этом режиме на входы 32 и 33 i блока управления поступают сигналы логического нуля и логической единицы соответственно. Запись кода скорости, до которой необходимо осуществить торможение, осуществляется в регистры 3 и 7(скорости) аналогично рассмотренному выше режиму, В этом режиме сигнал логического нуля устанавливается на выходе элемента И 49, с выхода 25 поступает на вход интегратора 9, переключая его регистр под- интегральной функции в режим вычитания.

Так как триггер 36 находится в исходном нулевом состоянии, то смг нал логического нуля с его прямого выхода поступает на вход элемента И 48 и на вход элемента ИЛИ 40, Сигнал логического нуля с выхода элемента И 47 также поступает на вход элемента ИЛИ 40, на вход элемента И 54 и перекрывает выход 20 подачи импульсов с делителя (ускорений) 2 на изменение содержимого регистра подинтегральной функции цифрового интегратора 9, После записи кода скорости с выходов блоков сравнения 4 и 8 по входам 18 и 19 поступают сиг- налы логического нуля. При этом сигнал логического нуля устанавливает-

ся на входах элементов НЕ 57 и 58, а сигн логической единицы - на их выходах и на выходе элемента И 46. Сигнал логической единицы с выхода элемента НЕ 58 поступает на вход элемента И 53, ас выхода элемента И 46 через элемент РШИ 41 - на вход элемента И 55, В результате этого при запуске устройства в этом режиме импульсы с генератора импульсов через элемент И 51, вькод 22 и через .элемент И 53 и выход 23 поступают на входы приращений независимой переменной интеграторов 5 и 9, Импульсы с делителя (ускорений) 2 через вход 13, через элементы И 52 и 55 и выход 21 поступают на вход регистра подинтегральной функции цифрового интегратора 9 в момент равенства содержимого регистра 7 скорости и регистра подинтегральной функции цифрового интегратора 9 с выхода 19 блока 8 сравнения в блок управления поступает сигнал логической единицы, При этом на выходах элемента И 46 элемента ИЛИ.41 и на входе элемента И 55 устанавливается сигнал логического нуля, перекрывая выход 21, для поступления импульсов с делителя ускорений. При переполнении счетчика (перемещений) 11 что свидетельствуе о начале торможения, сигнал логической единицы поступит через вход 31 на единичный вход триггера 36 и установит его в единичное состояние, При этом сигнал логического нуля с инверсного выхода триггера 36 через выход 24 поступит на вход цифрового интегратора 5 и переключит его регистр подынтегральной функции в режи вычитания. Сигнал логической единицы с прямого выхода триггера 36 через элемент И 48 элемент ИЛИ 40 поступит на вход элемента И 34 и импульсы с выхода элемента И 52 начнут поступат через выход 20 на вход регистра подынте ральной функции интегратора 5, В мо-- мент равенства содержимого регистра 3 скорости и регистра подынтеграль ной функции интегратора 5 сигнал ло- гической единицы с выхода блока 4 сравнения через вход 18, через элемент ИЛИ 30, элемент И 45, элемент ИЛИ 37 поступит на ну левой вход триггера 35 и установит устройство в начальное состояние.

тм ь г 10

15

20

25

30

35

40

45

50

55

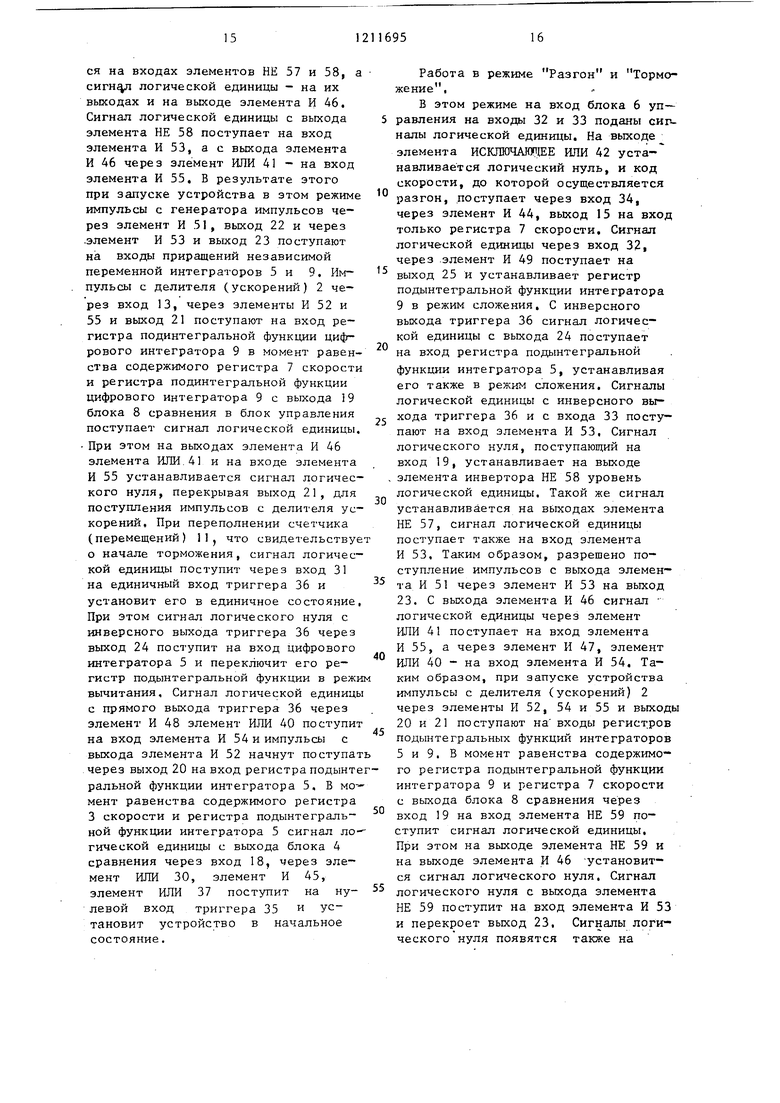

Работа в режиме Разгон и Торможение,

В этом режиме на вход блока 6 управления на входы 32 и 33 поданы сигналы логической единицы. На вьпсоде элемента ИСКЛЮЧАКУЦЕЕ ИЛИ 42 уста- навливаётся логический нуль, и код скорости, до которой осуществляется разгон, поступает через вход 34, через элемент И 44, выход 15 на вход только регистра 7 скорости. Сигнал логической единицы через вход 32, через элемент И 49 поступает на выход 25 и устанавливает регистр подынтегральной функции интегратора 9 в режим сложения, С инверсного выхода триггера 36 сигнал логической единицы с выхода 24 поступает на вход регистра подынтегральной

функции интегратора 5, устанавливая его также в режим сложения. Сигналы логической единицы с инверсного выхода триггера 36 и с входа 33 поступают на вход элемента И 53, Сигнал логического нуля, поступающий на вход 19, устанавливает на выходе элемента инвертора НЕ 58 уровень логической единицы. Такой же сигнал устанавливается на выходах элемента НЕ 57, сигнал логической единицы поступает также на вход элемента И 53, Таким образом, разрешено поступление импульсов с выхода элемента И 51 через элемент И 53 на выход 23, С выхода элемента И 46 сигнал логической единицы через элемент ИЛИ 41 поступает на вход элемента И 55, а через элемент И 47, элемент ИЛИ 40 - на вход элемента И 54, Таким образом, при запуске устройства импульсы с делителя (ускорений) 2 через элементы И 52, 54 и 55 и выходы 20 и 21 поступают на входы регистров подынтегральных функций интеграторов 5 и 9, В момент равенства содержимого регистра подынтегральной функции интегратора 9 и регистра 7 скорости с выхода блока 8 сравнения через вход 19 на вход элемента НЕ 59 поступит сигнал логической единицы. При этом на выходе элемента НЕ 59 и на выходе элемента И 46 установится сигнал логического нуля. Сигнал логического нуля с выхода элемента НЕ 59 поступит на вход элемента И 53 и перекроет выход 23, Сигналы логического нуля появятся также на

выходах элемента И А7 элементов ИШ 40 и 41. При этом перекроются выходы 20 и 21, При переполнении счетчика (перемещений) 11 на вход 31 поступит сигнал логической единицы и установит триггер 36 в единичное состояние. Сигнал логической единицы с прямого выхода триггера 36 через элемент И 50, элемент ИЛИ 41 поступит на вход 5 элемента И 55, а через элемент И 48, элемент ИЛИ 40 - на вход элемента И 54, При этом импульсы с делителя ускорений по выходам 20 и 21 начнут поступать на входы регистров : подинт егральных функций интеграторов

5 и 9, В тцальнейшем работа устройства в этом режиме не отличается от работы в режиме Торможение,

Предлагаемое устройство позволяет наиболее просто осуществить программирование скорости - задается лишь код новой скорости и команды на ее изменение, автоматическое осуществление разгона и торможения, точное определение начала торможения, шисо- кий диапазон уставок ускорения, возможность торможения с ускорением, отличающимся от ускорения при разгоне ,

Пуск

19

JJ

гг

гз

и

Фи.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания скорости в системах числового программного управления | 1984 |

|

SU1259213A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| Устройство для деления частоты пов-ТОРЕНия иМпульСОВ | 1979 |

|

SU817891A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство задания скорости в системах числового программного управления | 1986 |

|

SU1328793A1 |

Составитель Н, Горбунова Редактор Ю. Середа Техред С.Mhrунова Корректор А.Зимокбсов

638/51

Тираж 837 Подписное ; ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Авторы

Даты

1986-02-15—Публикация

1984-03-11—Подача