Изебретение относится к области техники автоматизированного управления производственными процессами, а именно к устройствам для использования в системах числового программного управления станками, и предназначено для преобразования кода скорости подачи в частоту импульсов в различных режимах работы интерполятора.

Цель изобретения - расширение функциональных возможностей путем обеспечения возможности работы устройства при больших значениях ускорений.

Существенным отличием предлагаемого устройства является то, что введение указанных блоков позволяет осуществить нелинейный закон изменения скорости. При этом кривая изменения скорости может быть представлена как две гладкосопряженные ветви двух парабол второго порядка. Это дости-. гается тем, что содержимое регистра подинтегральной функции интегратора изменяется с частотой делителя ускорений не на 1, а на величины 1,2,3, .,.,.,3,2,1,.,. 1,1 где наибольшее приращение скорости, записанное перед началом отработки в регистр наибольшего приращения скорости.

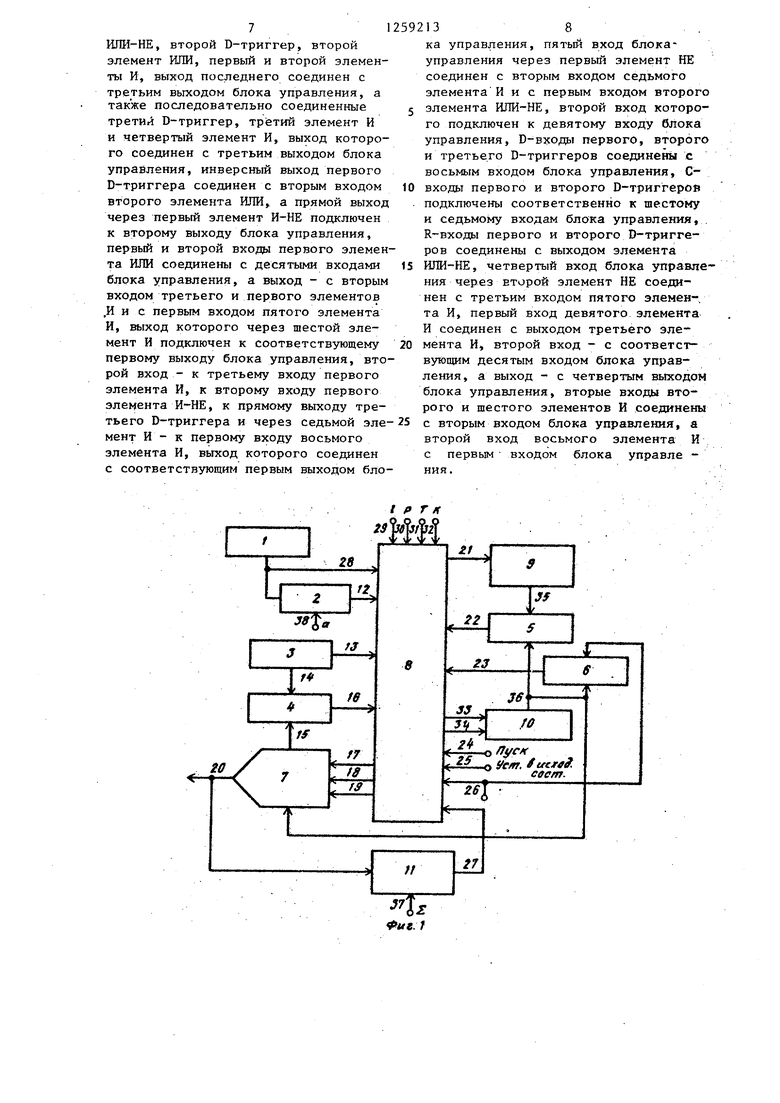

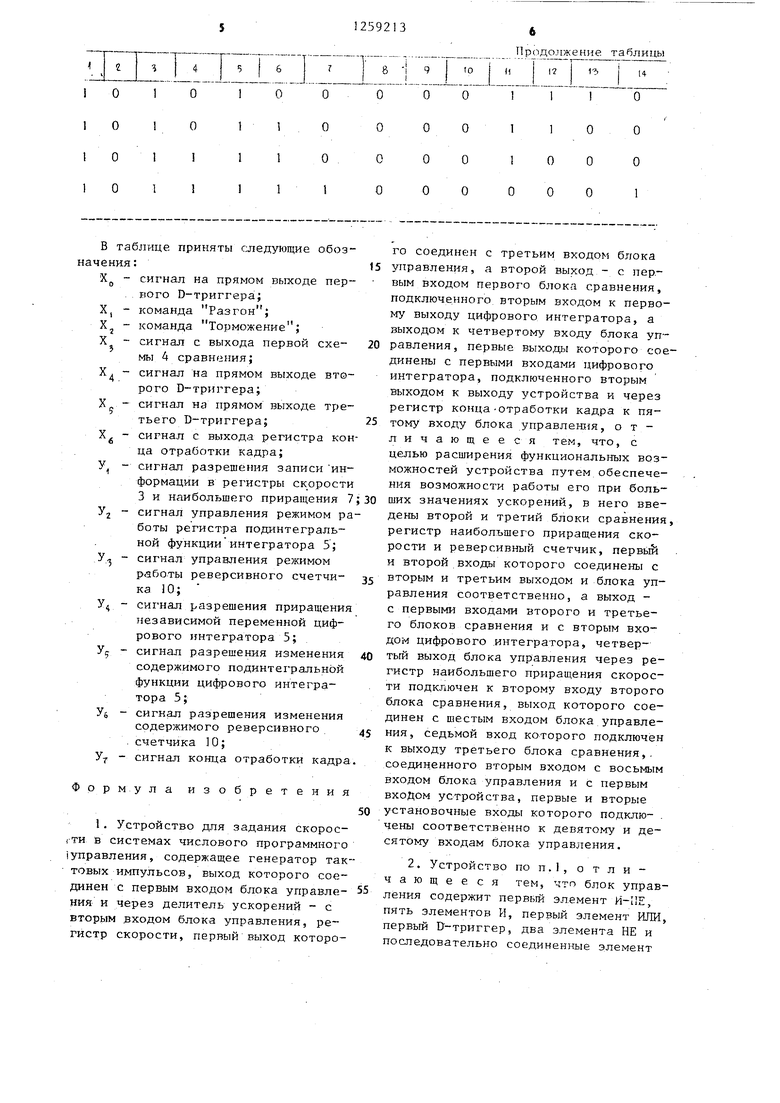

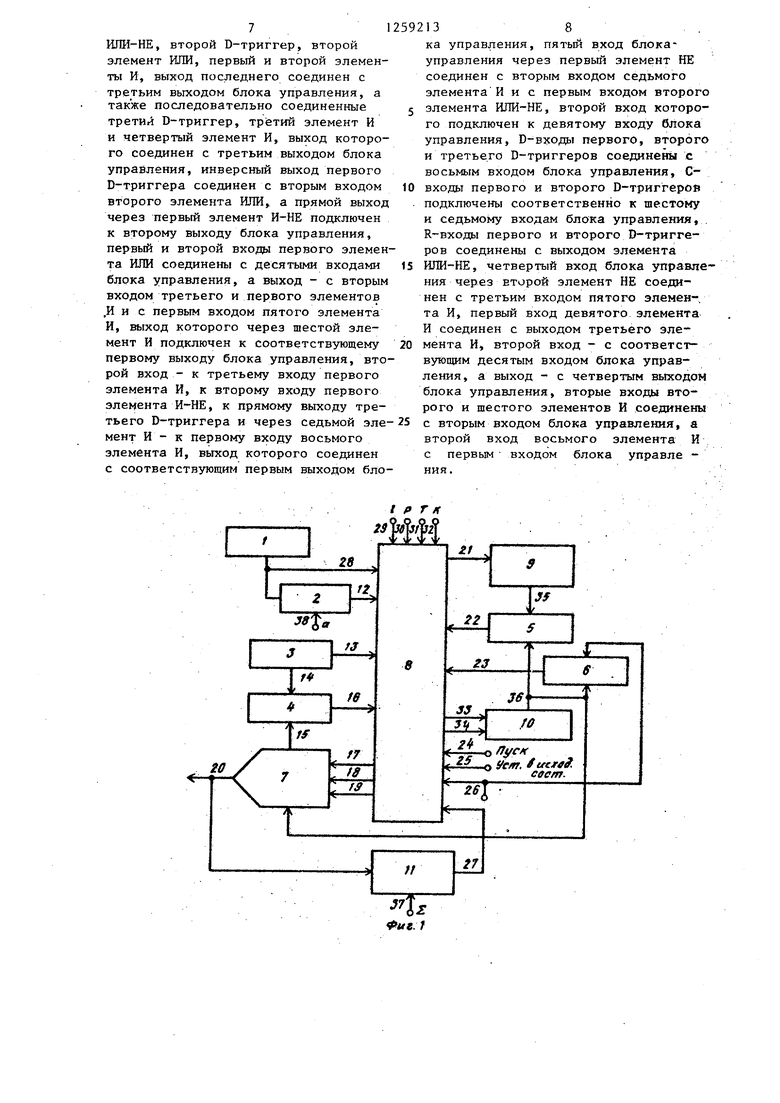

На 4«г, приведена функциональная схема устройства; на фиг.2 - схема |блока управления.

Устройство co : epжит генератор Г ;импульсов, делитель ускорений 2, регистр скорости 4, блоки сравнения 4, 5 и 6, цифровой интегратор 7,блок управления 8, регистр 9 наибольшего ириращения скорости, реверсивный счетчик 10 и регистр П конца отработки кадра, а также входы 12 и выход 13 блока управления 8, выход 14 регистра 3, выход 15 цифрового интегратора 7, вход 16 и выходы 17, 18, 19 блока управления 8, выход 20 цифрового интегратора 7, входа 21-32 и выходы 33, 34 блока управления, выход 35 регистра наибольшего приращения 9, выход 3.6 реверсивного счетчика, вход 37 регистра конца отработки кадра, вход 38 делителя ускорений.

Блок управления 8 (на фиг.2) со- I держит D-т риггеры 39-41, элементы НЕ 42, 43, элемент 44, элемент ИЛИ 45, 46, элемент И-НЕ 47, элементы И 48-56.

15

20

25

592132

Устройство работает следующим об- разом.

В начале каждого кадра в регистр 11 конца отработки кадра записывает- 5 ся сумма перемещений по координатам, а в регистр 9 наибольшего приращения - код наибольшего приращения скорости, определяемый как двоичное представление чиспа к, где О модуль разности кодов начальной и конечной скорости. Режим разгона.

В этом режиме код предыдущей скорости хранится в регистре подинтегральной функции интегратора 7, а код скорости, до которой нужно осуществить разгон, через блок 8 управления по входу 13 поступает в регистр 3 скорости. Реверсивный счетчик 10 устанавливается в исходное состояние, при котором в младшем разряде счетчика записана единица, а во всех остальных разрядах - нули. По команде разгон блок 8 управления вырабатывает сигнал, который по входам 19 и 33 поступает в интегратор 7 и реверсивный счетчик 10 и переводит регистр подинтегральной функции интегратора 7 и реверсивный счетчик 10 в режим сложения. По выходам 18 и 34 в интегратор 7 и реверсивный счетчик Ш поступают импульсы с частотой, определяемой установкой ускорения. При этом содержимое реверсивного

35 счетчика 10 с приходом каждого импульса увеличивается на единицу, а содержимое регистра подинтегральной функции интегратора 7 увеличивается на число, записанное в реверсивном

О счетчике 10. Импульсы приращения независимой переменной с генератора 1 импульсов через блок 8 управления по выходу 17 поступают на вход интегратора 7. Поскольку увеличивается со держймОе регистра подинтегральной функции, то частота импульсов, поступающих с выхода цифрового интегратору будет возрастать. В момент совпадения кодов в регистре 9 наиболь50 шего приращения и реверсивном счетчике 10 блок 6 сравнения вырабатывает сигнал, которьй по входу 22 поступит в блок 8 управления. По этому сигналу последний сформирует сиг55 нал, который по выходу 33 поступит в реверсивный счетчик 10 и переключит его в режим вычитания. В дальнейшем импульсы из блока 8 управления.

31

поступающие по выходу 34 в реверсивный счетчик 10, будут уменьшать его содержимое, В момент равенства содержимого реверсивного счетчика 10 еди нице схема 6 сравнения вырабатывает сигнал,который по входу 23 поступит в блок 8 управления. По этому сигналу блок 8 управления перекроет выход 34 и прекратит поступление импульсов изменяющих содержимое реверсивного счетчика 10. В дальнейшем с приходом каждого импульса с делителя 2 ускорений содержимое регистра подинтег- ральной функции цифрового интегратора 7 будет увеличиваться на единицу. В момент равенства содержимого регистра 3 скорости и регистра подин- тегральной функции цифрового интегратора 7 блок 4 сравнения вырабатывает сигнал, который по входу 16 пос- тупит в блок 8 управления. По этому сигналу блок В управления перекроет выход 18 и в регистре подинтеграль- ной функции цифрового интегратора 7 за(|тксируется код конечной скорости, а частота импульсов на выходе интегратора перестанет, изменяться. Появление импульса переполнения на выходе регистра I1 конца отработки кадра свидетельствует об отбработке за- данного пути. Импульс переполнения

134

с выхода регистра II конца отработки кадрй по входу 27 поступает в блок 8 управления, и работа устройства прекращается.

Режим торможения.

В этом режиме от программы череэ блок 8 управления в регистр 3 скорости перед началом работы устройства поступит код скорости t, до которой нужно осуществить торможение. В блок 8 управления поступает команда Торможение. При этом регистр подинтег- ральной функции интегратора 7 переключается в режим вычитания. В ос-т тальном работа устройства не отличается от работы в режиме Разгон.

Режим постоянной скорости.

В этом режиме выходы 18 и 34 перекрыты, содержимое регистра подин- тегральной функции в процессе работы устройства не изменяется и с выхода интегратора 7 поступают импульсы постоянной частоты. Работа устройства как и в предыдущих режимах прекращается по сигналу переполнения, поступающему в блок 8 управления по входу 27 с выхода регистра 11 конца отработки кадра.

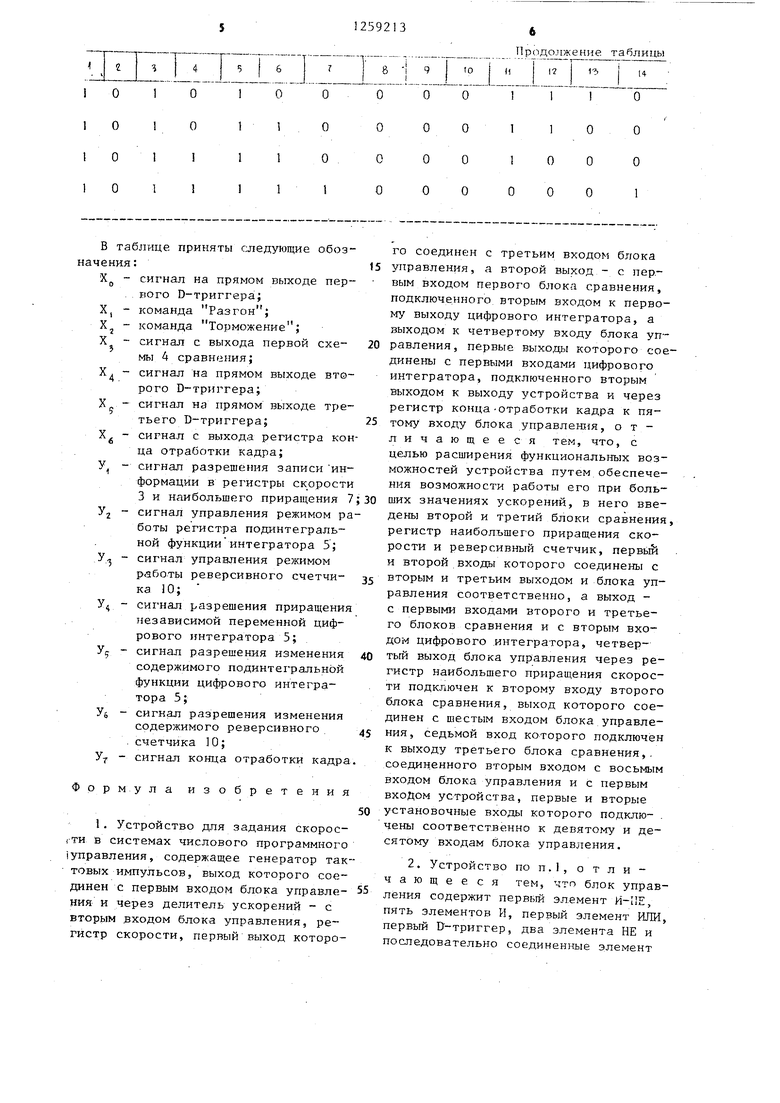

Работа устройства управления может быть описана следующей таблицей.

В таблице приняты следующие обозначения:

- сигнал на прямом выходе пер- ..1ЮГО D-триггера;

- команда Разгон ;

- команда Торможение ;

сигнал с выхода первой схе- 20 мы 4 сравнения;

- сигнал на прямом выходе второго D-триггера;

- сигнал на прямом выходе третьего D-триггера;25

- сигнал с выхода регистра конца отработки кадра;

- сигнал разрешения записи информации в регистры ск орости 3 и наибольшего приращения 7;30

- сигнал управления режимом работы регистра подинтеграль- ной функции интегратора 5;

- сигнал упрааления режимом

работы реверсивного счетчи- 35 ка 10;

- сигнал разрешения приращения независимой переменной цифрового IП тeгpaтopa 5;

сигнал разрешения изменения 40 содержимого подинтегральной функции цифрового интегратора 5;

- сигнал разрешения изменения

содержимого реверсивного s . счетчика 10;

- сигнал конца отработки кадра.

Формула изобретения

I. Устройство для задания скорос- гти в системах числового программного {управления, содержащее генератор так- товых импульсов, выход которого соединен с первым входом блока управле- ния и через делитель ускорений - с вторым входом блока управления, регистр скорости, первый выход котороПродолжение таблицы

го соединен с третьим входом блока управления, а второй выход - с первым входом первох о блока сравнения, подключенного, вторым входом к первому выходу цифрового интегратора, а выходом к четвертому входу блока управления, первые выхо,ды которого соединены с первыми входами цифрового интегратора, подключенного вторым выходом к выходу устройства и через регистр конца-отработки кадра к пятому входу блока управления, о т - личающееся тем, что, с целью расширения функциональных возможностей устройства путем,обеспечения возможности работы его при больших значениях ускорений, в него введены второй и третий блоки сравнения, регистр наибольшего приращения скорости и реверсивный счетчик, первьй и второй входы которого соединены с вторым и третьим выходом и блока управления соответственно, а выход - с первыми входами второго и третьего блоков сравнения и с вторым входом цифрового интегратора, четвертый выход блока управления через регистр наибольшего приращения скорости подключен к второму входу второго блока сравнения, выход которого соединен с шестым входом блока управления, седьмой вход которого подключен к выходу третьего блока сравнения,, соединенного вторым входом с восьмым входом блока управления и с первым входом устройства, первые и вторые установочные входы которого подклю- . чены соответственно к девятому и десятому входам блока управления,

2. Устройство по п.1, о т л и - чающееся тем, что блок управления содержит первый элемент И-ПЕ, пять злементов И, первый элемент ИЛИ, первый D-триггер, два элемента НЕ и последовательно соединенные элемент

71

ИЛИ-НЕ, второй D-триггер, второй элемент ИЛИ, первый и второй элементы И, выход последнего соединен с третьим выходом блока управления, а также последовательно соединенные третий D-триггер, третий элемент И и четвертый элемент И, выход которого соединен с третьим выходом блока управления, инверсный выход первого D-триггера соединен с вторым входом второго элемента ИЛИ, а прямой выход через первый элемент И-НЕ подключен к второму выходу блока управления, первый и второй входы первого элемента ИЛИ соединены с десятыми входами блока управления, а выход - с вторым входом третьего и первого элементов ,И и с первым входом пятого элемента И, выход которого через шестой элемент И подключен к соответствующему первому выходу блока управления, вто рой вход - к третьему входу первого элемента И, к второму входу первого элемента И-НЕ, к прямому выходу третьего D-триггера и через седьмой эле мент И - к первому входу восьмого элемента И, выход которого соединен с соответствздащим первым выходом бло

592138.

ка управления, пятый вход блока- управления через первьп элемент НЕ соединен с вторым входом седьмого элемента И и с первым входом второго 5 элемента ИЛИ-НЕ, второй вход которого подключен к девятому входу блока управления, D-входы первого, второго и третьего D-триггеров соединены с восьмым входом блока управления, С10 входь первого и второго D-триггеров . подключены соответственно к шестому и седьмому входам блока управления, . R-входы первого и второго D-триггеров соединены с выходом элемента

15 Р1ЛИ-НЕ, четвертый вход блока управления через второй элемент НЕ соединен с третьим входом пятого элемен-, та И, первый вход девятого, элемента И соединен с выходом третьего эле20 мента И, второй вход - с соответст- вуюпщм десятым входом блока управления, а выход - с четвертым вьпсодом блока управления, вторые входы второго и шестого элементов И соединены 25 с вторым входом блока управления, а второй вход восьмого элемента И с первым входом блока управле - ния.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задания скорости в системах числового программного управления | 1984 |

|

SU1211695A1 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| Масштабный интегратор | 1976 |

|

SU746601A1 |

| Цифровой интегратор | 1976 |

|

SU651371A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство стабилизации амплитуды видеосигнала | 1988 |

|

SU1603538A2 |

| Интерполятор для систем программного управления | 1977 |

|

SU658528A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| Устройство для цифрового дифференцирования | 1975 |

|

SU608145A1 |

| Многокоординатный цифровой линейный интерполятор | 1987 |

|

SU1522154A1 |

Изобретение касается автоматизированного управления производственнь1ми процессами, и может быть использовано в системах ЧПУ станками. Оно является частью цифрового интерполятора и предназначено для преобразования кода скорости подачи в частоту импульсов в различных режимах работы интерполятора. Целью изобретения является расширение функциональных возможностей устройства за счет возможности его работы при больших значеьшях ускорений. Устройство содержит генератор импульсов, делитель ускорений, регистр скорости, блоки сравнения, цифровой интегратор, блок управления, регистр наибольшего приращения скорости, реверсивный счетчик, регистр конца обработки кадра. Устройство работает в трех режимах: постоянной скорости, торможения и разгона. 1 з.п. ф-лы, 2 ил, 1 табл. с S (Л С

Авторы

Даты

1986-09-23—Публикация

1984-05-22—Подача