Изобрет ние относится к контрольно-измерительной и вычислительной технике.

Целью изобретения является увеличение функциональной надежности путем повышения достоверности результатов самоконтроля аналого-цифровог преобразователя.

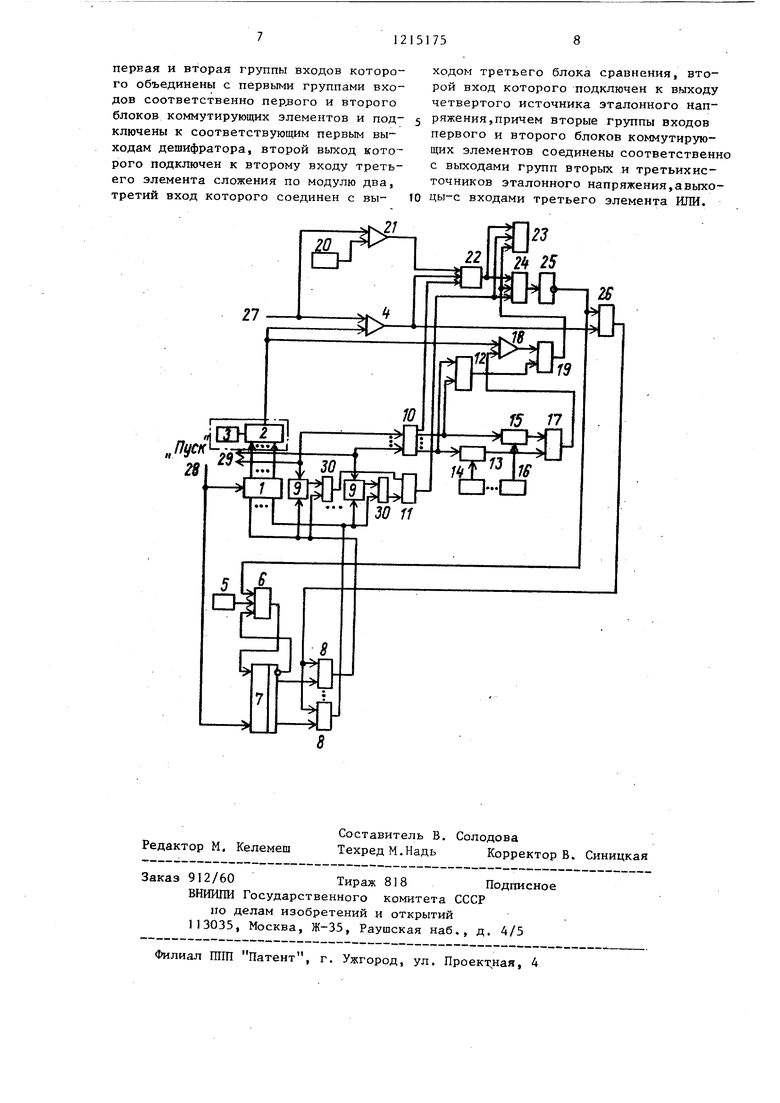

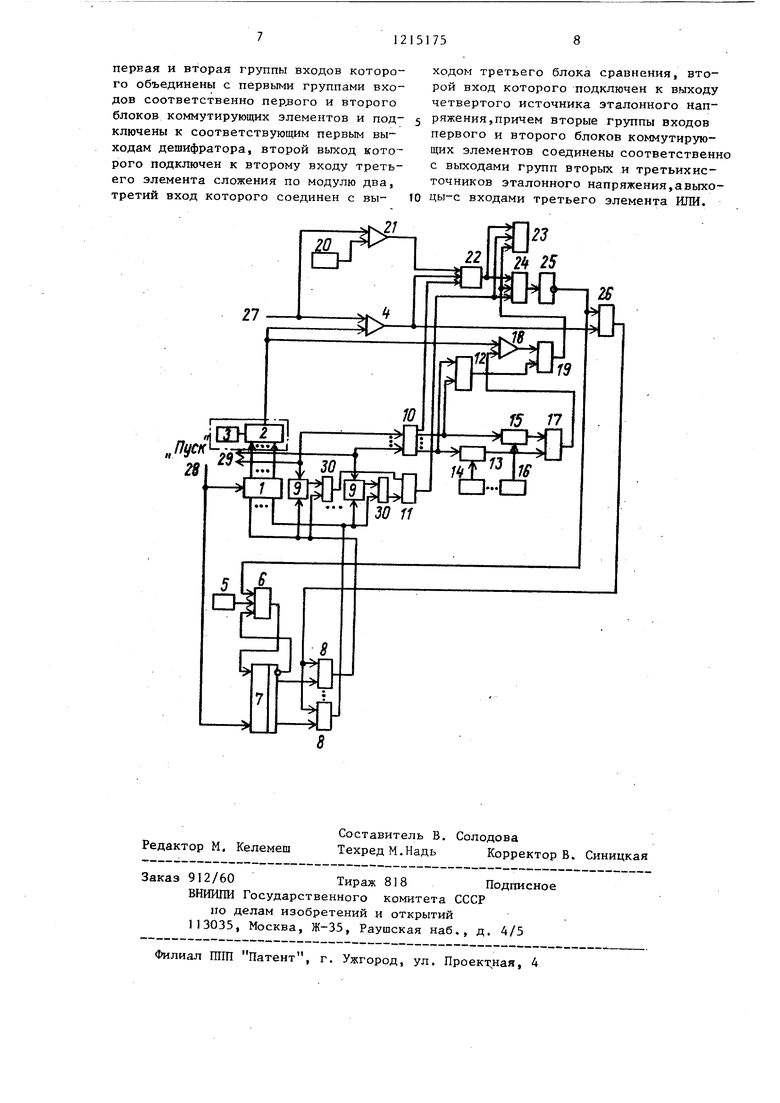

На чертеже представлена блок-схема аналого-цифрового преобразователя

Аналого-цифровой преобразователь содержит регистр 1, резистивную матрицу R 2 R 2 преобразователя код - напряжение и его первый источник 3 эталонного напряжения, первый блок 4 сравнения, генератор 5 тактовых импульсов, первый элемент И 6, регистр 7 сдвига, группу вторых элементов И 8, группу первых элементов 9 сложения по модулю два, дешифра- тор 10, первый элемент ИЛИ П, второй .элемент ИЛИ 12, первый блок 13 коммутирующих элементов, группу вторых источников 14 эталонного напряжения , второй блок 15 коммутирующих элементов, группу третьих источников 16 эталонного напряжения, третий элемент ИЛИ 17, второй блок 18 сравнения, второй элемент 19 сложения по модулю два, четвертый источник 20 эталонного напряжения, третий блок 21 сравнения, третий элемент 22 сложения по модулю два, блок 23 индикации, четвертый элемент ИЛИ 23, элемент НЕ 25, третий элемент И 26, входную шину 27, шину 28 Пуск, выходные шины 29, группу четвертых элементов И 30.

Аналого-цифровой преобразователь работает следующим образом.

В аналого-цифровом преобразователе основными элементами являются резистивная матрица R- 2 R 2 и первый источник 3 эталонного напряжения, с помощью которых вырабатывается сумма эталонных напряжений, соответствующая набранному коду. Измеряемое напряжение Uy с входной шины 27. поступает на первый вход первого блока 4 сравнения, а на его второй вход подается с резистивной матрицы R-2 R 2 сумма эталонных напряжений. Первый блок 4 сравнения вьщает сигнал, эквивалентный логической 1, когда напряжение, подаваемое на его первый вход Ux , больше или равно сумме эталонных напряжений, поступающей на его второй

752

вход, т.е. приОх эТ случае Un-iDgr , с выхода первого блока 4 , сравнения снимается сигнал, эквивалентный О. Сигнал с выхода первого блока 4 сравнения поступает через элемент И 26 и на первые входы группы вторых элементов И 8.

В исходном состоянии в регистре 7 сдвига в младшем (первом) разряде записана единица, а в остальных разрядах нули. В этом случае с первого (инверсного) выхода регистра 7 сдвига вьщается сигнал, эквивалентный логическому О, который запрещает прохождение импульсов с выхода генератора 5 тактовых импульсов через элемент И 6 и на информационный вход регистра 7 сдвига.

Работа аналого-цифрового преобразователя начинается в момент поступления на его шину 28 сигнала Пуск. При этом все разряды регистра 1 устанавливаются в нулевое состояние. По этому же сигналу Пуск единица с

младшего (первого) разряда регистра 7 сдвига переносится в следующий разряд. В этом случае с первого (инверсного) выхода регистра 7 сдвига подается сигнал, эквивалентный логической 1 на третий вход первого элемента И 6, На первый вход элемента И 6 поступает сигнал, эквивалентный логической 1, с выхода элемента НЕ 25.

Импульсы с выхода генератора 5 тактовых импульсов через элемент И 6 поступают на информационный вход регистра 7 сдвига. Начинается формирование суммы эталонных напряжений

с помощью регистра 1, резистивной матрицы R -2 R 2 и первого источника 3 эталонного напряжения. С выхода регистра 1 код, определяющий значение суммы эталонных напряжений, поступает на выходы 29 аналого-цифрового преобразователя.

Контроль правильности функционирования аналого-цифрового преобразователя осуществляется следующим образом.

Контроль правильности функционирования регистра 1 заключается в поряэрядном сравнении его входной и выходной информации.

Информация, поступающая на информационные входы регистра 1, одновреенно поступает па первые входы группы первых элементон 9 сложения .то

3

модулю два и на первые входы группы четвертых элементов И 30, На вторые входы группы первых элементов 9 сложения по модулю два снимается информация с выходов регистра 1. В случа поразрядного несоответствия входной и выходной информации регистра 1 с выхода соответствующего элемента 9 сложения по модулю два снимается сигнал, соответствующий логической М. Этот сигнал поступает на второ вход соответствующего элемента И 30 При наличии сигнала, эквивалентного логической 1, на первом входе этого элемента И 30 с его выхода выдается сигнал, эквивалентный логической I, который через элемент ИЛИ 11 поступает на второй вход блока 23 индикации, В этом случае блок 23 индикации выдает информацию о неисправности регистра 1. Одновременно с выхода элемента ИЛИ 11 сигнал, эквивалентный логической 1, поступает через элемент 11ГШ 24 на вход элемента НЕ 25, с выхода которого в данном случае подается сигнал, эквивалентный логическому О, который запрещает прохождение импульсов с выхода генератора 5 тактовых импульсов на вход регистра 7 сдвига. Этот же сигнал с выхода элемента НЕ 25 запрещает прохождение сигнала с выхода первого блока 4 сравнения. Аналого-цифровой преобразователь прекращает свое функционирование.

Контроль правильности функционирования резистивной матрицы R -2 R 2 состоит в сравнении ее выходного напряжения с наперед заданным эталонным напряжением с использованием группы вторых 14 и третьих 16 источников эталонного напряжения и второго блока 18 сравнения. Количество источников 14 и 16 эталонного напряжения определяется требованиями, предъявляемыми к уровню достоверности контроля правильности- функционирования резистивной матрицы R-2 R 2. Выходная информация с регистра I поступает на вход дешифратора 10, который обеспечивает поочередное подключение источников 14, 16 эталонного напряжения через соответствующие первый 13-и второй 15 блоки коммутирующих элементов и элемент ИЛИ 17 к второму входу второго блока 18 сравнения. На первый вход второго блока 18 сравнения пос5

тупает напряжение с выхода резистивной матрицы R-2R2. Второй блок 18 сравнения вьщает сигнал, эквивалентный логической 1, когда напряжение, подаваемое на его первый вход, больше или равно напр-яжения, поступающего на его второй вход. В случае неисправности резистивной матрицы R-2R2 указанное условие, соответствующее ее правильному функционированию, не выполняется и с выхода второго блока 18 сравнения на первьв вход второго элемента 19 сложения по модулю два поступает на

сигнал, эквивалентный логическому О, а на его второй вход поступает сигнал с выхода дешифратора 10 через элемент ИЛИ 12, определяющий выбор соответствующего источника 14,

16 эталонного напряжения. С выхода элемента 19 сложения по модулю два сигнал, эквивалентный логической 1, поступает на- третий вход блока 23 индикации, который выдает информацию о наличии неисправности в ре- зис;тивной матрице R-2R 2. Одновременно с выхода элемента 19 сложения по модулю два сигнал, эквивалентный логической 1, поступает через элемент ИЛИ 24 на вход элемента НЕ 25. С этого момента аналого-цифровой преобразователь прекращает свою работу.

Работоспособность первого блока 4 сравнения контролируется только в тот момент времени, когда на выходе регистра 1 будет код, который соответствует подаче на вход блока 4 эталонного напряжения, равного эталонно

му напряжению четвертого источника

20 эталонного напряжения, и заключаеся в сравнении выходных сигналов первого 4 и третьего 21 блоков сравнения на фиксированном значении эта45 лонного напряжения, подаваемого на второй вход третьего блока 21 сравнения от четвертого источника 20 эталонного напряжения. Третий элемент 22 сложения по модулю два вы50 дает сигнал, эквивалентный логическому О, в случае отсутствия неис - правности первого блока 4 сравнения при одновременном поступлении на его первый и второй входы сигналов, эк55 вивалентнь1х логической 1 или логическому О, при наличии управляющего сигнала на его третьем входе с выхода дешифратора 10. Сигнал с

выхода дешифратора 10 выдается только тогда, когда напряжение, снимаемое с выхода резистивной матрицы R-2R2, станет равным заранее выбранному значению напряжения, снимаемому с выхода четвертого источника 20 эталонного напряжения. При несовпадении выходных сигналов первого 4 и третьего 21 блоков сравнения (в случае неисправности первого 4 блока сравнения) и при наличии управляющего сигнала с выхода дешифратора 10 элемент 22 сложения по модулю два вьщает сигнал на первый вход блока 23 индикации, который вьщает информацию о наличии неисправности в бло ке 4 сравнения. Одновременно сигнал с выхода элемента 22 сложения по модулю два через элемент RTIH 24 поступает на вход элемента НЕ 25. С этого момента аналого-цифровой преобразователь прекращает свою работу.

Форм.ула изобретения

Аналого-цифровой преобразователь содеТ жащий регистр, преобразователь код-напряжение, выполненный на последовательно соединенных первом источнике эталонного напряжения и резистивной матрице R-2R, первый блок сравнения, генератор тактовых импульсов, первый элемент И, группу вторых элементов И, регистр сдвига, выход генератора тактовых импульсов подключен к первому входу первого элемента И, второй вход которого соединен с инверсным выходом регистра сдвига, а выход - с информационным входом регистра сдвига, управляющий вход которогообъединен с управляющим входом регистра и является пшной Пуск, прямые выходы регистра сдвига соединены с первыми входами группы соответствую1цих вторых элементов И, выходы которых подключены к соответствующим инфор мационным входам регистра, выходы которого соединены соответственно с вторыми входами резистивной матрицы R-2 R и являются выходными шинами, а выход резистивной матрицы R-2R соединен с первым входом первого блока сравнения, второй вход которого является входной шиной, отличающийся тем, что, с. целью повыгаения функциональной надежности устройства, в него введены группа первых элементов сложения по модулю два, дешифратор, первый, второй, третий и четвертый элементы ИЛИ, первый и второй блоки коммутирующих элементов, группы вторых и третьих источников эталонного напряжения, четвертый источник эталонного напряжения, второй и третий блоки сравнения, третий элемент И, второй и третий элементы ело- жения по модулю два, блок индикации, элемент НЕ, группа четвертых элементов И, при этом выход третьего элемента И подключен к вторым входам группы вторых элементов И, первые входы группы четвертых элементов И объединены с соответствую- щими первыми входами группы первых элементов сложения по модулю два и соединены с соответствующими выходами группы вторых элементов И, вторые входы группы первых элементов

сложения объединены с соответствующими входами дешифратора и соедине- гы с соответствующими выходами регистра, вторые входы группы четвертых элементов И соединены с соответствующими выходами группы первых элементов сложения по модулю два, а выходы - с соответствующими входами первого элемента ИЛИ, первый вход блока индикации объединен с первым

входом четвертого элемента ИЛИ и соединен с выходом третьего элемента сложения по модулю два, второй вход блока индикации объединен с вторым входом четвертого элемента ИЛИ

и соединен с выходом первого элемента ИЛИ, третий вход блока индикации объединен с третьим входом четвертого элемента ИЛИ и соединен с выходом второго элемента сложения по модулю

два, выход четвертого элемента ИЛИ через элемент НЕ соединен с первым входом третьего элемента И, второй вход которого объединён с первым входом третьего элемента сложения

по модулю два и соединен с выходом первого блока сравнения, первый вход которого соединен с первым входом второго блока сравнения, второй вход которого соединен с выходом третьего

элемента 1ШИ, а выход - с первым входом второго элемента сложения по модулю два, второй вход которого соединен с выходом второго элемента ИЛИ,

первая и вторая группы входов которого объединены с первыми группами входов соответственно первого и второго блоков коммутирующих элементов и подключены к соответствующим первьм выходам дешифратора, второй выход которого подключен к второму входу третьего элемента сложения по модулю два, третий вход которого соединен с выходом третьего блока сравнения, второй вход которого подключен к выходу четвертого источника эталонного нап5 ряжения,причем вторые группы входов первого и второго блоков коммутирующих элементов соединены соответственно с выходами групп вторых и третьихис- точников эталонного напряжения,авыхо10 цы-с входами третьего элемента ИЛИ.

27

2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля сопротивления | 1988 |

|

SU1651231A1 |

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU886236A2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| Устройство аналого-цифрового преобразования с самоконтролем | 1989 |

|

SU1695498A1 |

| Устройство для контроля дискретных систем | 1983 |

|

SU1117640A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| Устройство для контроля состояния диагностируемых цепей | 1985 |

|

SU1316002A1 |

| Устройство параллельно-последователь-НОгО АНАлОгО-цифРОВОгО пРЕОбРАзОВА-Ния C САМОКОНТРОлЕМ | 1979 |

|

SU815904A1 |

Изобретение относится к области контрольно-измерительной к вычислительной техники и позволяет увеличить функциональную надежность аналого-цифрового преобразователя за счет повышения достоверности результатов его самоконтроля. Контроль правильности функционирования регистра 1 заключается в поразрядном сравнении его входной и выходной информации. Контроль резистивной матрицыЛ -2 R 2 состоит в сравнении ее выходного напряжения с наперед заданным эталонным напряжением с исполь- зованием групп вторых и третьих источников 14 и 16 эталонного напряжения и второго блока 18 сравнения. Работоспособность первого блока 4 сравнения контролируется путем сравнения выходных сигналов его и третьего блока 21 сравнения на фиксированном значении эталонного напряжения, подаваемого на второй вход третьего блока 21 сравнения от четвертого источника 20 эталонного напряжения. Третий элемент 22 сложения по модулю два выдает сигнал, эквивалентный логическому О в случае отсутствия неисправности первого блока 4 сравнения. При несовпадении выходных сигналов первого и третьего блоков 4 и 21 сравнения в случае неисправности первого блока 4 сравнения и при наличии управляющего сигнала с выхода дешифратора 10 элемент 22 сложения по модулю два выдает сигнал на первый вход блока 23 индикации, который выдает информацию о наличии неисправности в блоке 4 сравнения. 1 ил. (Л С Ю ел ел

Редактор М. Келемеш

Заказ 912/60Тираж 818 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал mm Патент, г. Ужгород, ул. Проект,ная, 4

Составитель В. Солодова

Техред М.Надь Корректор В. Синицкая

| 0 |

|

SU167373A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Гитис Э,И | |||

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| М.: Энергия, 1975, с | |||

| РАССЕИВАЮЩИЙ ТОПЛИВО МЕХАНИЗМ | 1920 |

|

SU298A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1986-02-28—Публикация

1984-04-11—Подача