1

Иаобретение относится к вычисли тельной технике и телемеханике и может быть использовано для обмена информацией в различных системах сбора и обработки информации и в устройствах для рассредоточенных объектов.

Цель изобретения - увеличение дальности передачи и расширение области применения устройства путем обеспечения сопряжения с различными каналами связи.

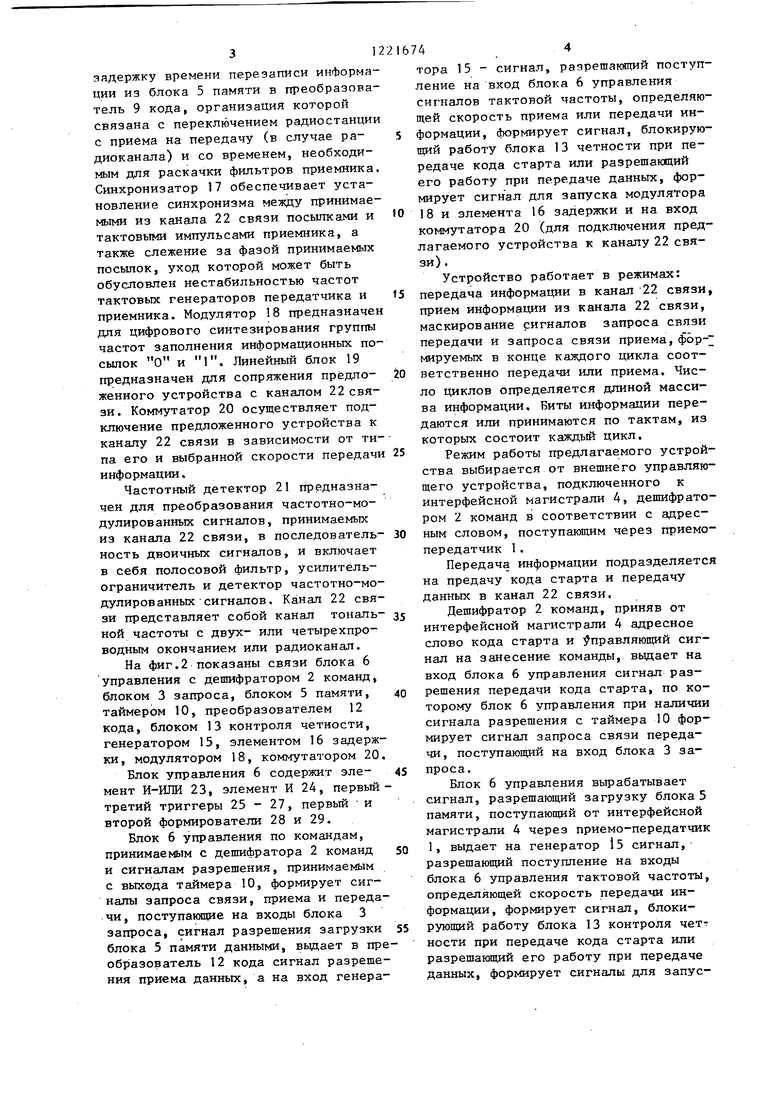

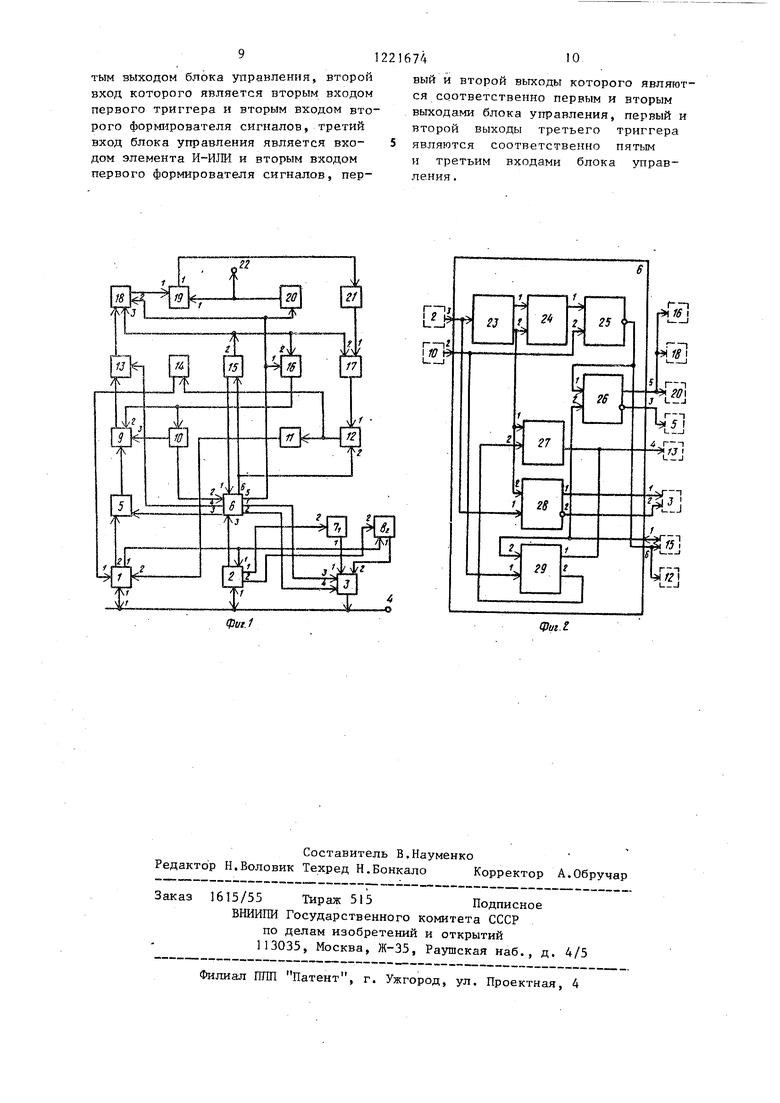

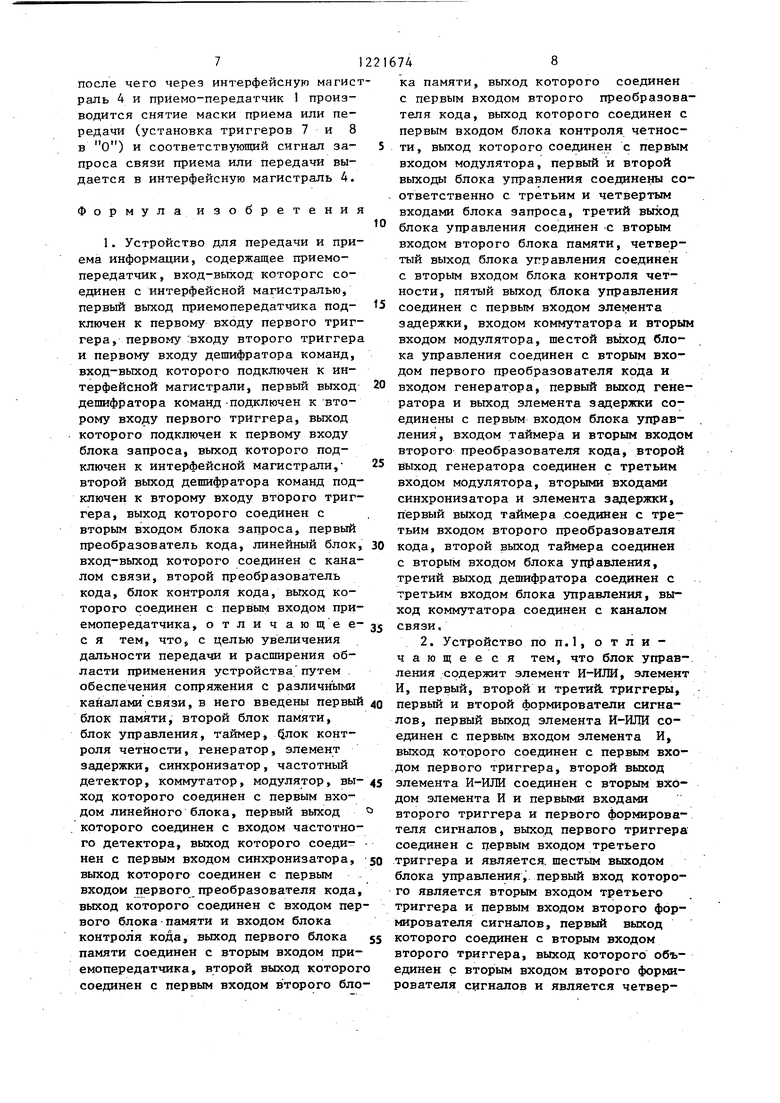

На фиг.1 представлена блок-схема предложенного устройства; на фиг.2- вариант функциональной схемы исполнения блока управления.

Устройство содержит приемо-пере- датчик 1, дешифратор 2 команд, блок 3 запроса, подключенные к интерфейсной магистрали 4, блок 5 памяти, соединенный с выходами приемо-передат- чика I и блока 6 управления, триггеры 7 и 8 соединенные с приемо-пере- датчиком 1, дешифратором 2 команд и блоком 3 запроса, соединенным с блоком 6 управления, преобразователь 9 кода, подключенный к блоку-5 памяти и таймеру 10, соединенному с блоком 6 управления, блок 11 памяти, соединенный f с блоком 6 управления, блок 11 памяти, соединенный с приемо-пере датчиком 1, преобразователь 12 кода, подключенный к блоку 6 управления, блок 13 контроля четности, соединен- ньй с преобразователем 9 кода и блоком 6,управления, блок 14 контроля кода, соединенный с приемо-передатчи ком I и с блоком 11 памяти и преобразователем 12 кода, генератор 15, соединенный с блоком 6 управления, преобразователем 9 кода, таймером 10, элементом 16 задержки и синхронизатором 17, соединенным с преобразователем 12 кода, модулятор 18, соединенный с блоком 6 управления, блоком 13 контроля четности, генератором 15, .элементом 16 задержки и с линейным блоком 19, подключенным к коммутатору 20, частотному детектору 21, соединенному с синхронизатором 17, и к каналу 22 связи, соединенному с коммутатором 20, подключенным к блоку 6 управления, элементу 16 задержки и модулятору 18.,

Приемо-передатчик 1 осуществляет параллельное двунаправленное формирование сигналов для приема и передачи информации с шин интерфейсной магистрали 4 от подключенного к ней внеш1

--

15

20

25

2216742

него управляющего устройства (не показанного) . Дешифратор 2 команд - прием кода команд от интерфейсной магистрали 4, организующих различные

5 режимы работы предложенного устройства. Блок 3 запроса предназначен для вьщачи в интерфейсную магистраль 4 маскированных сигналов запроса связи приема или передачи.

Интерфейсная магистраль 4 представляет собой набор шин адресных информационных и управляющих сигналов и предназначена для связи предложенного устройства с управляющими и другими устройствами, подключенными к . данной магистрали.

Блок 5 памяти осуществляет хранение байта передаваемой информации в период между двумя запросами связи передачи, с которыми предложенное устройство обращается к интерфейсной магистрали 4 при передаче информации. Блок 6 управления организует работу всех блоков по алгоритму, задаваемому выбранным режимом работы устройства. Триггеры 7 и 8 служат для маскирования сигналов запроса связи приема и передачи соответственно. Преобразователь 9 кода преобразует параллельный код передаваемой информации в последовательный. Таймер 10 устанавливает длительность передачи одного байта. Блок 11 памяти осуществляет хранение байта принимаемой ин35 формации в период между двумя запросами связи приема, с которыми предложенное устройство обращается к интерфейсной магистрали 4 при приеме информации. Преобразователь 12 кода

40 осуществляет преобразование последовательного кода принимаемой информации в параллельный. Блок 13 контроля четности предназначен для проверки на нечет байта передаваемой информа45 ции и, при необходимости, дополняет его до нечета в защитном разряде. Блок 14 контроля кода предназначен для проверки кодовых комбинаций принимаемых сигналов, Генератор 15 фор- .

50 мирует сигналы различных частот, необходимые для работы предложенного устройства со скоростью, выбранной в зависимости от типа канала 22 связи, сигналы опорной частоты, исполь55 зуемой в модуляторе 18, и тактирующие сигналы, необходимые для работы синхронизатор.а 17 и блока 6 управления. Элемент 16 задержки формирует

30

31

задержку времени перезаписи информации из блока 5 памяти в преобразователь 9 кода, организация которой связана с переключением радиостанции с приема на передачу (в случае ра- диоканала) и со временем, необходимым для раскачки фильтров приемника Синхронизатор 17 обеспечивает установление синхронизма между принимаемыми из канала 22 связи посылками и тактовыми импульсами приемника, а также слежение за фазой принимаемых посылок, уход которой может быть обусловлен нестабильностью частот тактовых генераторов передатчика и приемника. Модулятор 18 предназначен для цифрового синтезирования группы частот заполнения информационных посылок О и 1. Линейный блок 19 предназначен для сопряжения прёдло- женного устройства с каналом 22 связи. Коммутатор 20 осуществляет подключение предложенного устройства к каналу 22 связи в зависимости от типа его и выбранной скорости передачи информации.

Частотный детектор 21 предназначен для преобразования частотно-модулированных сигналов, принимаемьгх из канала 22 связи, в последователь- ность двоичных сигналов, и включает в себя полосовой фильтр, усилитель- ограничитель и детектор частотно-модулированных сигналов. Канал 22 связи представляет собой канал тональ- ной частоты с двух- или четырехпро- водным окончанием или радиоканал.

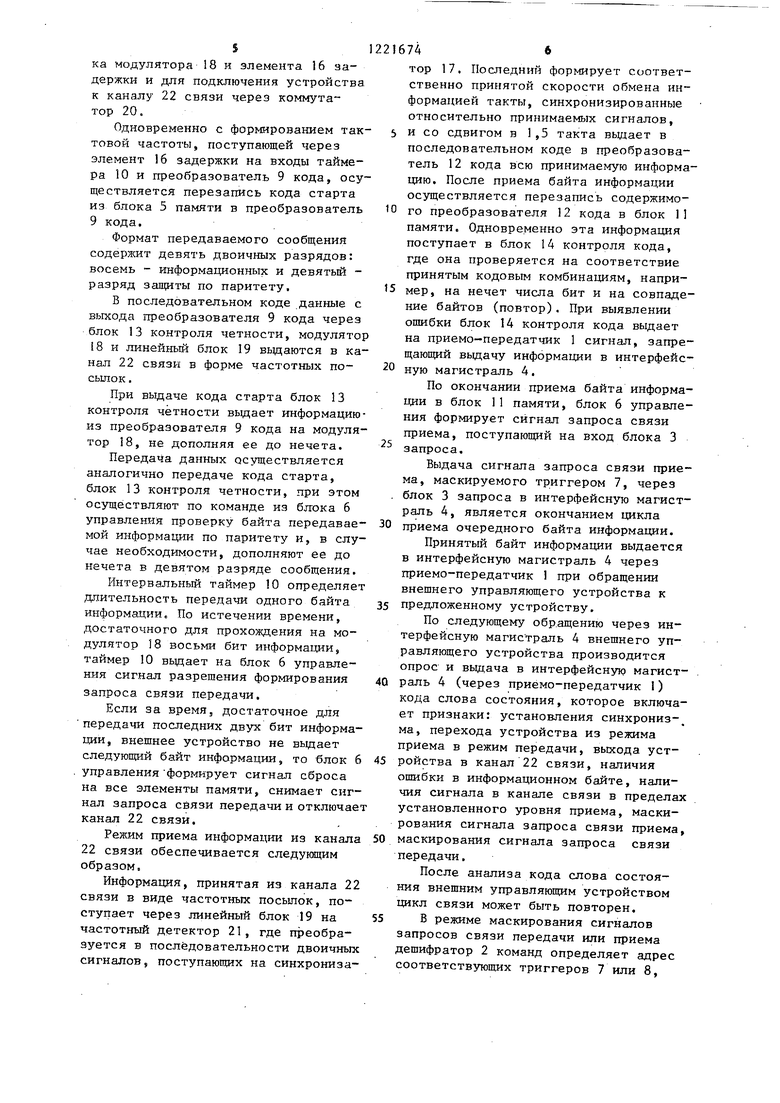

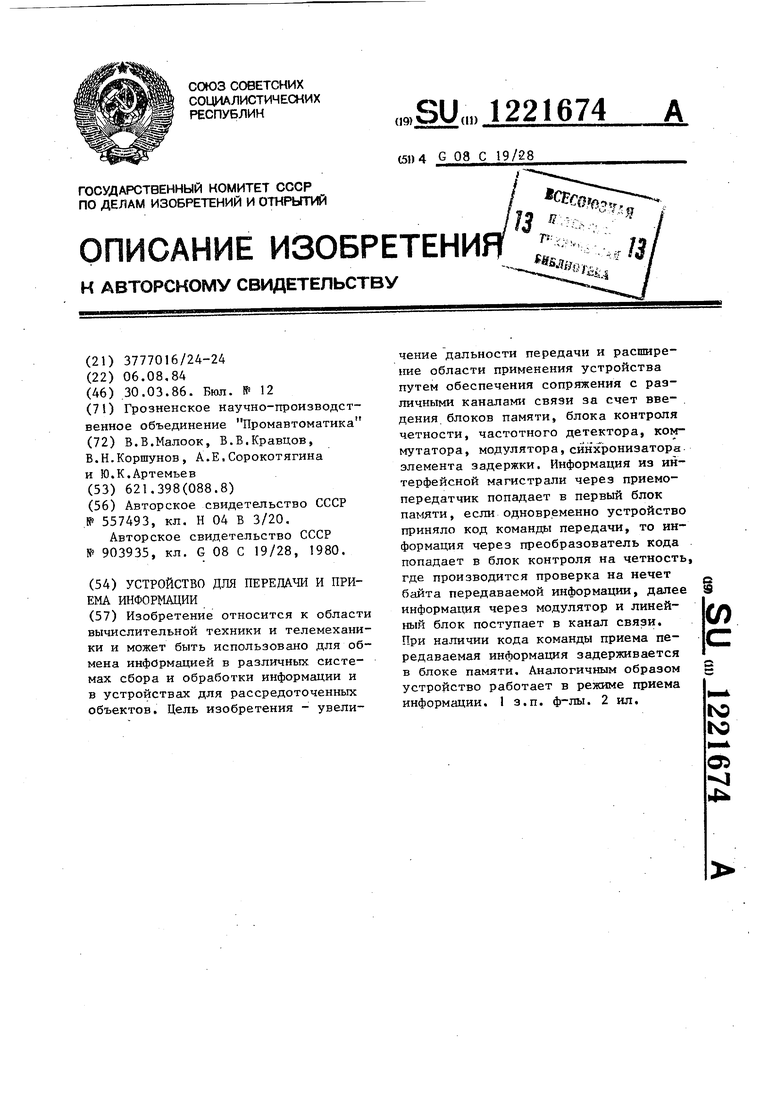

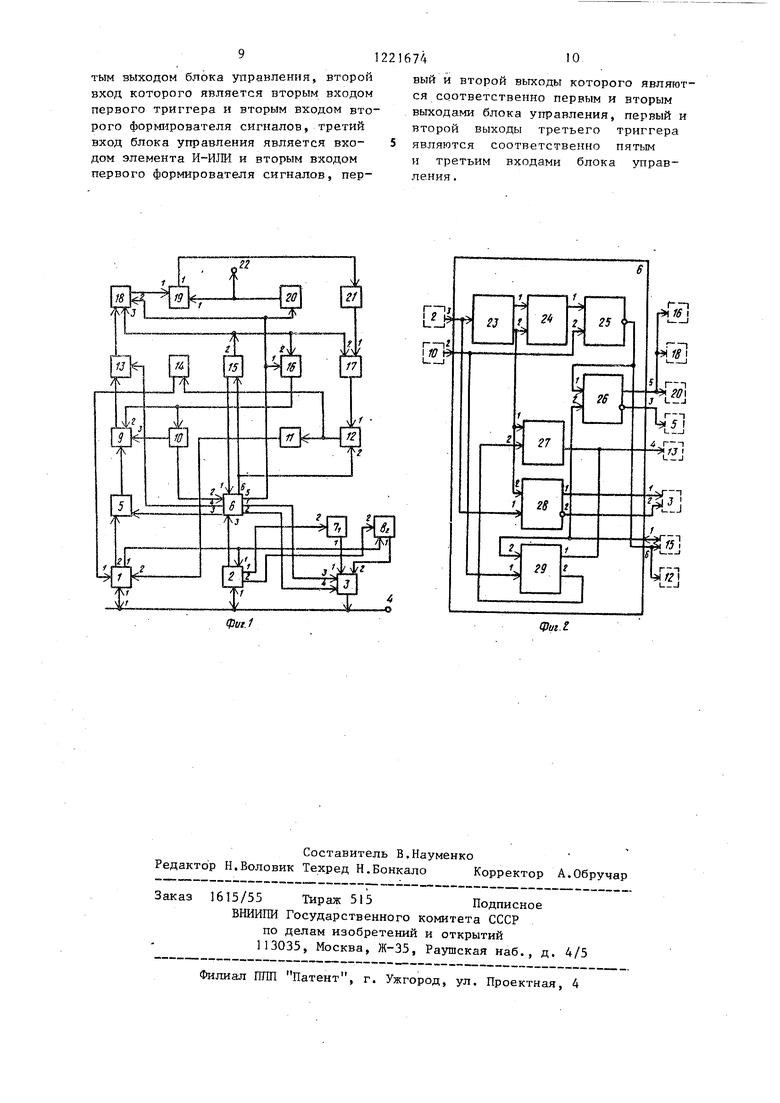

На фиг.2 показаны связи блока 6 управления с дешифратором 2 команд, блоком 3 запроса, блоком 5 памяти, таймером 10, преобразователем 12 кода, блоком 13 контроля четности, генератором 15, элементом 16 задержки, модулятором 18, коммутатором 20.

Блок управления 6 содержит эле- мент И-ИЛИ 23, элемент И 24, первый - третий триггеры 25 - 27, первый и второй формирователи 28 и 29.

Блок 6 управления по командам, принимаемым с дешифратора 2 команд и сигналам разрешения, принимаемым с выхода таймера 10, формирует сигналы запроса связи, приема и передачи, поступающие на входы блока 3 запроса, сигнал разрешения загрузки блока 5 памяти данными, выдает в преобразователь 12 кода сигнал разрешения приема данных, а на вход генера744

тора 15 - сигнал, разрешающий поступление на вход блока 6 управления сигналов тактовой частоты, определяющей скорость приема или передачи информации, формирует сигнал, блокирующий работу блока 13 четности при передаче кода старта или разрешающий его работу при передаче данных, формирует сигнал для запуска модулятора 18 и элемента 16 задержки и на вход коммутатора 20 (для подключения предлагаемого устройства к каналу 22 связи) .

Устройство работает в режимах: передача информации в канал 22 связи, прием информации из какала 22 связи, маскирование сигналов запроса связи передачи и запроса связи приема, фор- мируемых в конце каждого цикла соответственно передачи или приема. Число циклов определяется длиной массива информации. Биты информации передаются или принимаются по тактам, из которых состоит каждый цикл.

Режим работы предлагаемого устройства выбирается от внешнего управляющего устройства, подключенного к интерфейсной магистрали 4, дешифратором 2 команд в соответствии с адресным словом, поступающим через приемопередатчик 1 .

Передача информации подразделяется на предачу кода старта и передачу данных в канал 22 связи.

Дешифратор 2 команд, приняв от интерфейсной магистрали 4 адресное слово кода старта и : правляюшзнй сигнал на занесение команды, вьздает на вход блока 6 управления сигнал разрешения передачи кода старта, по которому блок 6 управления при наличии сигнала разрешения с таймера 10 формирует сигнал запроса связи передачи, поступающий на вход блока 3 запроса.

Блок 6 управления вырабатывает сигнал, разрешающий загрузку блока 5 памяти, поступающий от интерфейсной магистрали 4 через приемо-передатчик 1, выдает на генератор 15 сигнал, разрешающий поступление на входы блока 6 управления тактовой частоты, определяющей скорость передачи информации, формирует сигнал, блокирующий работу блока 13 контроля четт ности при передаче кода старта или разрешающий его работу при передаче данных, формирует сигналы для запуска модулятора 18 и элемента 16 задержки и для подключения устройства к каналу 22 связи через коммутатор 20.

Одновременно с формированием так- ТОБОЙ частоты, поступающей через элемент 16 задержки на входы таймера 10 и преобразователь 9 кода, осуществляется перезапись кода старта из блока 5 памяти в преобразователь 9 кода..

Формат передаваемого сообщения содержит девять двоичных разрядов: восемь - информационных и девятьй - разряд защиты по паритету.

В последовательном коде данные с выхода преобразователя 9 кода через блок 13 контроля четности, модулятор 18 и линейный блок 19 вьщаются в канал 22 связи в форме частотных по- сьшок.

при выдаче кода старта блок 13 контроля чётности выдает информацию- из преобразователя 9 кода на модулятор 18, не дополняя ее до нечета.

Передача данных осуществляется аналогично передаче кода старта, блок 13 контроля четности, при этом осуществляют по команде из бяока 6 управления проверку байта передавае- мой информации по паритету и, в случае необходимости, дополняют ее до нечета в девятом разряде сообщения.

Интервальный таймер 10 определяет ,цлительность передачи одного байта информации. По истечении времени, достаточного для прохождения на модулятор 18 восьми бит информации, таймер 10 выдает на блок 6 управления сигнал разрешения формирования запроса связи передачи.

Если за время, достаточное для передачи последних двух бит информации, внешнее устройство не выдает следующий байт информации, то блок 6 управления формирует сигнал сброса на все элементы памяти, снимает сигнал запроса связи передачи и отключае канал 22 связи.

Режим приема информации из канала 22 связи обеспечивается следуняцим образом.

Информация, принятая из канала 22 связи в виде частотных посыпок, поступает через линейный блок 19 на частотный детектор 21, где преобразуется в последовательности двоичных сигналов 5 поступающих на синхронизатор 17. Последний формирует соответственно принятой скорости обмена информацией такты, синхронизированные относительно принимаемых сигналов, и со сдвигом в 1,5 такта вьщает в последовательном коде в преобразователь 12 кода всю принимаемую информацию. После приема байта информации осуществляется перезапись содержимого преобразователя 12 кода в блок 11 памяти. Одновременно эта информация поступает в блок 14 контроля кода, где она проверяется на соответствие принятым кодовым комбинациям, например, на нечет числа бит и на совпадение байтов (повтор). При выявлении ошибки блок 14 контроля кода выдает на приемо-передатчик 1 сигнал, запрещающий выдачу информации в интерфейсную магистраль 4.

По окончании приема байта информации в блок 11 памяти, блок 6 управления формирует сигнал запроса связи приема, поступающий на вход блока 3 запроса.

Выдача сигнала запроса связи приема, маскируемого триггером 7, через блок 3 запроса в интерфейсную магистраль 4, является окончанием цикла приема очередного байта информации.

Принятый байт информации выдается в интерфейсную магистраль 4 через приемо-передатчик 1 при обращении внешнего управляющего устройства к предложенному устройству.

По следующему обр.ащению через интерфейсную магистраль 4 внешнего управляющего устройства производится опрос и выдача в интерфейсную магистраль 4 (через приемо-передатчик I) кода слова состояния, которое включает признаки: установления синхрониз-. ма, перехода устройства из режима приема в режим передачи, выхода устройства в канал 22 связи, наличия ошибки в информационном байте, наличия сигнала в канапе связи в пределах установленного уровня приема, маскирования сигнала запроса связи приема, маскирования сигнала запроса связи передачи.

После анализа кода слова состояния внешним управляющим устройством цикл связи может быть повторен.

В режиме маскирования сигналов запросов связи передачи или приема дешифратор 2 команд определяет адрес соответствующих триггеров 7 или 8,

после чего через интерфейсную магистраль 4 и прйемо-передатчик 1 производится снятие маски приема или передачи (установка триггеров 7 и 8 в о) и соответствующий сигнал за- проса связи приема или передачи выдается в интерфейсную магистраль 4.

Формула изобретения

1. Устройство для передачи и приема информации, содержащее приемопередатчик , вход-выход которого соединен с интерфейсной магистралью, первый выход приемопередатчика под- ключен к первому входу первого триггера, первому :входу второго триггера и первому входу дещифратора команд, вход-выход которого подключен к интерфейсной магистрали, первый выход дешифратора команд -подключен к второму входу первого триггера, выход которого подключен к первому входу блока запроса, выход которого подключен к интерфейсной магистрали,- второй выход дешифратора команд подключен к второму входу второго триггера, выход которого соединен с вторым входом блока запроса, первый преобразователь кода, линейный блок, вход-выход которого соединен с каналом связи, второй преобразователь кода, блок контроля кода, выход которого соединен с первым входом приемопередатчика, отличающее- с я тем, что, с целью увеличения дальности передачи и расщирения области применения устройства путем . обеспечения сопряжения с разлишйзгми каналами связи, в него введены первый блок памяти, второй блок памяти, блок управления, таймер, лок контроля четности, генератор, элемент задержки, синхронизатор, частотный детектор, коммутатор, модулятор, вы- ход которого соединен с первым входом линейного блока, первый выход которого соединен с входом частотного детектора, выход которого соедиг- нен с первым входом синхронизатора, выход которого соединен с первым входом первого преобразователя кода, выход которого соединен с входом первого блокапамяти и входом блока контроля кода, выход первого блока памяти соединен с вторым входом приемопередатчика, второй выход которог соединен с первым входом второго блока памяти, выход которого соединен с первым входом второго преобразователя кода, выход которого соединен с первым входом блока контроля четности, выход которого соединен с первым входом модулятора, первый и второй выходы блока управления соединены соответственно с третьим и четвертым входами блока запроса, третий выход блока управления соединен с вторым входом второго блока памяти, четвертый выход блока управления соединен с вторым входом блока контроля четности, пятый выход блока управления соединен с первым входом элемента задержки, входом коммутатора и вторы входом модулятора, шестой выход блока управления соединен с вторым входом первого преобразователя кода и входом генератора, первый выход генератора и выход элемента задержки соединены с первым входом блока управления, входом таймера и вторым входо второго преобразователя кода, второй йыход генератора соединен с третьим входом модулятора, вторыми входами синхронизатора и элемента задержки, первый выход таймера соединен с третьим входом второго преобразователя кода, второй выход таймера соединен с вторым входом блока ущ5явления, третий вьпсод дешифратора соединен с третьим входом блока управления, выход коммутатора соединен с каналом связи.

2. Устройство по П.1, о т л и - чающееся тем, что блок управления содержит элемент И-ИЛИ, элемент И, первый, второй и третий, триггеры, первый и второй формирователи сигналов, первый выход элемента И-ЙДИ соединен с первым входом элемента И, выход которого соединен с первым входом первого триггера, второй выход элемента И-ИЛИ соединен с вторым входом элемента И и первыми входами второго триггера и первого формирователя сигналов, выход первого триггера соединен с первым входом третьего триггера и является, шестым выходом блока управления, первый вход которого является вторым входом третьего триггера и первым входом второго формирователя сигналов, первый выход которого соедршен с вторым входом второго триггера, выход которого объединен с вторым входом второго формирователя сигналов и является четвер9

тым выходом блока управления, второй вход которого является вторым вкодом первого триггера и вторым входом второго формирователя сигналов, третий вход блока управления является входом элемента И-ИЛИ и вторым входом первого формирователя сигналов, пер

74

0

вый и второй выходы которого являются соответственно первым и вторым выходами блока управления, первый и второй выходы третьего триггера являются соответственно пятым и третьим входами блока управления .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными | 1988 |

|

SU1599863A1 |

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

| Система коммутации вычислительных устройств,устройство коммутации связи и устройство сопряжения | 1984 |

|

SU1180915A1 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Устройство для контроля магистралей электронных вычислительных машин | 1981 |

|

SU964648A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Устройство для обмена данными | 1989 |

|

SU1700562A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

Изобретение относится к области вычислительной техники и телемеханики и может быть использовано для обмена информацией в различных системах сбора и обработки информации и в устройствах для рассредоточенных объектов. Цель изобретения - увеличение дальности передачи и расширение области применения устройства путем обеспечения сопряжения с различными каналами связи за счет вве- . дения блоков памяти, блока контроля четности, частотного детектора, коммутатора, модулятора,синхронизатора элемента задержки. Информация из интерфейсной магистрали через приемопередатчик попадает в первый блок памяти, если одновременно устройство приняло код команды передачи, то информация через преобразователь кода попадает в блок контроля на четность, где производится проверка на нечет байта передаваемой информации, далее информация через модулятор и линейный блок поступает в канал связи. При наличии кода команды приема передаваемая информация задерживается в блоке памяти. Аналогичным образом устройство работает в режиме приема информации, 1 з,п, ф-лы. 2 ил. (Л to 1C ЦтЛ 05 4;:а

фм./

Щиг.1

| Устройство для приема и передачи информации | 1974 |

|

SU557493A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для передачи и приема информации | 1980 |

|

SU903935A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1986-03-30—Публикация

1984-08-06—Подача