СО

СО

о |С

4

Изобретение относится к импульсной технике и может быть использовано при построении хронизаторов, цифровых синтезаторов частоты, электромузыкальных инстрзжентов.

Цель изобретения - повышение коэффициента деления при сохранении синхронного режима работы.

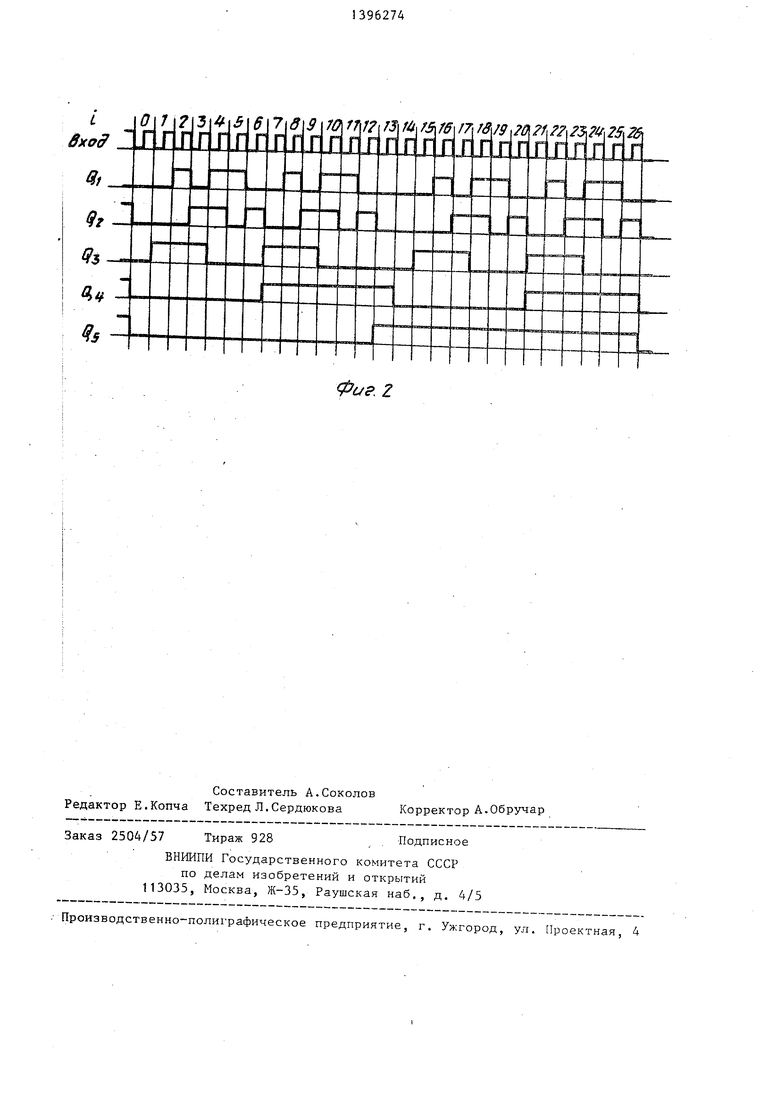

На фиг.1 приведена электрическая функциональная схема синхронного лителя частоты; на фиг.2 - временные диаграммы, поясняющие его работу.

Синхронный делитель частоты содержит первый 1, второй 2, третий 3, 5 ия (такта) синхронного делителя час20

30

35

четвертый 4, и пятый 5 1К-триггеры, первьй 6, второй 7, третий 8 и четвертый 9 элементы И. С- и R-входы всех 1К-триггеров 1 - 5 соединены со- отв.етственно с входной шиной 10 и с шиной 11 сброса. Первые входы первого 6, второго 7, третьего 8 и четвертого 9 элементов И соединены с инверсным выходом первого 1К-тригге- ,ра 1, К-БХОД которого соединен с ин- 25 вареным выходом второго 1К-триггера 2, 1-вход - С- прямым выходом третьего 1К-триггера 3, прямой выход - с 1-входоМ BTOiioro 1К-триггера 2. I- и К-входы пятого 1К-триггера 5 соединены с выходом первого элемента И 6, второй вход которого соединён с прямым выходом четвертого 1К-триг- гёра 4, третий вход - с вторыми входами второго 7 и третьего 8 элементов И, с инверсным выходом третьего 1К-триггера 3 и с К-входом второго 1К-триггера 2, прямой выход которого соединен с четвертым входом первого элемента И 6, с третьим входом второ- 40 го элемента И 7, выход которого подключен к 1-входу четвертого 1К-триг- гера 4, и с К-входом третьего IK- триггера 3, 1-вход которого соединен с выходом четвертого элемента И 9, второй вход которого соединен с инверсным :выходом четвертого 1К-триг- гера 4. Прямой выход пятого 1К-триг- гера 5 соединен с третьим входом третьего элемента И 8, выход которого соединен с К-входом четвертого 1К-триггера 4.

При указанной схеме соединения элементов синхронного делителя частоты логические уравнения для I- и К-входов всех 1К-триггеров 1 - 5 еле дующие:

1, QJ; Ii Q,; Ir

45

50

.-55

тоты и порядковый номер входного импульса на шине 10; Q.- сигнал на прямом выходе j-ro 1К-триггера, где j 1,2,...,5.

Работа синхронного делителя частоты полностью описывается логическими уравнениями для I- и К-входов IK- триггеров 1-5.

По сигналу Сброс, поступающему по шине 1 1 , 1К--триггеры 1 - 5 устанавливаются в исходное (нулевое) состояние, после чего состояния выходов (фиг.2, при равны

Q, 0; q 0; Q 3 0; Q 0;

Qr ОНа основании логических уравнений для I- и К-входов 1К-триггеров 1 - 5 синхронного делителя частоты состояния I- и К-входов следзтощив:

1 Q о; 1, Q, 0; 1., Q, 14 Q,Q7Q3 Oi 15 Q.Q.Q3Q4 OK, Qj 1; K Q3 1; Кз Q., 0;

KI Q,Q3Qr 0; Kj QiQiQjQ o.

Поскольку IK-триггер no последующему входному импульсу на шине 10 при I О и К О не изменяет своего состояния, при I I и К I переключается в противоположное состояние, при и К О переключается в состояние 1, а при I О и К 1 в состояние О, то по первому входному импульсу (по первому отрицатель- ному перепаду сигнала), поступившему по шине 10 после окончания действия сигнала Сброс, 1К-триггер 3 переключается в состояние 1, а осталь-, ные 1К-триггеры 1,2,4 и 5 не изменяют своего состояния (фиг.2, при

14 Q;QiQ3; 1у QiQiQ3Q4; К, Q,; K QJ; Кз Q,;

К4 Q,Q3Q5; к,, Q,.

где индексы у буквенных обозначений соответствуют номеру 1К-триггера, а Q и Q обозначают сигнал соответственно на прямом и инверсном выходах 1К-триггера.

На фиг.2 обозначены вход - входной сигнал (входные импульсы ) на шине 10; i - порядковый номер состоя20

30

35

2540

45

50

55

тоты и порядковый номер входного импульса на шине 10; Q.- сигнал на прямом выходе j-ro 1К-триггера, где j 1,2,...,5.

Работа синхронного делителя частоты полностью описывается логическими уравнениями для I- и К-входов IK- триггеров 1-5.

По сигналу Сброс, поступающему по шине 1 1 , 1К--триггеры 1 - 5 устанавливаются в исходное (нулевое) состояние, после чего состояния выходов (фиг.2, при равны

Q, 0; q 0; Q 3 0; Q 0;

Qr ОНа основании логических уравнений для I- и К-входов 1К-триггеров 1 - 5 синхронного делителя частоты состояния I- и К-входов следзтощив:

1 Q о; 1, Q, 0; 1., Q, 14 Q,Q7Q3 Oi 15 Q.Q.Q3Q4 OK, Qj 1; K Q3 1; Кз Q., 0;

KI Q,Q3Qr 0; Kj QiQiQjQ o.

Поскольку IK-триггер no последующему входному импульсу на шине 10 при I О и К О не изменяет своего состояния, при I I и К I переключается в противоположное состояние, при и К О переключается в состояние 1, а при I О и К 1 в состояние О, то по первому входному импульсу (по первому отрицатель- ному перепаду сигнала), поступившему по шине 10 после окончания действия сигнала Сброс, 1К-триггер 3 переключается в состояние 1, а осталь-, ные 1К-триггеры 1,2,4 и 5 не изменяют своего состояния (фиг.2, при

i 1). При этом состояния выходов становятся равны

Q-, 0; q Изменяются

0; Q I; р4 o;Qr ои состояния входов:

1,

1; 12 0; 1, I; 1 0; I,

1-3-

К, 1; KI 0; Кз 0; К 0; Kg В результате по второму входному импульсу (второму такту) устройство переходит в свое второе состояние (фиг.2, при i 2).,. которое характеризуется следующими значениями выходов и входов 1К-триггеров 1 - 5. (j; 1; Q 0; Q3 1; Q

К1; I 1; 1з 0; I4 1; К2 0; Kj 0;.К4

0;Q5

o;is

0;K5

Рассматривая и далее таким же об-- разом работу синхронного делителя частоты, получим все состояния входов и выходов каждого 1К-триггера 1-5 при всех 1.

В двенадцатом такте Qj становится равной Q 1 (фиг.2, при i 12), а в двадцать седьмом все 1К-триггеры возвращаются в исходное нулевое состояние .

Q-, 0; Q 0; q 0; Q, 0.

Ha этом заканчивается цикл работы синхронного делителя частоты. Далее его работа повторяется через каждые Двадцать семь входных.импульсов. Формула изо брётения

Синхронный делитель частоты, содержащий первый, второй, третий, чет

вертый и пятый 1К-триггеры, С- и R-входы которых соединены соответственно с входной шиной и шиной сброса, первый элемент И, выход которого соединен с I- и К-входами пятого 1К-триггера, второй элемент И, выход которого соединен с 1-входом четвертого 1К-триггера, К-вход кото10 рого соединен с выходом третьего

элемента И, первый и второй входы которого соединены с инверсными выходами соответственно первого и третьего 1К-триггеров, отличающий15 с я тем, что, с целью повьшения коэффициента деления, в него введен чет- вертьА элемент И, выход которого соединен с 1-входом третьего 1К-тригге- ра, первый вход - с инверсным выхо20 дом первого ХК-триггер а и с первыми входами первого и второго элементов И, второй вход - с инверсным, выходом четвертого 1К-триггера, прямой выход которого соединен с вторым входом пер25 вого элемента И, третий вход которого соединен с вторым входом третьего элемента И, третий вход которого подключен к прямому выходу пятого IK- триггера, с вторым входом второго эле30 мента И и с К-входом второго 1К-триг- гера, 1-вход которого соединен с прямым выходом первого 1К-триггера, пря- :мой выход с четвертым входом первого элемента И, с третьим входом

35 второго элемента И и К-входом третьего 1К-триггера, прямой выход которо; го соединен с 1-входом первого IK- триггера, К-вход которого соединен с инверсным выходом второго 1К-триггера.

Фиг. Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты | 1986 |

|

SU1396275A1 |

| Синхронный делитель частоты на 17 | 1985 |

|

SU1285593A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Синхронный делитель частоты на 14 | 1986 |

|

SU1368983A1 |

| Синхронный делитель частоты на 10 | 1985 |

|

SU1338061A1 |

| Делитель частоты на 19 | 1984 |

|

SU1226660A1 |

| Синхронный делитель частоты | 1986 |

|

SU1429317A1 |

| Синхронный делитель частоты на 10 | 1984 |

|

SU1225009A1 |

| Синхронный делитель частоты на 12 | 1984 |

|

SU1221747A1 |

| Синхронный делитель частоты на 18 | 1985 |

|

SU1274152A1 |

Изобретение относится к импульсной технике и может быть использовано при построении хронизаторов, цифровых синтезаторов частоты и элект- ромузыкаль.ньгх инструментов. Целью изобретения является увеличения коэффициента деления при сохранении синхронного режима работы. Синхронный делитель частоты содержит IK- триггеры 1-5, элементы И 6-9, входную шину 10, шину 11 сброса. Работа синхронного делителя частоты описывается логическими уравнениями для I- и К-входов 1К-триггеров 1-5 и по- ясняется временными диаграммами, приведенными в описании изобретения. 2 ил. С «б

| Делитель частоты на 19 | 1984 |

|

SU1226660A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| и др | |||

| Микроэлектронные схемы цифровых устройств, М.: Сов.радио, 1975, с.192, рис.5.32 | |||

| Синхронный делитель частоты | 1986 |

|

SU1322470A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-05-15—Публикация

1986-07-23—Подача