Изобретение относится к приборостроению, средствам автоматики и вычислительной техники и может быть использовано в цифровых системах программного управления, которые содержат преобразователи угол-код, в которых задание текущего значения регулируемой величины осуществляетс абсолютными значениями„

Цель изобретения - упрощение устройства.

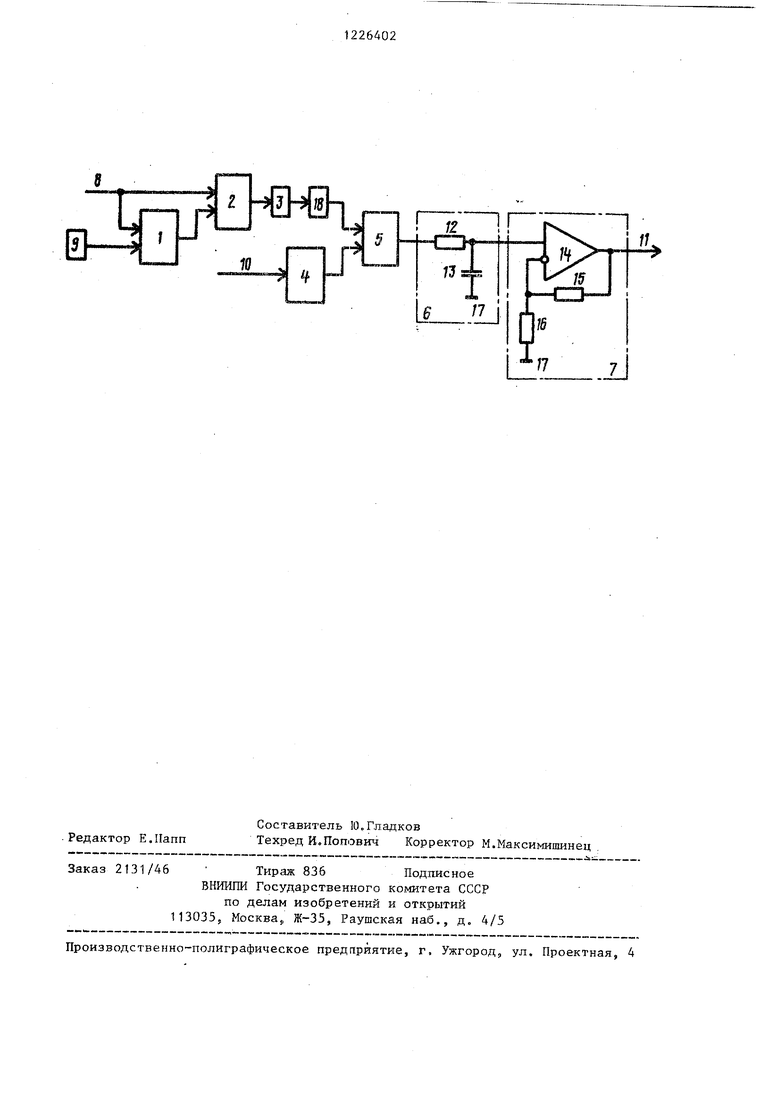

На чертеже представлена принципиальная схема устройства.

Устройство содержит регистр 1 памяти, сумматор 2, элемент УШИ 3, дешифратор 4, элемент И 5, преобразователь 6 частота-напряжение, усилитель 7, первый вход 8 устройства5 тактирующий генератор 9, второй вход 10 и выход 11 устройства, ограничительный элемент 12, конденсатор 13, операционный „усилитель 14, резисторы 15 и 16, общую шину 17, элемент НЕ 18.

Преобразователь частота-напряжение 6 содержит ограничительный элемент 125 конденсатор 13 и общую ШИНУ 17,.

Усилитель 7 содержит операцион- ньй усилитель 14 резисторы 15 и 16 и общую шину 17.

Устройство работает следующим образом, ,

При подгслючении устройства к преобразователю регулируемая величина - код, например к преобразователю уго код, выход которого соединен с информационным входом регистра 1 памяти, информация в котором обновляется с частотой f , поступающей на управляющий вход регистра памяти с выхода тактирующего генератора 9.

Допустим, что максимально возможное изменение регулируемой величины за период 1/f может быть записано и разрядами двоичного кода Тогда частота изменения состояния. (h + 1)-го разряда регистра двйично го счетчика преобразователя угол-ко пропорциональна скорости изменения регулируемой вепичины и определяется выражением:

Д

fQ,

где &Q. приращение кода преобразователя угол-код за период частоты „ f

5

0

5

емкость h -разрядного двоичного счетчика преобраз ова- теля угол-код , частота сигнала на выходе тактирующего генератора 9. .Для формирования импульса длительностью 1/{ на выходе элемента НЕ 18 при изменении состояния ( + 1)-го разряда двоичного счетчика преобразователя угол-код вход 8 устройства подключается к выходу (П + 1)-го разряда двоичного счетчика преобра- | зовате,г1я угол-код. При этом на первый вход сумматора 2 поступает информация о текущем состоянии (h+1)-ro разряда двоичного счетчика преобразователя угол-код, а на второй - информация об инверсном состоянии (h + 1.)-го разряда двоичного счетчика преобразователя угол-код, .задержанная на период сигнала частоты f Если состояние (h + 1)-го разряда двоичного счетчика преобразователя -угол-код не изменяется за указанный период, т,е. текущая информация равна задержанной на период информации, то на выходе элемента НЕ 18 форми0

5

5

5

0

если

руется логический сигнал изменяется, то 1

Импульсы напряжения частотой f гфойдя через элемент И 5, поступают па вход преобразователя 6 частота- напряжение, выполненного, например, в виде ф1-шьтра нижних частот5 постоянное напряжение с выхода которого згсилнвается усилителем 7 и поступает на вход устройства 11, нулевой зфо- вень которого должен быть установлен дополнительно введенными цепями коррекции, если в качестве элемента И 5 применена серийная малая интегральная схема, напряжение на выходе которой при сигнале О отлично от нуля.

Напряжение с выхода 11, в общем случае, суммируется с напряжением., пропорциональным рассогласованию между заданным и фактическим значениями регулируемой величины, и является управляющим воздействием для регулируемой величины, несколько ,превышающим значение, достаточное . для поддержания заданной скорости изменения регулируемой величины.

Код, пропорциональный рассогласованию между заданным и фактическим знaчeния п{ регулируемой величины, поступает на вход 10 и при его уменьшении до наперед заданной величины

3

на выходе дешифратора 4 и, соответственно, э лемента И 5 устанавливается сигнал О, что приводит к уменьшению напряжения на выходе 11 и увеличению рассогласования.

Назначение дешифратора 4 - выклю чение импульсного напряжения на выходе преобразователя 6 частоты-нап- ряжение при рассогласовании меньшем допустимого, т.е. если код допустимо го рассогласования равен 010, то при кодах 001.и 000 на выходах дешифратора 4 и элемента И 5 соответст венно, на вход преобразователя 6 частота-напряжение поступает сигнал О. Величина скоростного сигнала с постоянной времени интегрирующей цепи начинает уменьшаться и рассогласование вновь увеличивается до кода 010. Реализован дешифратор 4 на ИМС К561 И112, на входы А которых подается код с ПКК, и на входах Б набирается с помош;ью перемычек код допустимого рассогласования.

Схема дешифратора 4 несколько усложняется, если ПКН построить на ЦАП К572 ПА2 (при двоичных кодах), так как возникает необходимость устанавливать код допустимого рассогласования как в области положительных, так и в области отрицательных его значений.

При двоичном коде на выходе преобразователя угол-код регистр 1 памяти представляет собой D-триггер а сумматор 2 и элементы ИЛИ 3, НЕ 18 - элемент ИСКЛЮЧАЮЩЕЕ ИЛИ.

Сказанное .справедливо и для двоично-десятичного кода 1248, если Q - 10,100 ... В этом случае вход 8 устройства подключается к выходу младшего разряда одной из декад преобразователя угол-код. Если же требуется иметь Qr 20,200..., то к

264024

входу 8 устройства подключаются Т, 3 и 4 разряды декады преобразователя угол-код, т.е. регистр 1 памяти и сумматор 2 должны быть трехразряд- 5 ными. Получение других значений Q, при двоично-десятичном коде 1248 затруднено.

Предлагаемое вьшолнение устройства для формирования сигнала, про- 10 порционального скорости, позволяет

существенно его упростить, и за счет этого снизить стоимость и существенно повысить его надежность.

15 Формула изобретения

Устройство для формирования сигнала, пропорционального скорости, содержащее регистр памяти, сумматор,

20 тактирующий генератор, элементы ИЛИ, НЕ, И и ограничительный элемент, соединенньй первым вьшодом с входом усилителя, выход которого является выходом устройства, отличаю25 щ е е с я тем, что, с целью упрощения устройства, в нем установлен дешифратор и конденсатор, первая обкладка которого заземлена, а вторая соединена с первым выводом огра,,, ничительного элемента, подключенного вторым выводом к выходу элемента И, соединенного первым входом с выходом дешифратора, а вторым входом через элемент НЕ - с выходом элеМен- та ИЛИ, подключенного входом к вы ходу сумматора, соединенного первьпч и вторым входами, соответственно, с информационным входом и выходом регистра памяти, подключенного yrtpaB- ляющим входом к выходу тактирующего, генератора, а информационный вход регистра памяти и вход дешифратора являются первым и вторым входами устройства.

40

Редактор Е.Папп

Составитель Ю.Гладков

Техред Й.Попович Корректор М.Максимишинец

2131/46

Тираж 836 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва,, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Ll jJ

.. II.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Автоматический цифровой измеритель коэффициента гармоник | 1980 |

|

SU911363A1 |

| Генератор ступенчатого напряжения | 1986 |

|

SU1330734A1 |

| Устройство для моделирования случайных блужданий | 1981 |

|

SU999063A1 |

| Система управления вибростендом | 1984 |

|

SU1259224A2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Устройство формирования много-СТупЕНчАТОгО КВАзиСиНуСОидАльНОгОТРЕХфАзНОгО НАпРяжЕНия | 1978 |

|

SU809437A1 |

| Калибратор переменного напряжения | 1983 |

|

SU1115031A1 |

Изобретение относится к области приборостроения, средств автоматики и вычислительной техники и может быть использовано в цифровых системах программного управления, которые содержат преобразователи угол- код и в которых задание текущего значения регулируемой величины осу- ществляется абсолютными значениями, В данном случае решается задача конструктивного упрощения устройства и обеспечения его функционирования в случае представления задающего воздействия в параллельном коде. Выходной сигнал преобразователя угол-код поступает на первьш вход устройства, т.е. на первый вход сумматора и на информационный вход регистра памяти. Выходной сигнал тактирующего генератора поступает на управляющий вход регистра памяти, В регистре памяти выходной сигнал преобразователя угол-код задерживается на такт квантования. Выходной сигнал регистра памяти поступает на второй вход сумматора, а с его выхода через элементы 1 ШИ и НЕ сигнал поступает на первый вход элемента И, Выходной сигнал измерителя рассогласования поступает на второй вход устройства, т.е. на вход дешифратора. Он анализирует сигнал рассогласования и формирует на своем выходе сигнал разрешения или запрета, которьй поступает на второй вход элемента И. Выходной сигнал элемента И через преобразователь частота-напряжение, например, выполненньш в виде фильтра низких частот, и усилитель, вьшолнеиный, например, на основе операционного усилителя, поступает на выход устройства. 1 ил. i (Л ГчЭ ю О5 4 О Ю

| УСТРОЙСТВО для ПОЛУЧЕНИЯ ПРОИЗВОДНОЙ | 0 |

|

SU408270A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для формирования сигнала, пропорционального скорости | 1977 |

|

SU673981A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-04-23—Публикация

1984-06-07—Подача