Изобретение относится к области вычислительной техники и предназначено для применения в устройствах управления цифровых вычислительных машин с микропрограммным управлением в частности в устройствах управления графическими дисплеями.

Целью изобретения является сокращение оборудования за счет уменьшения объема памяти при многоуровневом ветвлен1-ш.

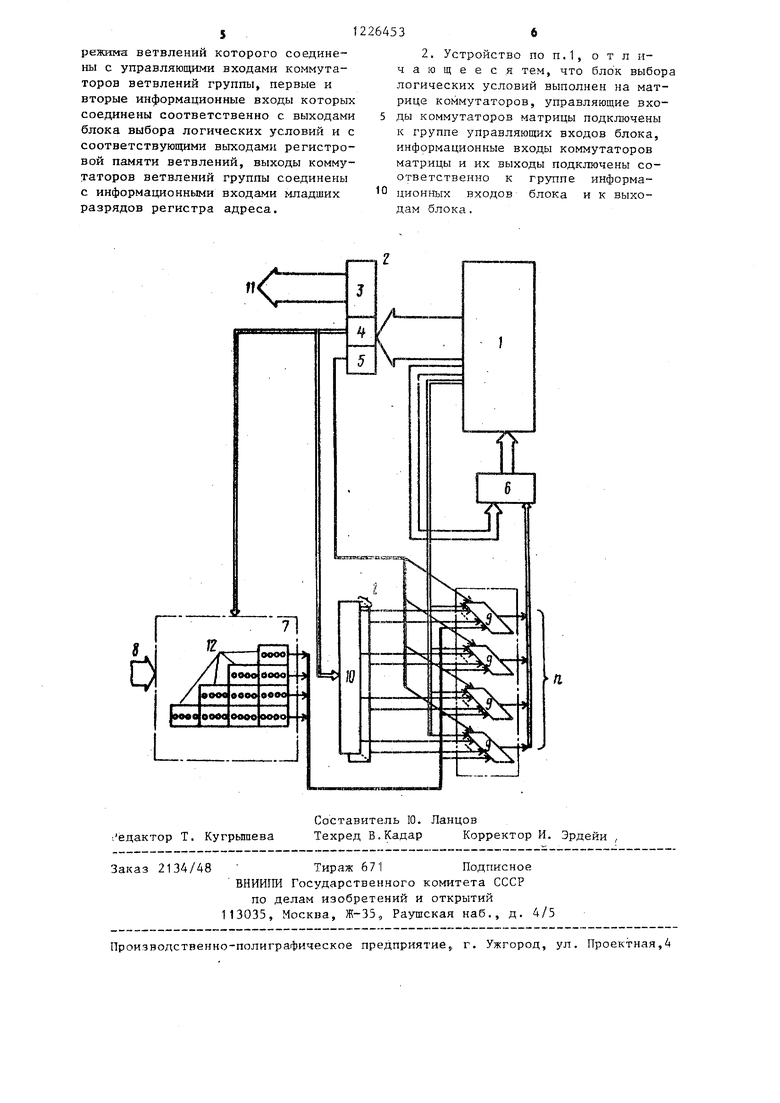

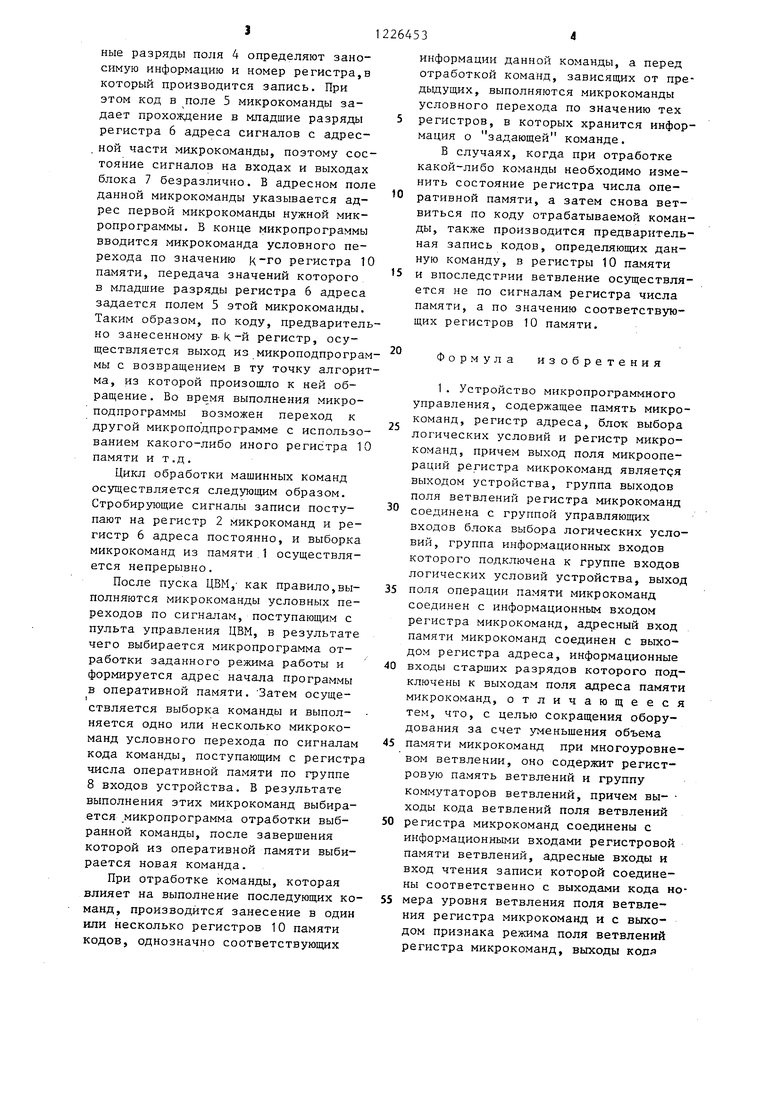

На чертеже приведена структурная схема предлагаемого устройства микропрограммного управления.

Устройство содержит память 1 микрокоманд, регистр 2 микрокоманд,содержащий выход 3 поля микроопераций, выход 4 поля ветвлений и выход 5 кода режима ветвления, регистр 6 адреса, блок 7 выбора логических условий группу 8 входов логических условий, группу коммутаторов 9 ветвлений, регистровую память 10 ветвлений и группу 11 выходов. Блок 7 содержит матрицу коммутаторов 12,

Устройство работает следующим образом.

По группе 8 входов в устройство поступают сигналы, от значения которых зависит алгоритм выполняемых в устройстве микропрограмм. Этими сигналами являются: код операции машинной команды, поступающий с регистра числа оперативной памяти, призна- ки, определяющие результаты выполнения текущей и предьщущих микрокоманд, сигналы состояния процессора, оперативной памяти, внешних устройств, различного спецоборудования, сигналы, поступающие с панели управления ЦВМ,и т.д.

Цикл выполнения микрокоманды осуществляется путем считывания из памяти 1 микрокоманд кода очередной микрокоманды, которая содержит управляющую и адресную части. В адресной части указывается К -разрядный адрес следующей микролооманды,, причем h младших разрядов адреса могут модифицироваться в процессе выполнения микрокоманды, а старшие К-п разрядов адреса поступают непосредственно на регистр 6 адреса. Управляющая часть микрокоманды записывается в регистр 2 микрокоманд, при этом код выхода 3 поля микроопераций регистра 2 поступает на выходы 11 устройства и управляет микрооперациями

в блоках ЦВМ, а выходы 4 и 5 управляют формированием младших разрядов адреса след,уюш;ей микрокоманды.- После завершения формирования

младших разрядов адреса микрокоманды, время которого определяется временем задержки элементов в блоке 7 и в коммутаторах 9,новьй адрес заносится в регистр 6 адреса,Через некоторое время, определяемое задержкой сигналов в памяти 1 микрокоманд, на его выходах появляется код следующей микрокоманды, который снова заносится в регистр 2 микрокоманд ; Занесение в регистры 2 и б осуществляется по сигналам, периодически поступающим с генератора тактовых импульсов (не показан).

При безусловном следовании последовательности микрокоманд в поле 5 микрокоманды задается такой код, при поступлении которого на управляющие входы коммутаторов 9 на их выходы будут передаваться значения младших

разрядов адресной части микрокоманды. Таким образом, адрес следующей микрокоманды будет полностью определяться адресным полем выполняемой микровсоманды.

При необходимости изменения порядка следования микрокоманд в зависимости от значения каких-либо условий в поле 5 микрокоманды задается код, который подключает на

выходы коммутаторов 9 сигналы с выходов блока 7, а в поле 6 - код, под воздействием которого на выход

блока 7 передаются сигналы анализируемых условий, выбранные из множества условий, поступающих по группе 8 входов. Таким образом, адрес следующей микрокоманды определяется в зависимости от значения анализируемых условий.

При необходимости обращения к

микроподпрограмме выполняется микрокоманда, которая заносит в К-и регистр 10 памяти код, однозначно соответствующий той точке алгоритма,

из которой осуществляется переход в микроподпрограмму. Управление записью в регистры ветвления осуществляется кодом в поле 4 микрокоманды, для чего в этом поле выделяется специальный бит, единица в котором вызывает запись в один из регистров (при нулевом его значении состояние регистров не изменяется), а остальные разряды поля 4 определяют заносимую информацию и номер регистра,в который производится запись. При этом код в поле 5 микрокоманды задает прохождение в младшие разряды регистра 6 адреса сигналов с адресной части микрокоманды, поэтому состояние сигналов на входах и выходах блока 7 безразлично. В адресном поле данной микрокоманды указывается адрес первой микрокоманды нужной микропрограммы. В конце микропрограммы вводится микрокоманда условного перехода по значению регистра 10 памяти, передача значений которого в младшие разряды регистра 6 адреса задается полем 5 этой микрокоманды. Таким образом, по коду, предварительно занесенному в-R-и регистр, осуществляется выход из микроподпрограммы с возвращением в ту точку алгоритма, из которой произошло к ней обращение . Во время выполнения микроподпрограммы возможен переход к другой микроподпрограмме с использованием какого-либо иного регистра 10 памяти и т.д.

Цикл обработки машинных команд осуществляется следующим образом. Стробирующие сигналы записи поступают на регистр 2 микрокоманд и регистр 6 адреса постоянно, и выборка микрокоманд из памяти . 1 осуществляется непрерывно.

После пуска ЦВМ,- как правило,выполняются микрокоманды условных переходов по сигналам, поступающим с пульта управления ЦВМ, в результате чего выбирается микропрограмма отработки заданного режима работы и формируется адрес начала программы в оперативной памяти. Затем осуществляется выборка команды и выполняется одно или несколько микрокоманд условного перехода по сигналам кода команды, поступающим с регистр числа оперативной памяти по группе 8 входов устройства. В результате выполнения этих микрокоманд выбирается микропрограмма отработки выбранной команды, после завершения которой из оперативной памяти выбирается новая команда.

При отработке команды, которая влияет на выполнение последующих команд, производится занесение в один или несколько регистров 10 памяти кодов, однозначно соответствующих

информации данной команды, а перед отработкой команд, зависящих от пре- дьщущих, выполняются микрокоманды условного перехода по значению тех

регистров, в которых хранится информация о задающей команде.

В случаях, когда при отработке какой-либо команды необходимо изменить состояние регистра числа оперативной памяти, а затем снова ветвиться по коду отрабатываемой команды, также производится предварительная запись кодов, определяющих данную команду, в регистры 10 памяти

и впоследствии ветвление осуществляется не по сигналам регистра числа памяти, а по значению соответствующих регистров 10 памяти.

20

Формула изобретения

1. Устройство микропрограммного управления, содержащее память микрокоманд, регистр адреса, бло-к выбора логических условий и регистр микрокоманд, причем выход поля микроопераций регистра микрокоманд является выходом устройства, группа выходов поля ветвлений регистра микрокоманд соединена с группой управляющих входов блока выбора логических условий, группа информационных входов которого подключена к группе входов логических условий устройства, выход

поля операции памяти микрокоманд соединен с информационным входом регистра микрокоманд, адресный вход памяти микрокоманд соединен с выходом регистра адреса, информационные

входы старших разрядов которого подключены к выходам поля адреса памяти микрокоманд, отличающееся тем, что, с целью Сокращения оборудования за счет уменьшения объема

памяти микрокоманд при многоуровневом ветвлении, оно содержит регистровую память ветвлений и группу коммутаторов ветвлений, причем вы- ходы кода ветвлений поля ветвлений

регистра микрокоманд соединены с информационными входами регистровой памяти ветвлений, адресные входы и вход чтения записи которой соединены соответственно с выходами кода номера уровня ветвления поля ветвления регистра микрокоманд и с выходом признака режима поля ветвлений регистра микрокоманд, выходы кодя

51

режима ветвлений которого соединены с управляющими входами коммутаторов ветвлений группы, первые и вторые информационные входы которых соединены соответственно с выходами блока выбора логических условий и с соответствующими выходами регистровой памяти ветвлений, выходы коммутаторов ветвлений группы соединены с информационными входами младших разрядов регистра адреса.

264536

2, Устройство по П.1, о т л и- ч а о щ е е с я тем, что блок выбора логических условий выполнен на матрице коммутаторов, управляющие вхо- 5 ды коммутаторов матрицы подключены к группе управляющих входов блока, информационные входы коммутаторов матрицы и их выходы подключены соответственно к группе информационных входов блока и к выходам блока.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управ-лЕНия | 1978 |

|

SU807290A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управ-лЕНия | 1979 |

|

SU842815A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления | 1980 |

|

SU881748A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Микропрограммное устройство управления (его варианты) | 1983 |

|

SU1125625A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Микропроцессор | 1984 |

|

SU1242975A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1183964A1 |

Изобретение относится к области вычислительной техники и предназначено для применения в устройствах управления цифровых вычислительных, машин с микропрограммным управлением, в частности в устройствах управления графическими дисплеями.Цель изобретения - сокращение оборудования за счет уменьшения объема памяти при многоуровневом ветвлении. Цель изобретения достигается за счет введения в устройство регистровой памяти ветвлений и группы коммутаторов ветвлений с соответствующими функциональными связями между ними и известными блоками устройства. 1 з.п. ф-лы, 1 ил. I со N: ю 05 4 сл со

едактор Т. Кугрьшева

Составитель Ю. Ланцов

Техред В.Кадар Корректор И. Эрдейи ,

Заказ 2134/48 Тираж 671 Подписное ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,, г. Ужгород, ул. Проектная,4

| Авторское свидетельство СССР № 669984, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1974 |

|

SU503240A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-05-17—Подача