«1

Изобретение откосится к импульсной технике,

. Цель изобретения - расширение функциональных возможностей за счет получения управляемой временной диаг- раммы выходных сигналов.

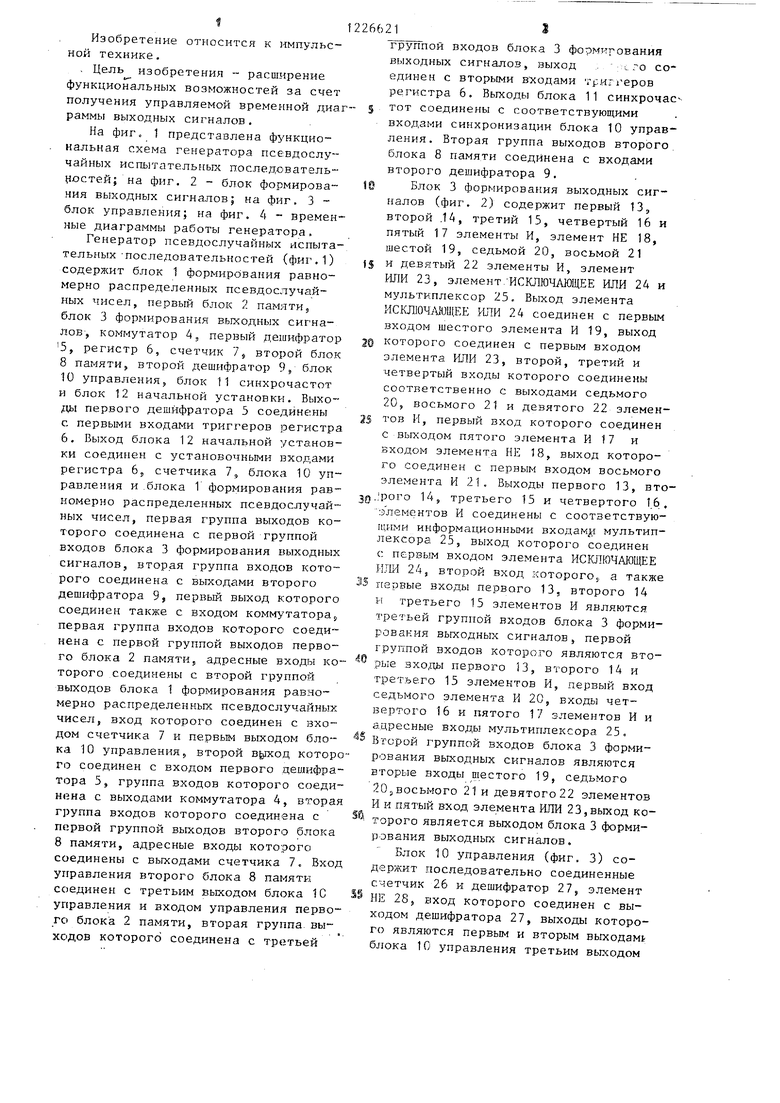

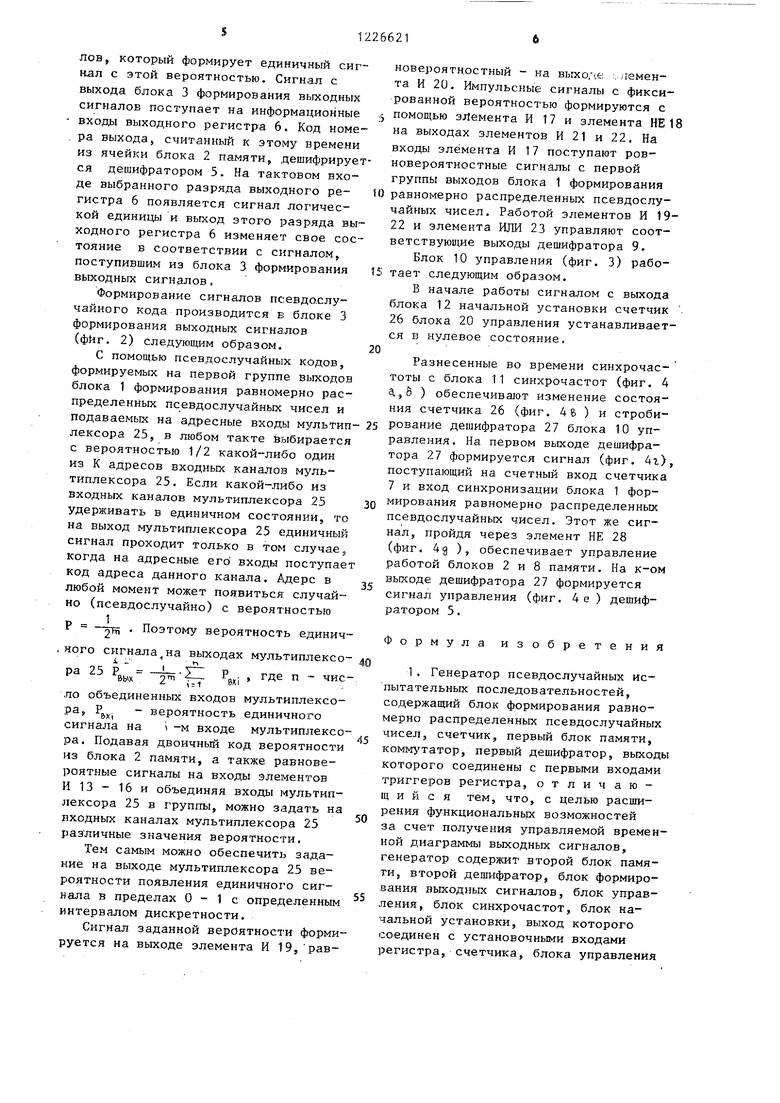

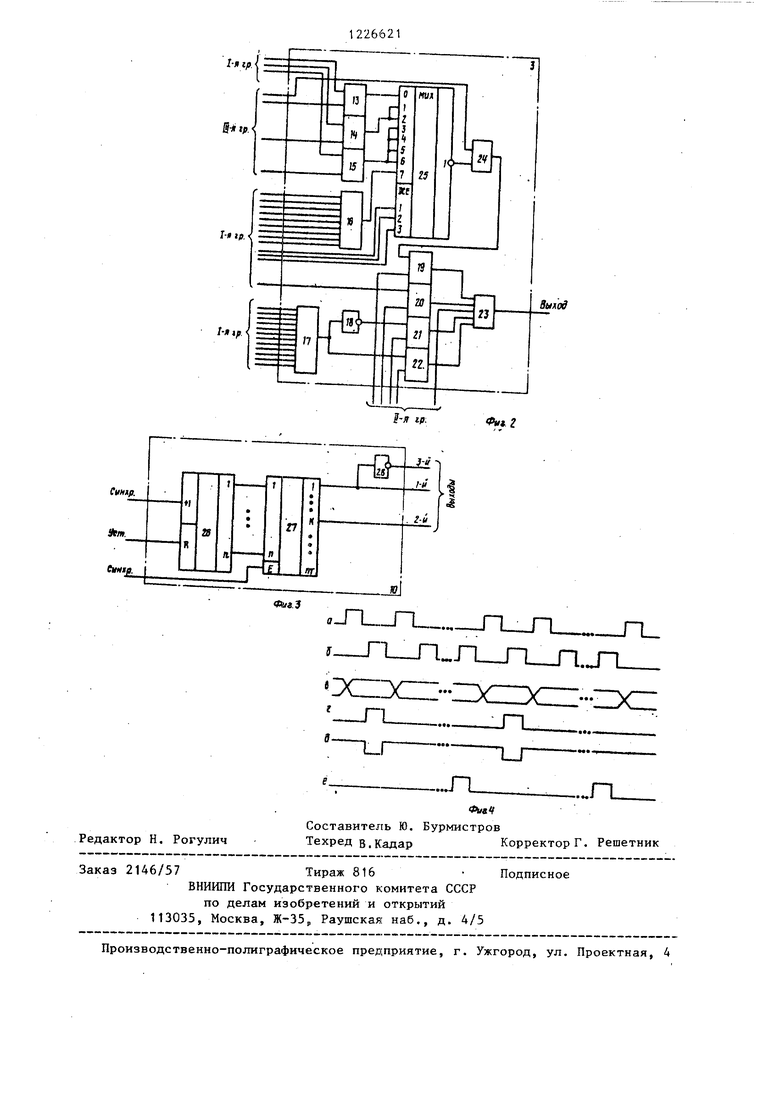

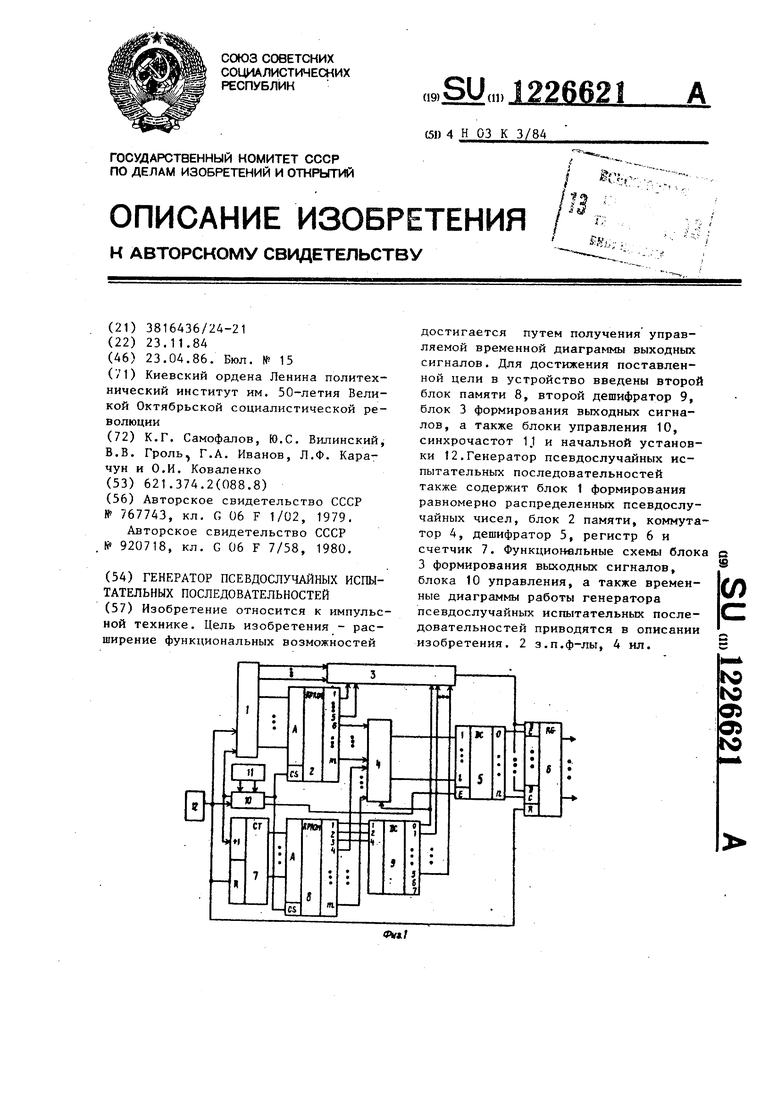

На фиг. 1 представлена функциональная схема генератора псевдослучайных испытательных последователь- ростей; на фиг, 2 - блок формирова- НИН выходных сигналов; на фиг, 3 блок управления; на фиг. 4 - временные диаграммы работы генератора,

Генератор псевдослучайных испытательных последовательностей (фиг,1) содержит блок 1 формирования равномерно распределенных псевдослучайных чисел, первый блок 2 памяти, блок 3 формирования выходных сигналов, коммутатор 45 первый дешифратор 5, регистр 6, счетчик 1 второй блок 8 памяти, второй дешифратор 9,, блок 10 управления,, блок 11 синхрочастот и блок 12 начальной установки. Выходы первого дешифратора 5 соединены с первыми входами триггеров регистра 6, Выход блока 12 начальной установки соединен с установочными входами регистра 6, счетчика 7, блока 10 управления и .блока 1 формирования равномерно распределенных псевдослучайных чисел, первая группа выходов которого соединена с первой грзшпой входов блока 3 формирования выходных сигналов, вторая группа входов которого соединена с выходами второго дешифратора 9, первый выход которого соединен также с входом коммутатораj первая группа входов которого соединена с первой группой выходов первого блока 2 памяти, адресные входы ко торого соединены с второй группой выходов блока 1 формирования равномерно распределенных псевдослучайных чисел, вход которого соединен с входом счетчика 7 и первьм выходом бло- ка 10 управления, второй вукод которго соединен с входом первого дешифратора 5, группа входов которого соединена с выходами коммутатора 4, втора группа входов которого соединена с первой группой выходов второго блока 8 памяти, адресные входы которого соединены с выходами счетчика 7, Вхо управления второго блока 8 памяти соединен с третьим выходом блока 1C управления и входом управления первого блока 2 памяти, вторая группа, выходов которого соединена с третьей

g ft S

0

группой входов блока 3 формкгования выходных сигналов, выход :--го соединен с вторьми входами триггеров регистра 6. Выходы блока 11 синхрочас-- тот соединены с соответствующими входами синхронизации блока 10 управления. Вторая группа выходов второго. блока 8 памяти соединена с входами второго дешифратора 9.

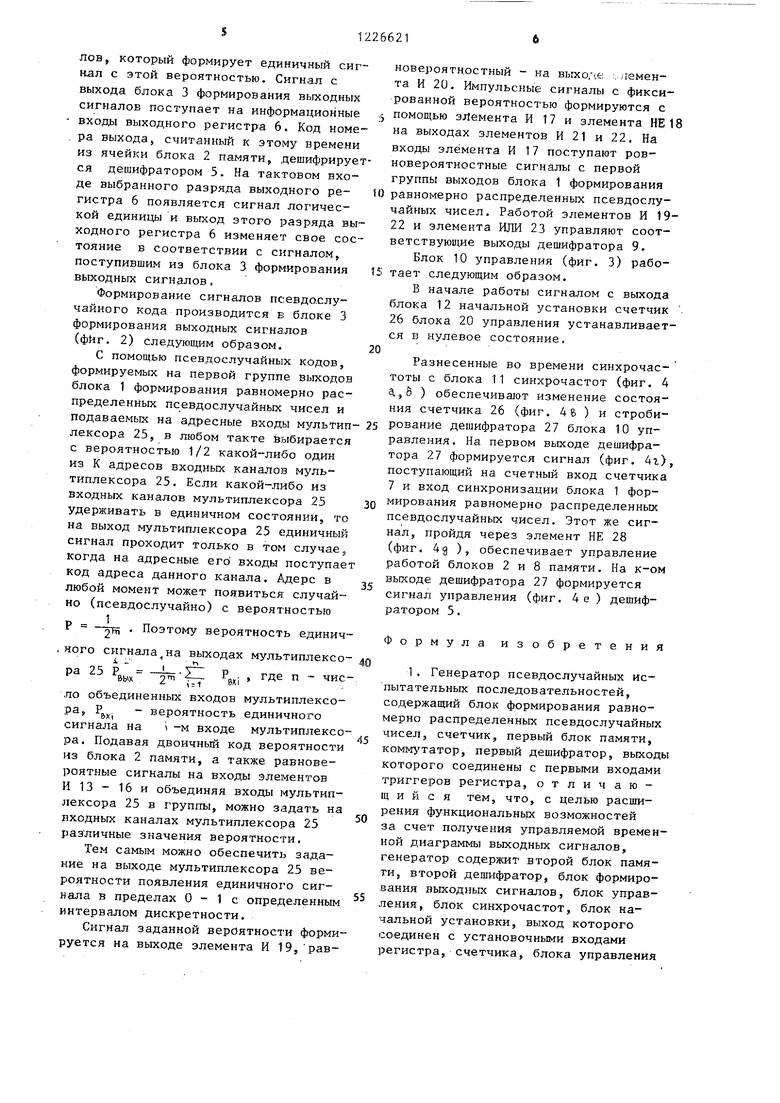

Блок 3 формирования выходных сигналов (фиг. 2) содержит первый 13, второй .14, третий 15, четвертый 16 и пятый 17 элементы И, элемент НЕ 18, шестой 19, седьмой 20, восьмой 21 и девятый 22 элементы И, элемент ИЛИ 23, элемент.-ИСКЛЮЧАЮЩЕЕ ИЛИ 24 и мультиплексор 25. Выход элемента ИСКЛЙЧМЦЕЕ .ИЛИ 24 соединен с первьм входом шестого элемента И 19, выход которого соединен с первым входом з.лемента ИЛИ 23, второй, третий и четвертый входы которого соединены соответственно с выходами седьмого 20, восьмого 21 и девятого 22 элементов И, первый вход которого соединен с выходом пятого элемента И 17 и .входом элемента НЕ 18, выход которого соединен с первым входом восьмого элемента И 21. Выходы первого 13, вто- .;рого 14, третьего 15 и четвертого 1,6, элементов И соединены с соотзетствую- информационными входам и мультиплексора 25, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ И7М 24, второй вход которого а также первые входы первого 13, второго 14 и третьего 15 элементов И являются третьей группой входов блока 3 формирования выходных сигналов, первой группой входов которого являются вторые зхо,цы первого 13, второго 14 и третьего 15 элементов И, первый вход седьмого элемента И 20, входы четвертого 16 и пятого 17 элементов И и ацресные входы мультиплексора 25. Второй группой входов блока 3 формирования выходных сигналов являются вторые входы шестого 19, седьмого 20 восьмого 21 и девятого 22 элементов И и пятый вход элемента ИЛИ 23,выход которого является выходом блока 3 формирования выходных сигналов.

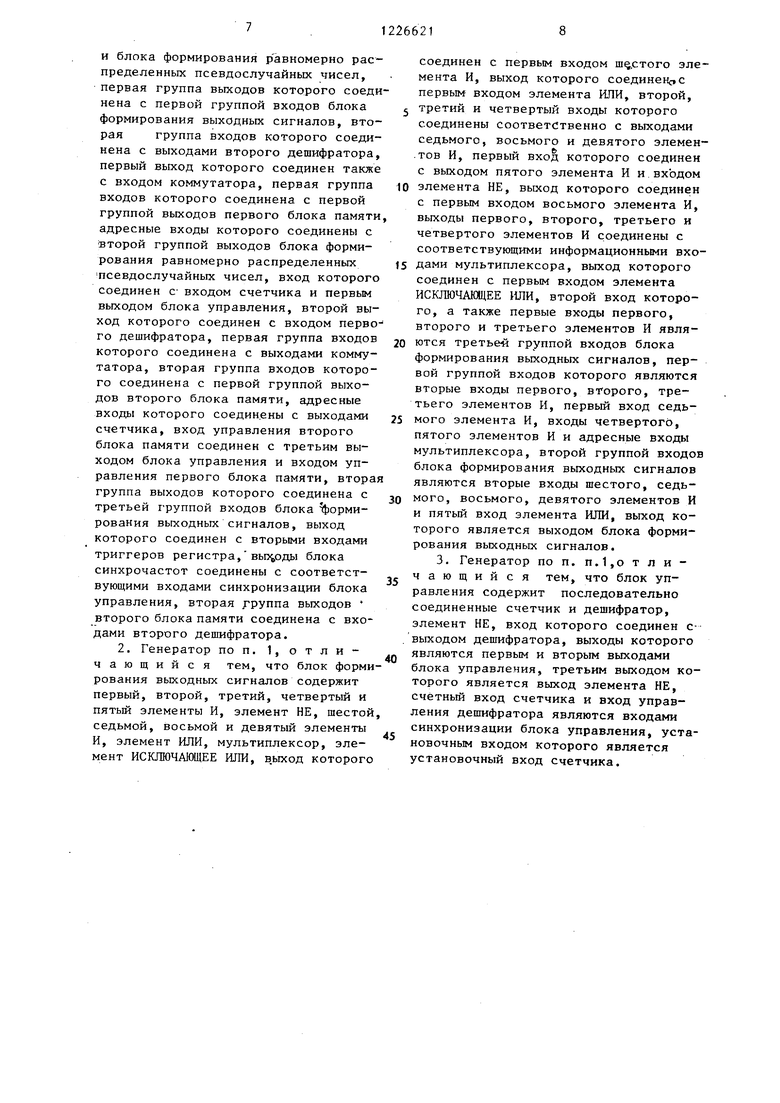

Блок 10 управления (фиг. 3) содержит последовательно соединенные счетчик 26 и дешифратор 27, элемент НЕ 28, вход которого соединен с выходом дешифратора 27, выходы которого являются первым и вторым выходами блока 10 управления третьим выходом

5 которого является выход элемента ,НЕ 28. Счетньш вход счетчика 26 и вход управления дешифратора 27 являются входами синхронизации блока 10 управления, установочным входом которого является установочный вход счетчика 26.

Генератор псевдослучайных испытательных последовательностей работает следующим образом.

При включении устройства блок 12 начальной установки устанавливает счетчик 7, регистр 6 и блок Юуправ- ления в начальное (нулевое) состояние, а в блоке 1 формирования равномерно распределенных псевдослучайных чисел устанавливает логическую единицу в старшем и логический нуль в младших разрядах.

В блоках 2 и 8 памяти записана следующая информация. В каждой ячейке блока 2 памяти записано слово, состоящее из двух частей. Младшие разряды представляют собой код вероятности появления единичного сигнала а старшие - код номера выхода генератора псевдослучайных испытательных последовательностей. Каждое слово блока 2 памяти определяет номер выхода (код номера выхода записан в старших разрядах ячейки), на котором iдолжен появиться сигнал с заданной ве- .роятностью (код вероятности записан в младших разрядах ячейки). В каждой ячейке блока 8 памяти записано слово, состоящее из двух частей. Младшие разряды представляют собой код признака типа выходного сигнала, а старшие - код номера выхода генератора псевдослучайных испытательных пос ледовательностей.

Работа генератора псевдослучайных испытательных последовательностей синхронизируется блоком 10 управлени на входы которого поступают две сдвинутые синхросерии из блока 11 (фиг.4 а,б) синхрочастот.

Время появления сигнала с блока 10 управления на входе разрешения дешифратора 5 определяется максимальной задержкой появления сигнала на одном из D-входов триггеров регистра 6.

Блок 1 формирования равномерно распределенных псевдослучайных чисел в каждом такте генерирует равновероятностный псевдослучайный код, который поступает на адресные входы блок

26621

2 памяти, обеспечивая выбор соответствующей ячейки блока 2 памяти.

Содержимое этой ячейки считывается, но код номера выхода генератора 5 не поступает на входы дешифратора 5, так как в это время коммутатор ft находится в режиме, при котором первая группа выходов блока 2 памяти от.ключе- на от входов дешифратора 5. В каждом

to такте изменяется состояние счетчика 7, формирующего адреса, и из блока 8 памяти выбирается соответствующая ячейка. Старшие разряды (первая группа выходов) этой ячейки поступают на

t5 входы коммутатора 4, младшие разряды (вторая группа выходов) - на входы дешифратора 9, формирующего признак. Сигнал с дешифратора 9 поступает в блок 3 формирования выходных сигна20 лов, где формируется ср1гнал заданного типа, который поступает на информационные входы выходного регистра 6. Если- код признака с дешифратора 9 определяет, что должен быть сформирован

25 сигнал одного из следующих типов: на заданном выходе генератора сигнал логического нуля; на заданном выходе генератора сигнал логической единицы; равновероятный сигнал - О или 1

J. на заданном выходе генератора с вероятностью Р 0,5; импульсный единичный сигнал с фиксированной вероятностью; импульсный нулевой сигнал с фиксированной вероятностью, то коммутатор 4 подключает выходы блока 2 памяти к входам дешифратора 5 и код номера выхода поступает на входы дешифратора 5. При этом на тактовом входе соответствующего разряда выходного регистра 6 появляется сигнал логической единицы и этот разряд изменяет свое состояние в соответствии с сигналом, поступившим из блока 3 формирования выходных сигналов.

Если код признака с дешифратора 9 определяет, что должен быть сформирован сигнал, при котором только на одном выходе генератора происходит изменение значения сигнала, причем единичное значение сигнала устанавли- вается с заданной вероятностью, то сигнал с выхода дешифратора 9, соединенного с входом коммутатора4,отклю чает сигналы с первой группы выходов блока В памяти и подключает сигналы с 5 первой группы выходов блока 2 памяти к входам коммутатора 4.Код вероятности с блока 2 памяти при этом поступает в блок 3 формирования вьтодных сигна40

5

лов, который формирует единичный сиг- нял с этой вероятностью. Сигнал с выхода блока 3 формирования выходных сигналов поступает на информационные входы выходного регистра 6, Код номера выхода, считанный к этому времени из ячейки блока 2 памяти, депшфрирует ся дешифратором 5. На тактовом входе выбранного разряда выходного регистра 6 появляется сигнал логической единицы и вьгход этого разряда выходного регистра 6 изменяет свое состояние в соответствии с сигналом, поступившим из блока 3 формирования выходных сигналов,

Формирование сигналов псевдослучайного кода производится Ei блоке 3 формирования выходных сигналов (фиг, 2) следующим образом.

С помощью псевдослучайных кодов, формируемых на первой группе выходов блока 1 формирования равномерно распределенных псевдослучайных чисел и подаваемых на адресные входы мультиплексора 25, в любом такте выбирается с вероятностью t/2 какой-либо один из К адресов входных каналов нуль- типлексора 25. Если какой-либо из входных каналов мультиплексора 25 удерживать в единичном состоянии, то на выход мультиплексора 25 единичный сигнал проходит только в том случае,, когда на адресные его входы поступает код адреса данного канала, в любой момент может появиться случайно (псевдослучайно) с вероятностью

Р Поэтому вероятность единичного сигнала на выходах мультиплексо- Р 25 Р.; Р,,. , где п - чис2 Ti

i:1

ло объединенных входов мультиплексора, Е

6X1

- вероятность единичного

сигнала на -м входе мультиплексора. Подавая двоичный код вероятности из блока 2 памяти, а также равновероятные сигналы на входы элементов И 13 - 16 и объединяя входы мультиплексора 25 в группы, можно задать на входных каналах мультиплексора 25 различные значения вероятности.

Тем самым можно обеспечить задание на выходе мультиплексора 25 вероятности появления единичного сигнала в пределах О - 1 с определенным интервалом дискретности.

Сигнал заданной вероятности формируется на вьгходе элемента И 19, равновероятностный - на выхо,-1е элемента И 20. Импульсные сигналы с фиксированной вероятностью формируются с помощью элемента И 17 и элемента НЕ 18 на выходах элементов И 21 и 22, На входы элемента И 17 поступают ров- новероятностные сигналы с первой группы выходов блока 1 формирования

равномерно распределенных псевдослучайных чисел. Работой элементов И 19- 22 и элемента ИЛИ 23 управляют соответствующие выходы дешифратора 9. Блок 10 управления (фиг. 3) работает следующим образом,

В начале работы сигналом с выхода блока 12 начальной установки счетчик . 26 блока 20 управления устанавливается в нулевое состояние,

.

Разнесенные во времени синхрочастоты с блока 11 синхрочастот (фиг. 4 а.,ё ) обеспечивают изменение состояния счетчика 26 (фиг. 46 ) и стробирование дешифратора 27 блока 10 управления. На первом выходе дешифратора 27 формируется сигнал (фиг. 4г), поступающий на счетный вход счетчика 7 и вход синхронизации блока 1 формирования равномерно распределенных псевдослучайных чисел. Этот же сигнал, пройдя через элемент НЕ 28 (фиг. 4д ), обеспечивает управление работой блоков 2 и 8 памяти. На к-ом выходе дешифратора 27 формируется сигнал управления (фиг, 4е ) дешифратором 5,

Формула изобретения

1. Генератор псевдослучайных испытательных последовательностей, содержапщй блок формирования равномерно распределенных псевдослучайных чисел, счетчик, первый блок памяти, комм татор, первый дешифратор, выходы которого соединены с первыми входами триггеров регистра, отличаю- щ и и с я тем, что, с целью расширения функциональньж возможностей за счет получения управляемой временной диаграммы выходных сигналов, генератор содержит второй блок памяти, второй дешифратор, блок формирования выходных сигналов, блок управления, блок синхрочастот, блок начальной установки, выход которого соединен с установочными входами регистра, счетчика, блока управления

и блока формирования р авномерно распределенных псевдослучайных чисел, первая группа выходов которого соединена с первой группой входов блока формирования выходных сигналов, вторая группа входов которого соединена с выходами второго дешифратора, первый выход которого соединен также с входом коммутатора, первая группа входов которого соединена с первой группой выходов первого блока памяти адресные входы которого соединены с второй группой выходов блока формирования равномерно распределенных псевдослучайных чисел, вход которого соединен с- входом счетчика и первым выходом блока управления, второй выход которого соединен с входом перво го дешифратора, первая группа входов которого соединена с выходами коммутатора, вторая группа входов которого соединена с первой группой выходов второго блока памяти, адресные входы которого соединены с выходами счетчика, вход управления второго блока памяти соединен с третьим выходом блока управления и входом управления первого блока памяти, втора группа выходов которого соединена с третьей группой входов блока формирования выходных сигналов, выход которого соединен с вторыми входами триггеров регистра, блока синхрочастот соединены с соответствующими входами синхронизации блока управления, вторая j pynna выходов второго блока памяти соединена с входами второго дешифратора.

2. Генератор по п. 1,отли- чающийся тем, что блок формирования выходных сигналов содержит первый, второй, третий, четвертый и пятый элементы И, элемент НЕ, шестой седьмой, восьмой и девятый элементы И, элемент ИЛИ, мультиплексор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, в.ыход которого

ю J5 2о 25 о

5

5

соединен с первым входом ш%,стого элемента И, выход которого соединенс с первым входом элемента ИЛИ, второй, третий и четвертый входы которого соединены соответственно с выходами седьмого, восьмого и девятого элемен- .тов И, первый вход которого соединен с выходом пятого элемента И и входом элемента НЕ, выход которого соединен с первым входом восьмого элемента И, выходы первого, второго, третьего и четвертого элементов И соединены с соответствующими информационными входами мультиплексора, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого, а также первые входы первого, второго и третьего элементов И являются третьей группой входов блока формирования выходных сигналов, первой группой входов которого являются вторые входы первого, второго, третьего элементов И, первый вход седьмого элемента И, входы четвертогй, пятого элементов И и адресные входы мультиплексора, второй группой входов блока формирования вьпсодных сигналов являются вторые входы шестого, седьмого, восьмого, девятого элементов И и пятый вход элемента ИЛИ, выход которого является выходом блока формирования выходных сигналов.

3. Генератор по п. п.1,о т л и - чающийся тем, что блок управления содержит последовательно соединенные счетчик и дешифратор, элемент НЕ, вход которого соединен с- выходом дешифратора, выходы которого являются первым и вторым выходами блока управления, третьим выходом которого является выход элемента НЕ, счетный вход счетчика и вход управления дешифратора являются входами синхронизации блока управления, установочным входом которого является установочный вход счетчика.

If.

1-я tf.

n

Г&W

Z1

5h

Выход

22.1

PP

1 Я If:

Фтг

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Генератор псевдослучайных чисел | 1989 |

|

SU1691839A2 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Генератор случайного процесса | 1988 |

|

SU1656527A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

Изобретение относится к импульсной технике. Цель изобретения - расширение функциональных возможностей достигается путем получения управляемой временной диаграммы выходных сигналов. Для достижения поставленной цели в устройство введены второй блок памяти В, второй дешифратор 9, блок 3 формирования выходных сигналов, а также блоки управления 10, синхрочастот 1.1 и начальной установки 12.Генератор псевдослучайных испытательных последовательностей также содержит блок 1 формирования равномерно распределенных псевдослучайных чисел, блок 2 памяти, коммутатор 4, дешифратор 5, регистр 6 и счетчик 7. Функциональные схемы блока 3 формирования выходных сигналов, блока 10 управления, а также временные диаграммы работы генератора псевдослучайных испытательных последовательностей приводятся в описании изобретения. 2 з.п.ф-лы, 4 ил. (Л

Фи.Ъ

n

Редактор H. Рогулич

«A/e

Составитель Ю. Бурмистров Техред В.КадарКорректор Г. Решетник

Заказ 2146/57Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35„ Раушская наб., д. Д/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Генератор псевдослучайных кодов | 1978 |

|

SU767743A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-11-23—Подача