Изобретение относится к вычислительной технике, в частности к средствам автоматического контроля микропроцессорных устройств, и может быть использовано в радиоэлектронной промышленности в процессе разработки, производства и эксплуатации микропроцессорных систем.

Цель изобретения - повышение полноты формируемой тест-программы и сокращение времени формирования.

На фиг. 1 представлена структурная схема предлагаемого формирователя; на фиг. 2 - схема мультиплексора выдачи теста; на фиг. 3 - схема генератора, построенного на многосвязной цепи Маркова; на фиг. 4 - схема блока памяти последовательности кодов микротестов; на фиг. 5 - блок-схема алгоритма работы блока управления; на фиг. 6 - схема блока управления.

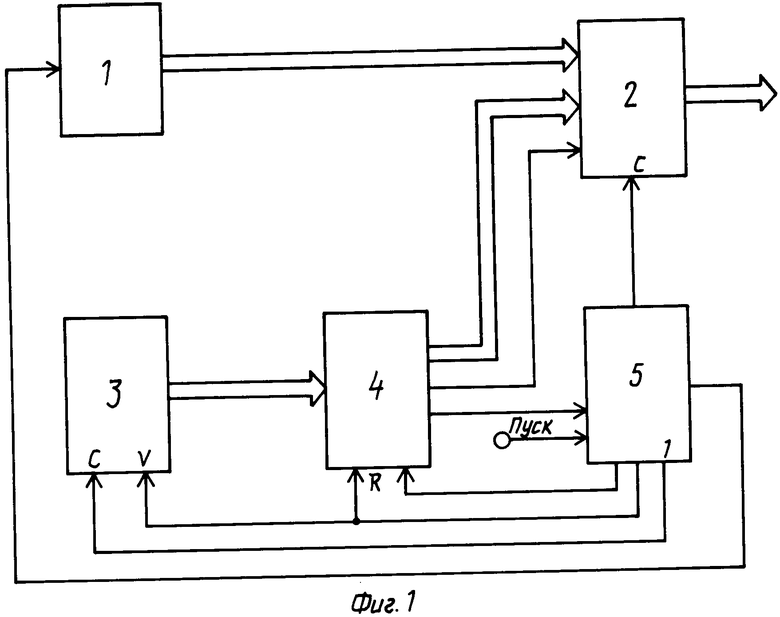

Формирователь тестов содержит генератор 1 псевдослучайных кодов, мультиплексор 2 выдачи теста, генератор 3 случайной последовательности, блок 4 памяти последовательности кодов микротестов, блок 5 управления.

Мультиплексор 2 предназначен для формирования очередного слова команды и состоит из мультиплексора 6 и буферного регистра 7.

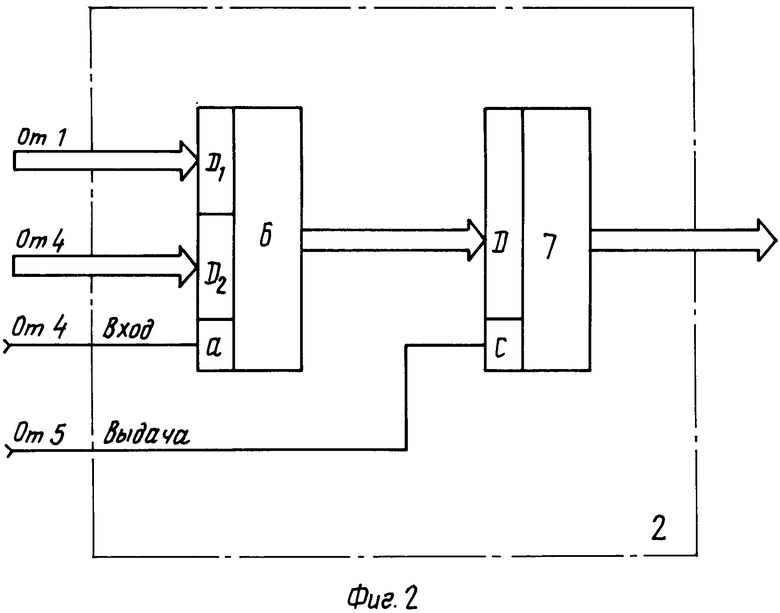

Генератор 3 построен как блок многосвязной цепи Маркова содержит группу 8 регистров, образованную регистрами 9.1,9.2, . . . , 9. n, где n - связность цепи Маркова, генератор 10 псевдослучайной последовательности, блок 11 памяти, регистр 12.

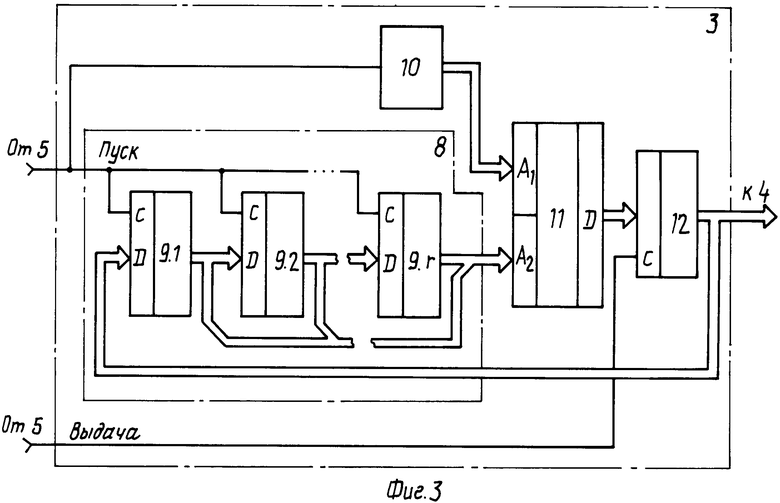

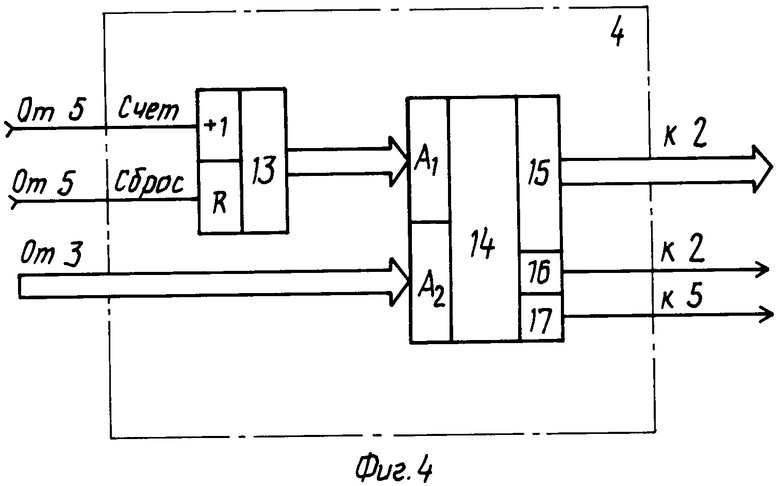

Блок 4 содержит счетчик 13 и блок 14 памяти с выходами 15-17.

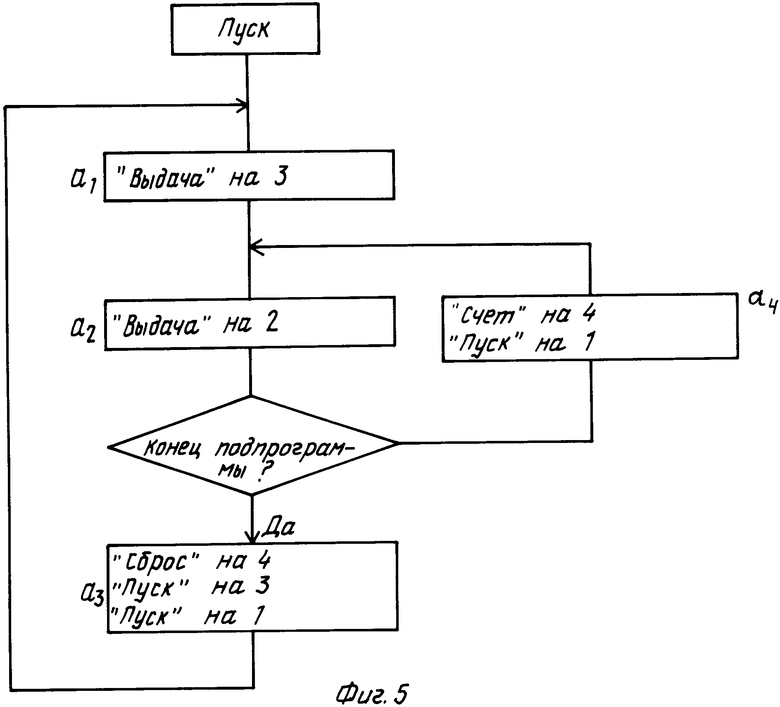

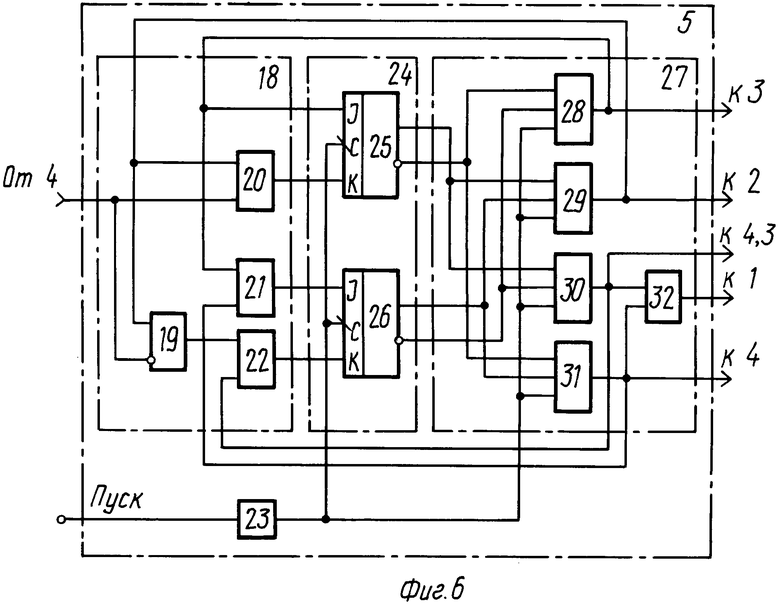

Блок 5 управления представляет собой синхронный управляющий автомат с множеством внутренних состояний а0, а1, а2, а3 и содержит дешифратор 18, образованный элементами И 19 и 20 и элементами ИЛИ 21 и 22, генератор 23 тактовых импульсов, группу 24 триггеров, образованную триггерами 25 и 26, дешифратор 27, образованный элементами И 28-31 и элементом ИЛИ 32.

Для пояснения работы формирования тестов воспользуемся следующей структурой команд микропроцессора. С целью эффективного использования оборудования команды микропроцессора имеют переменную длину и могут состоять из 1, 2, 3 и т. д. слов. Например, микропроцессоры типа INTEL 8080, КР 580 имеют одно-, двух- и трехсловные команды, где длина одного слова составляет 8 бит (один байт). Независимо от типа команды, код выполняемой операции, длина самой команды и режимы адресации операндов задаются в ее первом слове. Следующие слова команды содержат данные, участвующие в операциях, либо их адреса. Назовем первое слово команды кодом команды.

Генератор 1 псевдослучайных кодов предназначен для генерации случайных чисел, используемых в качестве второго, третьего и т. д. слова команды, т. е. в качестве адресов и данных. В простейшем случае он может быть реализован на сдвиговых регистрах с обратными связями. При подаче на вход генератора 1 сигнала "Пуск" на его выходе появляется псевдослучайный код. Следующий код вырабатывается при подаче следующего сигнала "Пуск" и т. д. Разрядность вырабатываемых кодов равна разрядности слов, на которых состоит команда.

Мультиплексор 6 в зависимости от значения сигнала на его управляющем входе, передает на выход либо данные с входа D1 или D2.

Буферный регистр 7 служит для хранения очередного слова команды. Запись очередного слова команды в буферный регистр 7 осуществляется при подаче на управляющий вход мультиплексора 2.

Таким образом, если управляющий сигнал "Вход" мультиплексора 2 равен единице, то при поступлении сигнала "Выдача" в регистр 7 записывается код с выхода генератора 1, т. е. на выход формирователя подается псевдослучайное данное. Если управляющий сигнал "Вход" мультиплексора 2 выдачи теста равен нулю, то при поступлении сигнала "Выдача" в регистр 7 записывается код с выхода блока 4.

Генератор 3 предназначен для формирования случайной последовательности кодов, управляющие стохастическими характеристиками порождаемых микротестов.

Генератор 10 псевдослучайной последовательности вырабатывает распределенные числа. В простейшем случае может быть реализован на сдвиговых регистрах с обратными связями. При подаче на управляющий вход генератора 10 сигнала "Пуск" на его выходе появляется псевдослучайное число. Очередное псевдослучайное число вырабатывается при подаче следующего управляющего сигнала "Пуск" и т. д.

Регистры 9 предназначены для хранения кодов состояния связной цепи Маркова.

Блок 11 памяти представляет собой двухмерный массив из слов. Адресация слова осуществляется путем указания номера строки и номера столбца. При изменении адреса на адресных входах запускается процесс чтения, и на выходе блока 11 памяти появляется содержимое соответствующего слова. При этом в регистре 9.1 хранится младшая (правая) группа из ] log2β [ разрядов адреса; в регистре 9.2 - следующая (справа-налево) группа из ] log2 β [ разрядов адреса и т. д. ; в регистре 9. n - старшая (левая), т. е. n-я группа из ] log2 β [ разрядов адреса, где β - число состояний цепей Маркова.

Разрядность адресного входа А1 совпадает с разрядностью генератора 10 псевдослучайной последовательности генератора 3.

Блок 4 формирования последовательности кодов микротестов предназначен для формирования кодов команд и операндов.

Таким образом, число строк блока 14 памяти равно β n, а число столбцов - 2m, где m - разрядность генератора 3.

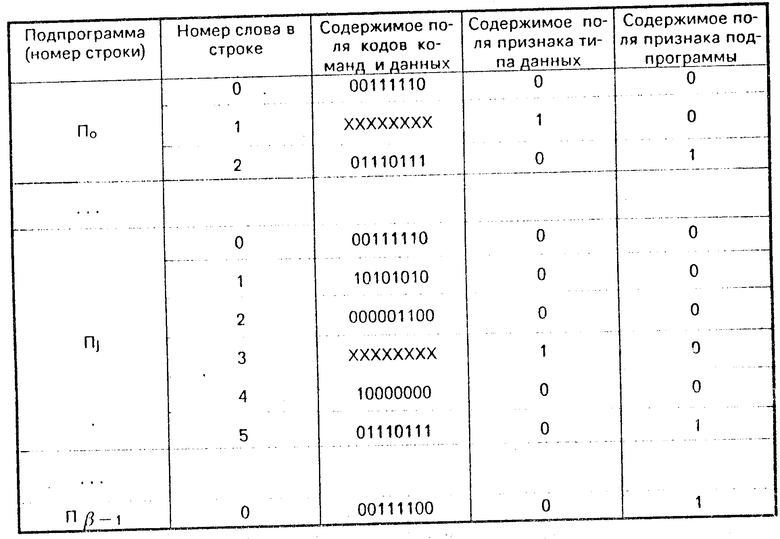

Каждое слово блока 14 памяти состоит из следующих полей:

поле команд и данных, содержащего С разрядов, в поле команд и данных записывается код команды или операнды, указанному полю соответствует группа выходов 15 блока 14 памяти;

однобитовое поле признака типа данных, в котором заносится "0", если соответствующие данные являются детерминированными (содержатся в поле команд и данных) и "1", если в качестве данных используются случайные коды с выхода генератора 1, полю признака данных соответствует выход 16 блока 14 памяти;

однобитовое поле признака конца подпрограммы, в котором заносится "1", если рассматриваемое слово является последним словом подпрограммы или "0" - в противном случае, полю признака конца подпрограммы соответствует выход 17 блока 14 памяти.

Блок 5 управления обеспечивает управление процессом формирования тестов в соответствии с алгоритмом, представленным на фиг. 5. Дешифратор 18 реализует функцию возбуждения памяти управляющего автомата. Группа 24 триггеров образует память управляющего автомата.

Дешифратор 27 предназначен для определения текущего состояния управляющего автомата и формирования выходных сигналов блока управления.

Состояния управляющего автомата кодируются следующим образом: а0 - 00, а1 - 11, а2 - 10, а3 - 01, где двоичными числами обозначены состояния триггеров 26 и 25 соответственно.

Формирователь работает следующим образом.

Порождаемая тестовая последовательность состоит из подпрограмм, причем порядок порождения подпрограмм определяется цепью Маркова.

В исходном состоянии триггеры 25 и 26 и счетчик 13 установлены в нулевое состояние.

На выходах генераторов 1 и 10 установлены произвольные псевдослучайные коды. В регистрах 9.1, . . . , 9. n и блок 11 памяти заносится следующая информация (на фиг. 1-6 цепи сброса и начальной загрузки условно не показаны).

Из множества команд контролируемого микропроцессора составляются тестовые подпрограммы. Каждая подпрограмма представляет собой последовательность команд. Так как в исходном состоянии на адресном входе блока 11 памяти установлен произвольный псевдослучайный код, а на другом адресном входе - код некоторого состояния, принятой до начальной, то на выходе блока 11 памяти в исходном состоянии установлен номер некоторой подпрограммы.

В блок 14 памяти заносятся подпрограммы, из которых формируется случайная последовательность тестов (см. таблицу).

Если каждая подпрограмма состоит ровно из одной команды, а признаки типа данных установлены в единицу, то предлагаемый формирователь формирует такие же тестовые последовательности, что и прототип.

При использовании постоянных либо перепрограммируемых запоминающих устройств соответствующая информация заносится в блок 14 памяти на этапе изготовления предлагаемого формирователя.

По сигналу "Пуск" генератор 23 тактовых импульсов начинает формирование тактовых импульсов.

Поскольку триггеры 25 и 26 находятся в нулевом состоянии, первый тактовый импульс через элемент И 28 дешифратора 27 поступает на вход "Выдача" генератора 3. На выходе регистра 12 появляется очередное состояние многосвязной цепи Маркова (номер подпрограммы), которое поступает на адресный вход блока 14 памяти и на информационный вход регистра 9.1. Изменение адреса на входе запускает процесс чтения из блока 14 памяти. При этом в качестве адреса строки используется содержимое регистра 12 (номер подпрограммы), а в качестве адреса столбца - содержимое счетчика 13 (номер слова внутри подпрограммы). На выходах блока 14 памяти появляются следующие данные: на группе выходов 15 появляется содержимое поля данных текущего слова подпрограммы (т. е. код команды или операнд), который поступает на группу информационных входов мультиплексора 6; на выходе 16 появляется признак типа данных (т. е. "0", если в качестве очередного слова тестовой последовательности используется значение с группы выходов 15 или "1", если необходимо сгенерировать псевдослучайный операнд), который поступает на управляющий вход мультиплексора 6; на выходе 17 появляется признак конца подпрограммы (т. е. "1", если рассматриваемое слово является последним в подпрограмме или "0" - в противном случае), который поступает на вход дешифратора 18 блока 5 управления.

В зависимости от значения поля 16 признака данных на выход мультиплексора 6 коммутируется либо один вход, либо другой. Данные с выхода мультиплексора 6 поступает на информационные входы регистра 7 узла выдачи теста.

Поскольку в этом состоянии выходы элемента И 28 и элемента ИЛИ 21 установлены в единицу, по заданному фронту первого тактового импульса триггеры 25 и 26 устанавливаются в единицу.

Второй тактовый импульс через элемент И 29 поступает на вход "Выдача" мультиплексора 2 выдачи теста, фиксируя в регистре 7 очередное слово формируемого теста, поступающего с выхода мультиплексора 6. Рассматриваемое слово поступает на выход формирователя.

В состоянии а2 управляющего автомата в зависимости от значения сигнала на входе дешифратора 18 происходит следующее: если сгенерированное слово тестовой последовательности не является последним в подпрограмме, т. е. выход 17 блока 14 памяти (после признака конца подпрограммы) находится в нулевом состоянии, то выходы элементов И 19 и ИЛИ 22 устанавливаются в единицу и по заднему фронту второго импульса триггера 26 сбрасывается в ноль (состояние а4 управляющего автомата); в противном случае выход 17 блока 14 памяти находится в единичном состоянии, выход элемента И 20 устанавливается в единицу и по заднему фронту второго тактового импульса триггер 25 сбрасывается в ноль (состояние а3 управляющего автомата).

В случае, если еще не достигнут конец подпрограммы, следующий тактовый импульс поступает через элемент И 31 на вход "+1" счетчика 13 и через элемент ИЛИ 32 на вход "Пуск" генератора 1. При этом содержимое счетчика 13 увеличивается на единицу. Новое содержимое счетчика 13 поступает на первый адресный вход (вход А1) блока 14 памяти. Генератор 1 вырабатывает псевдослучайное число, которое поступает на первую группу информационных входов мультиплексора 6. Изменение адреса на входе А1 запускает процесс чтения из блока 14 памяти. На входах блока 14 памяти появляется очередное слово подпрограммы, а на выходах мультиплексора 6 формируется очередное слово тестовой последовательности, которое поступает на информационные входы регистра 7. Поскольку в состоянии а4 выходы элемента И 31 и элемента ИЛИ 21 установлены в единицу, то по заднему фронту рассматриваемого тактового импульса триггер 26 переходит в единичное состояние (состояние а2 управляющего автомата).

Если же достигнут конец подпрограммы, то следующий тактовый импульс через элемент И 30 поступает на вход "Сброс" счетчика 13, на вход "Пуск" блока 3 многосвязной цепи Маркова и через элемент ИЛИ 32 на вход "Пуск" генератора 1. При этом счетчик 13 сбрасывается в нулевое состояние, образуя новый адрес столбца, который поступает на первый адресный вход блока 14 памяти, в регистр 9.1 записывается код, поступающий с выхода регистра 12, а в регистры 9.2, . . . , 9. n записываются коды, поступающие с выходов регистров 9.1, . . . , 9. n-1, соответственно; содержимое регистров 9.1, . . . , 9. n образует новый адрес строки, который поступает на вторую группу адресных входов блока 11 памяти; генератор 10 псевдослучайных кодов вырабатывает псевдослучайное число, которое поступает на первую группу адресных входов (вход А1) блока 11 памяти.

Изменение адреса запускает процесс чтения из блока 14 памяти. На выходе блока 14 памяти появляется номер очередного состояния цепи Маркова (номер следующей подпрограммы), который поступает на информационные входы регистра 12. Поскольку в состоянии выходы элемента И 30 и элемента ИЛИ 22 установлены в единицу, то по заднему фронту рассматриваемого тактового импульса триггер 26 устанавливается в нулевое состояние (состояние а1 управляющего автомата).

Таким образом, смена состоянии а4 и а2 управляющего автомата обеспечивает выдачу на выход формирователя команд соответствующих тестовых подпрограмм. Смена состояний а3 и а1 обеспечивает случайный выбор другой тестовой подпрограммы.

Формирователь позволяет сочетать детерминированные и псевдослучайные тестовые воздействия. При этом неисправности, легко обнаруживаемые случайными воздействиями, выявляются с помощью команд, состоящих из кодов, вырабатываемых блоком 4, и данных с выхода генератора 1. Труднообнаруживаемые неисправности выявляются с помощью детерминированных воздействий, хранимых в блоке 14 памяти.

В частности, для микропроцессора INTEL 8080 (К 580 ИК 80) 80% неисправностей являются легко обнаруживаемыми и требуют порядка 106 псевдослучайных тестовых команд. Для труднообнаруживаемых неисправностей (20% ) в прототипе требуется увеличение длины тест-программы в 10 раз. (56) Авторское свидетельство СССР N 1552185, кл. G 06 F 11/26, 1990.

Авторское свидетельство СССР N 1661769, кл. G 06 F 11/26, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2010316C1 |

| Формирователь тестов | 1989 |

|

SU1661769A1 |

| Формирователь тестов | 1987 |

|

SU1552185A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Формирователь тестов | 1988 |

|

SU1635187A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

Изобретение относится к вычислительной технике, в частности к средствам автоматического контроля микропроцессорных устройств. Цель изобретения - повышение полноты и сокращение времени контроля. Формирователь тестов содержит генератор псевдослучайных кодов, мультиплексор выдачи теста, генератор случайной последовательности, блок памяти последовательности кодов микротестов, блок управления. Генерируемая на выходе формирователя последовательность кодов команд и данных представляет собой псевдослучайную последовательность регулярных подпрограмм, вероятность появления которых описывается многосвязной цепью Маркова. Коды команд вырабатываются мультиплексором выдачи теста. Операнды команды вырабатываются либо генератором псевдослучайных кодов, либо мультиплексором выдачи теста. Сочетание случайных и регулярных тестовых воздействий ведет к повышению полноты формируемых тестов и сокращению времени контроля. 6 ил. , 1 табл.

ФОРМИРОВАТЕЛЬ ТЕСТОВ, содержащий блок управления, мультиплексор выдачи тестов, генератор случайной последовательности, генератор псевдослучайных кодов, блок памяти последовательности кодов микротестов, причем группа выходов мультиплексора выдачи тестов является группой выходов формирователя, первый выход поля управления блока управления соединен с входом синхронизации генератора случайной последовательности, группа выходов которого соединена с группой адресных входов блока памяти последовательности кодов микротестов, группа выходов которого соединена с первой группой информационных входов мультиплексора выдачи теста, второй выход поля управления блока управления соединен с входом разрешения генератора случайной последовательности, третий выход поля управления блока управления соединен с входом синхронизации генератора псевдослучайных кодов, группа выходов которого соединена со второй группой информационных входов мультиплексора выдачи теста, вход пуска формирователя соединен с входом пуска блока управления, отличающийся тем, что четвертый выход поля управления блока управления соединен с входом синхронизации мультиплексора выдачи теста, пятый выход поля управления блока управления соединен с входом синхронизации блока памяти последовательности кодов микротестов, первый выход которого соединен с управляющим входом мультиплексора выдачи теста, вход логического условия блока управления соединен с вторым выходом блока памяти последовательности кодов микротестов, вход установки начального состояния блока памяти последовательности кодов микротестов соединен с вторым выходом поля управления блока управления.

Авторы

Даты

1994-05-15—Публикация

1991-09-26—Подача