Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах, связанных с преобразователем информации ,

Цель изобретения - повьшгение быстродействия и контролируемости преобразователя.

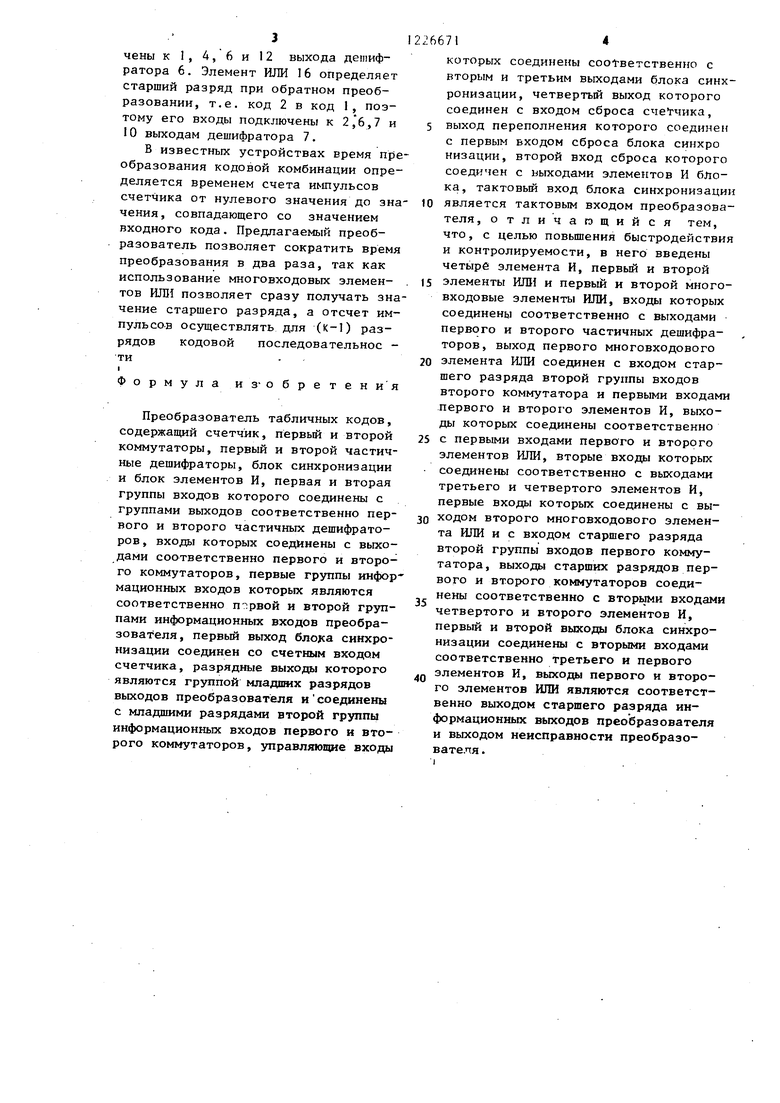

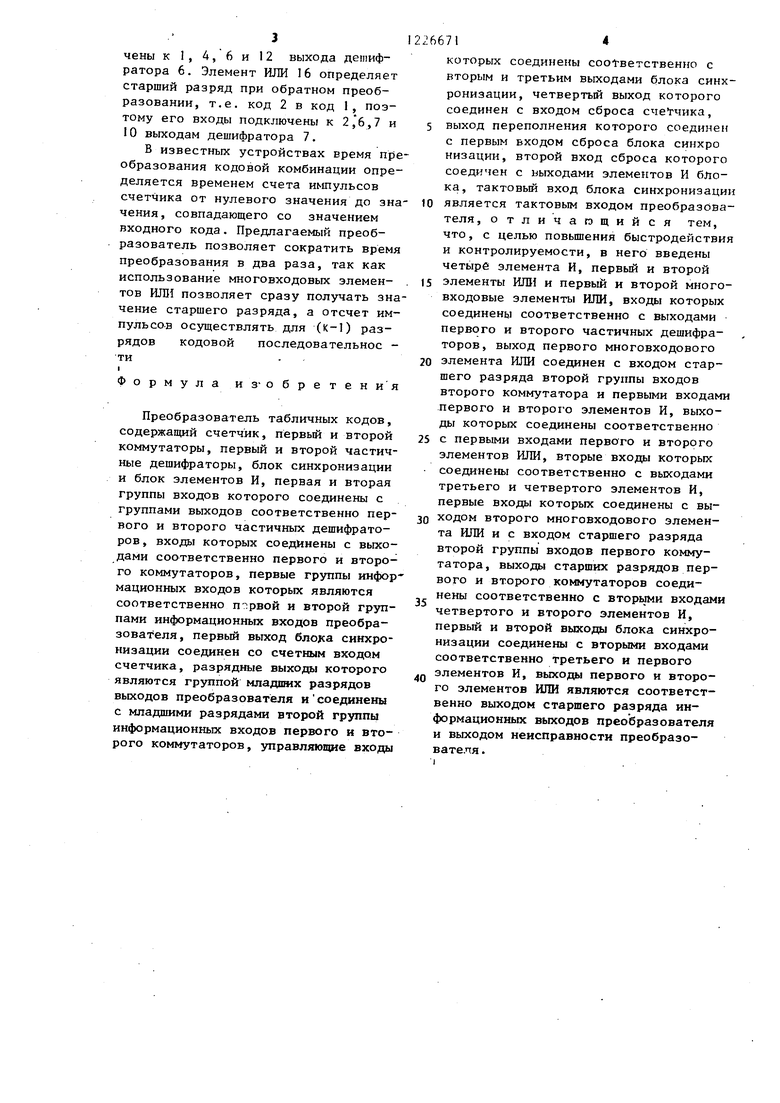

На чертеже приведена структурная схема преобразователя.

Преобразователь содержит блок 1 синхронизации, тактовый вход 2 преобразователя , счетчик 3, первый и второй коммутаторы 4 и -5, первый и второй частичные дешифраторы 6 и 7, группу 8 элементов И, элементы И 9 и 10, элемент ИЛИ 11, элементы И 12 и 13, элемент ИЛИ 14, первый и второй многовходовые элементы ИЛИ 15 и 16, первую 17 и вторую 18 группы информационных входов преобразователя, группу 19 информационных выходов преобразователя, выход 20 неисправности преобразователя.

Предлагаемый преобразователь работает следующим образом.

При поступлении преобразуемого кода на первую группу входов коммутатора 4 блок 1 синхронизации устанавливает счетчик 3 в исходное состояние, выдает на коммутатор 4 управляющий сигнал, разрешающий поступление входной информации с первой группы информационных входов через коммутатор 4 на частичный дешифратор 6. С возбужденных выходов дешифратора информация поступает на входы элементов И группы 8. Одновременно информация с выходов частичного дешифратора 6, определяющих старший разряд выходного кода, поступает на входы многовходового элемента ИЛИ 15 тем самым сразу определяя старший разряд выходного кода, который поступает на информационные входы коммутатора 5. Далее блок 1 синхронизации выдает на коммутатор управляющий сигнал, разрешающий поступление кодовых комбинаций через входы коммутатора 5. Счетчик 3 начинает перебор кодовых комбинаций, возбуждая выходы дешифратора 7. При совпадении кода,поступившего с первой группы информационных входов, с кодовой комбинацией, накопленной в счетчике 3 в совокупности со старшим разрядом, согласно закону перекодирования на выходе блока элементов И группы 8 появляется сигнал, который, воз

действуя на блок синхронизации, прекращает поступление импульсов на счетный вход счетчика 3 и фиксирует его состояние. Старший разряд преобразованного кода снимается с выхода многовходовог о элемента ИЛИ 15 через элементы И 10 и ИЛИ 11, остальные (К-1) разряды преобразованного кода снимаются с выходов счетчика 3. При обратном преобразовании преобразуемый код поступает через коммутатор 5 на дешифратор 7, а кодовые комбинации со счетчика 3 - на вход дешифратора 6 через коммута- J тор 4. В дальнейшем преобразователь работает аналогично.

В случае, если на вход преобразователя подана комбинация, не охваченная законом преобразования, то сигнал переполнения счетчика 3 воздействует на блок синхронизации, прекращая поступление импульсов на счетный вход счетчика 3 и останавливая устройство.

Использование многовходовых элементов ИЛИ позволяет одновременно с преобразованием кодовых комбинаций осуществлять контроль правильности преобразования старшего разряда и выдавать сообщение об ошибке, используя элементы И 13 и ИЛИ 14.

Пусть необходимо осуществить взаимные преобразования кодов, приведенных в таблице.

0

5

0

Элемент ИЛИ 15 определяет старший разряд при преобразовании кода 1 в код 2, поэтому его входы подклю3

чены к 1, 4,6 и 12 выхода дешифратора 6. Элемент ИЖ 16 определяет старший разряд при обратном преобразовании, т.е. код 2 в код 1, поэтому его входы подключены к 2 , б, 7 и 10 выходам дешифратора 7.

В известных устройствах время преобразования кодовой комбинации определяется временем счета иьтульсов счетчика от нулевого значения до значения , совпадающего со значением входного кода. Предлагаемый преобразователь позволяет сократить время преобразования в два раза, так как использование многовходовых элемен- тов ИЛИ позволяет сразу получать значение старшего разряда, а отсчет им- пульсо-в осуществлять для (К-1) разрядов кодовой последовательное ти

I

Формула из-обретени я

Преобразователь табличных кодов, содержащий счетчик, первый и второй коммутаторы, первый и второй частичные дешифраторы, блок синхронизации и блок элементов И, первая и вторая группы входов которого соединены с группами выходов соответственно первого и второго частичных дешифраторов , входы которых соединены с выходами соответственно первого и второго коммутаторов, первые группы инфор мационных входов которых являются соответственно первой и второй группами информационных входов преобразователя, первьш выход блока синхронизации соединен со счетным входом счетчика, разрядные выходы которого являются группой младших разрядов выходов преобразователя и соединены с младшими разрядами второй группы информационных входов первого и второго коммутаторов, управляющие входы

26671«

которых соединены cootBercTBeHHO с вторым и третьим выходами блока синхронизации, четвертый выход которого соединен с входом сброса сче гчика,

5 выход переполнения которого соединен с первым входом сброса блока синхро низации, второй вход сброса которого соедичен с выходами элементов И блока, тактовый вход блока синхронизации

10 является тактовым входом преобразователя, отличающийся тем, что, с целью повьш1ения быстродействия и контролируемости, в него введены четыре элемента И, первый и второй

15 элементы ИЛИ и первьш и второй много- входовые элементы ИЛИ, входы которых соединены соответственно с выходами первого и второго частичных дешифраторов, выход первого миоговходового

20 элемента ИЛИ соединен с входом старшего разряда второй группы входов второго коммутатора и первыми входами первого и второго элементов И, выходы которых соединены соответственно

25 с первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены соответственно с выходами третьего и четвертого элементов И, первые входы которых соединены с вы30 ходом второго многовходового элемента ИЛИ и с входом старшего разряда второй группы входов первого коммутатора, выходы старших разрядов первого и второго коммутаторов соединены соответственно с вторыми входами четвертого и второго элементов И, первый и второй выходы блока синхронизации соединены с вторыми входами соответственно третьего и первого

. элементов И, выхода первого и второго элементов ИЛИ являются соответственно выходом старшего разряда информационных выходов преобразователя и выходом неисправности преобразователя .

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь табличных кодов | 1979 |

|

SU769529A1 |

| Преобразователь последовательного комбинированного кода в параллельный двоичный код | 1982 |

|

SU1078424A1 |

| Стартстопный демодулятор | 1986 |

|

SU1363516A1 |

| Устройство для анализа распределения ошибок в кодовой комбинации | 1983 |

|

SU1128401A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1522400A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 2005 |

|

RU2298624C2 |

| Устройство сопряжения | 1981 |

|

SU993240A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах, связанных с преобразованием информации. Целью изобретения является повышение быстродействия и контролируемости преобразования. Это дости- гается тем, что в преобразователь введены комбинационные элементы определяющие и преобразующие старшие разряды входного и выходного кодов, а также определяющие запрещенные кодовые комбинации. 1 ил.

| Устройство для преобразования кодов | 1974 |

|

SU530329A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь табличных кодов | 1979 |

|

SU769529A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-06-14—Подача