t

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах, связанных с преобразованием информации.

Известен преобразователь кодов .1Д содержащий распределитель импульсов, первый и второй шифраторы, первую и вторую схемы сравнения. Недостаток данного устройства состоит в том, что для преобразования кодов, отображающих алфавитно-цифровую информацию, необходим распределитель на большое число выходов. Это усложняет устройство, снижает его надежность и технологичность.

Наиболее близким решением данной задачи является преобразователь табличных кодов 2, содержащий двоичный счетчик, генератор импульсов, выход которого соединен со счетным входом двоичного счетчика, блок управления, первый и второй коммутаторы, первые группы информационных входов которых соединены с первой и второй группами входов преобразователя.

Кроме того, преобразователь содержит второй счетчик, два полных дешифратора и два блока выдачи информации.

Недостаток преобразователя состоит в большом объеме аппаратуры и низкой технологичности, связанных с наличием двух полных дешифраторов на большое число выходов.

Целью изобретения является упрощение преобразователя, повышение его надежности и технологичности.

Поставленная цель достигается за счет того, что преобразователь табличных кодов, содержащий двоичный счетчик, генератор импульсов, выход которого соединен со счетным входом двоичного счетчика, блок управления, первый ивторой коммутаторы, первые группы информационных входов которых соединены с первой группой входов преобразователя, содержит первый и второй частичные дешифраторы и блок элементов И,выход которого соединен с входом блокировки блока управления. Первый и второй выходы блока управления соединены с управляющими входами первого и второго коммутаторов, вторые группы входов которых соединены с группой выходов двоичного счетчика и являются выходами преобразователя. Группы выходов первого и второго коммутаторов соединены со входами первого и второго частичных дешифраторов соответственно, группы выходов которых соединены с первой и второй группами входов блока элемента И. Третий вход блока управления соединен с входом блокировки генератора импульсов, четвертый выход - со входом сброса двоичного счетчика, выход переполнения которого соединен с третьим входом блока управления.

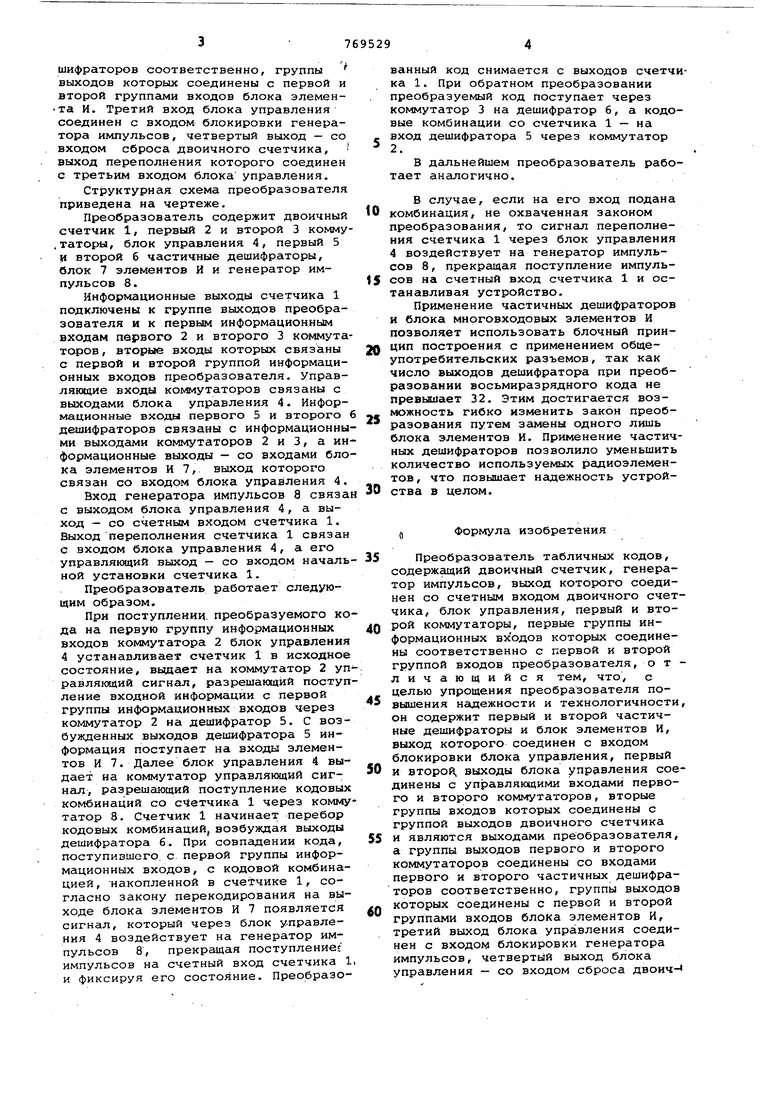

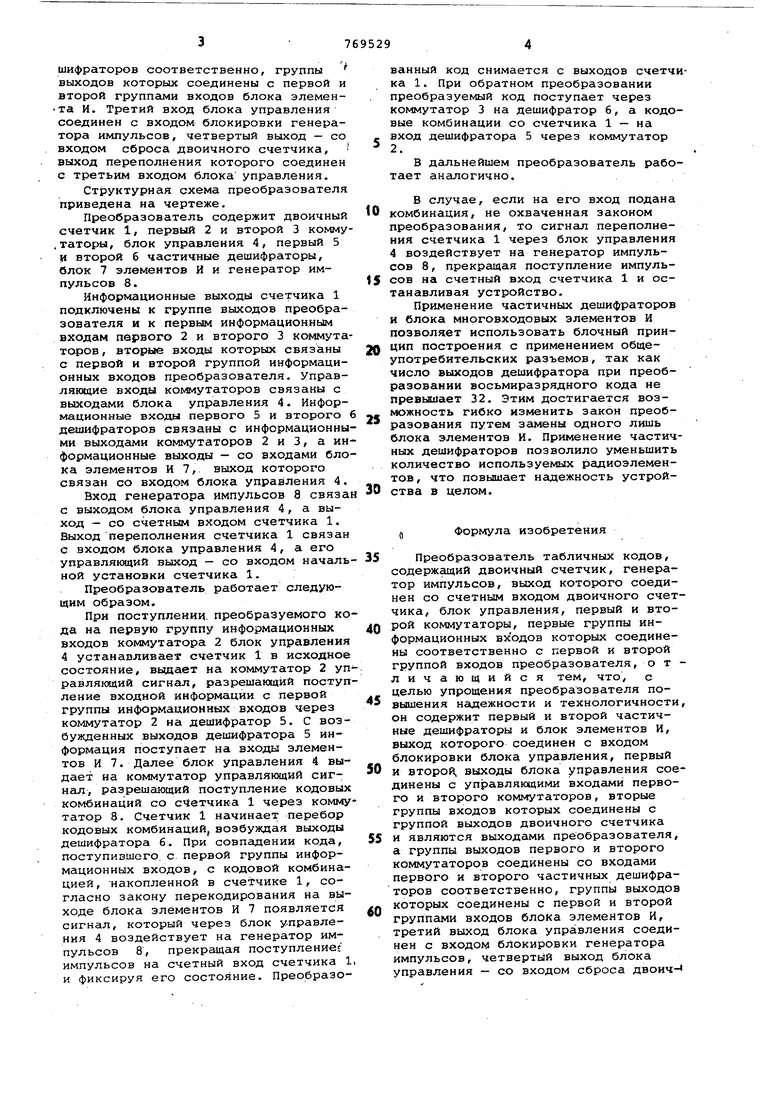

Ст руктурная схема преобразователя приведена на чертеже.

Преобразователь содержит двоичный счетчик 1, первый 2 и второй 3 комму.таторы, блок управления 4, первый 5 Н второй 6 частичные дешифраторы, блок 7 элементов И и генератор импульсов 8.

Информационные выходы счетчика 1 подключены к группе выходов преобразователя и к первым информационн1Л4 входам первого 2 и второго 3 коммутаторов, вторьте входы которых связаны с первой и второй группой информационных входов преобразователя. Управляющие входы коммутаторов связаны с выходами блока управления 4. Информационные входы первого 5 и второго 6 дешифраторов связаны с информационными выходами коммутаторов 2 и 3, а информационные выходы - со входами блока элементов И 7, выход которого связан со входом блока упрайления 4.

Вход генератора импульсов 8 связан с выходом блока управления 4, а выход - со счетным входом счетчика 1, Выход переполнения счетчика 1 связан с входом блока управления 4, а его управлякядий выход - со входом начальной установки счетчика 1.

Преобразователь работает следующим образом.

При поступлении- преобразуемого кода на первую группу информационных входов коммутатора 2 блок управления 4 устанавливает счетчик 1 в исходное состояние, выдает на коммутатор 2 управлякяций сигнал, разрешающий поступление входной информации с первой группы информационных входов через коммутатор 2 на дешифратор 5. С возбужденных выходов дешифратора 5 информация поступает на входы элементов И 7. Далее блок управления 4 выдает на коммутатор управляющий сигнал разрешающий поступление кодовых комбинаций со сЧетчика 1 через коммутатор 8. Счетчик 1 начинает перебор кодовых комбинаций, возбуждая выходы дешифратора 6. При совпадении кода, поступившего, с первой группы информационных входов, с кодовой комбинацией, накопленной в счетчике 1, согласно закону перекодирования на выходе блока элементов И 7 появляется сигнал, который через блок управления 4 воздействует на генератор импульсов 8, прекращая поступление; импульсов на счетный вход счетчика 1, и фиксируя его состояние. Преобразованный код снимается с выходов счетчика 1. При обратном преобразовании преобразуемый код поступает через коммутатор 3 на дешифратор 6, а кодовые комбинации со счетчика 1 - на

вход дешифратора 5 через коммутатор

2.

В дальнейшем преобразователь работает аналогично.

В случае, если на его вход подана

О комбинация, не охваченная законом преобразования, то сигнгш переполнения счетчика 1 через блок управления 4 воздействует на генератор импульсов 8, прекращая поступление импульS сов на счетный вход счетчика 1 и останавливая устройство.

Применение частичных дешифраторов и блока многовходовых элементов И позволяет использовать блочный принQ цип построения с применением общеупотребительских разъемов, так как число выходов дешифратора при преобразовании восьмиразрядного кода не превьшает 32. Этим достигается возможность гибко изменить закон преобразования путем замены одного лишь блока элементов И. Применение частичных дешифраторов позволило уменьшить количество используемых ргщиоэлементов, что повышает надежность устройства в целом.

d Формула изобретения

Преобразователь табличных кодов, содержащий двоичный счетчик, генератор импульсов, выход которого соединен со счетным входом двоичного счетчика, блок управления, первый и второй коммутаторы, первые группы информационных входов которых соединены соответственно с первой и второй группой входов преобразователя, отличающийся тем, что, с целью упрощения преобразователя повышения надежности и технологичности.

он содержит первый и второй частичные дешифраторы и блок элементов И, выход которого соединен с входом блокировки блока управления, первый

0 и второй, выходы блока управления соединены с управляющими входами первого и втор;ого коммутаторов, вторые группы входов которых соединены с группой выходов двоичного счетчика

5 и являются выходами преобразователя, а группы выходов первого и второго коммутаторов соединены со входами первого и второго частичных дешифраторов соответственно, группы выходов

Q которых соединены с первой и второй группами входов блока элементов И, третий выход блока управления соединен с входом блокировки генератора импульсов, четвертый выход блока управления - со входом сброса двоич-

ного счетчика, выход переполнения которого соединен с третьим входом блока управления.

Источники информации, принятые во внимание при экспертизе

свидетельство СССР 06 F 5/02, 1972.

свидетельство СССР 06 F 5/02, 1974

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь табличных кодов | 1984 |

|

SU1226671A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Функциональный генератор | 1980 |

|

SU926679A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Устройство для контроля программ на координатографе | 1983 |

|

SU1149219A1 |

| Устройство для последовательного программного управления | 1983 |

|

SU1126928A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для ввода информации | 1989 |

|

SU1649529A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

Авторы

Даты

1980-10-07—Публикация

1979-01-22—Подача