«

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и спедиализированньпс вычислительных устройствах.

.Цель изобретения - сокращение объема используемой памяти.

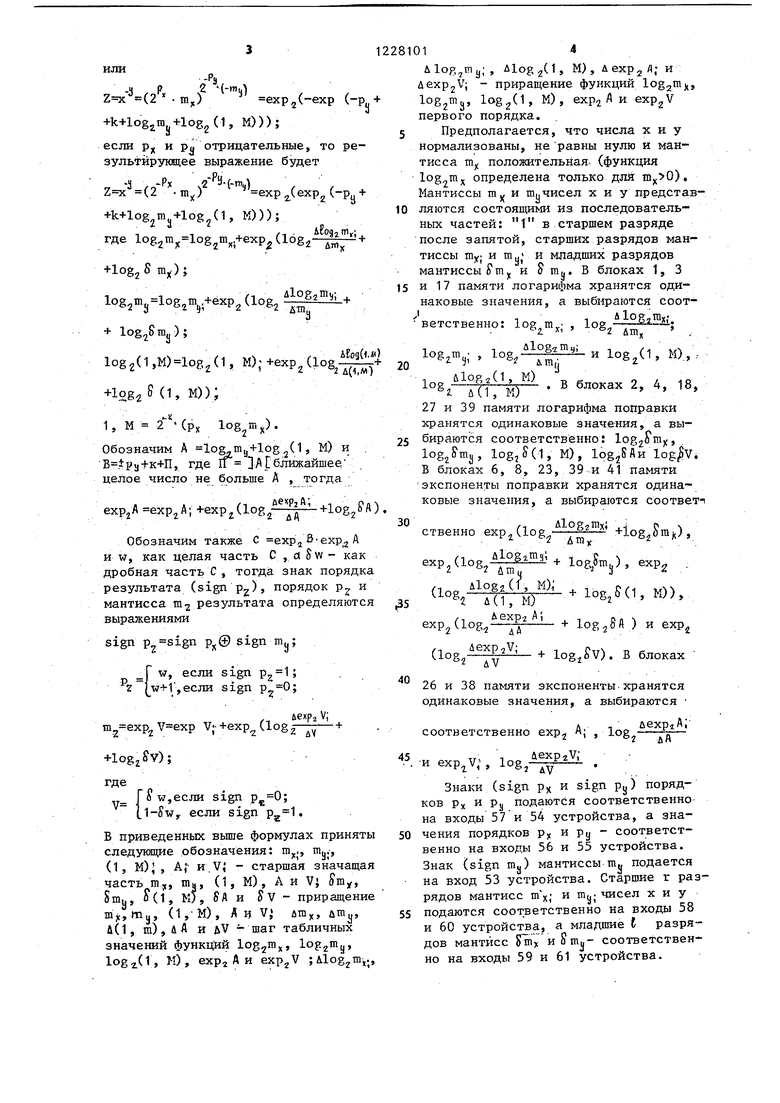

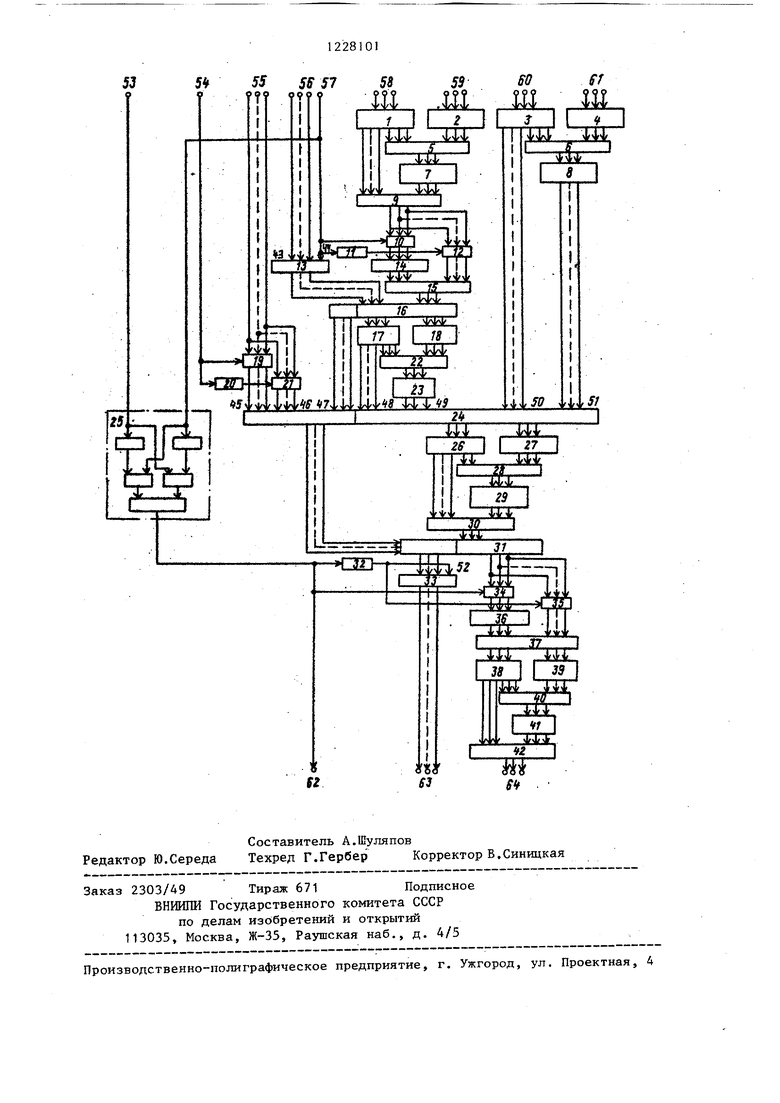

На чертеже представлена блок-схема устройства для возведения в степень.

Устройство содержит первый блок памяти логарифма, первый блок 2 памяти логарифма поправки, второй блок 3 памяти логарифма, второй блок А памяти логарифма поправки, первый и второй сумматоры 5 и 6 поправки, первый и второй блоки 7 и 8 памяти экспоненты поправки, второй сумматор 9, первую группу элементов И 10, первый элемент НЕ 11, вторую группу элементов И 12, первы счетчик 13, первьй блок 14 формирования дополнения, первую группу элементов ИЛИ 15, нормализатор 16, третий блок 17 памяти логарифма, третий блок 18 памяти логарифма поправки. Кроме того, устройство содержит группу элементов И 19, второй элемент НЕ 20, четвертую группу элементов И 21, третий сумматор 22 поправки, третий блок 23 памяти экспоненты поправки, первый сумматор 24, элемент ИСКЛЮЧАЩЕЕ ИЛИ 25, первый блок 26 памяти экспоненты, четвертьм блок 27 памяти логарифма поправки , четвертый сумматор 28 поправки, четвертый блок 29 памяти экспоненты поправки, третий сумматор 30, блок 31 сдвига, третий элемент НЕ 32, второй счетчик 33. Устройство содержит также пятую и шестую группы элементов И 34 и 35, вто- -рой блок 36 формирования дополнения вторую группу элементов ИЛИ 37, второй блок 38 памяти экспоненты, пятый блок 39 памяти логарифма поправки, пятый сумматор 40 поправки, пя- тьй блок 41 памяти экспоненты по- пр авки, четвертьй сумматор 42, информационный и управлякиций входы 43 и 44 счетчика 13, четвертый, пятый, третий, второй, седьмой, первый и шестой входы 45, 46, 47, 48, 49, 50 и 51 сумматора 24, управляющий вход 52 счетчика 33, входы 53 и 54 знаков мантиссы показателя и порядка степени устройства, входы 55 и 56 порядков показателя и основания сте281012

пени устройства, вход 57 знака порядка основания степени устройства, входы старших 58 и младших 59 разрядов мантиссы основания степени 5 устройства, входы.старших 60 и младших 61 разрядов мантиссы показателя степени устройства, выход знака 62 порядка результата устройства, выходы порядка 63 и мантиссы 64 ре- 10 зультата устройства.

Устройство для возведения в степень работает следующим образом.

Возведение в произвольную степень чисел, представленных в форме с пла- 15 вающей запятой ( т,, т, где TD, и m у - мантисса, а р и Рц - порядок X и у соответственно), с использованием операций Логарифмирования и экспоненцирования реализуется 20 по следующим алгоритмам.

При положительной степени (),

если р.. и PU положительные, то

,. р, .мц Рм (2 -mx) ехр2(2 .1п,,.(р +

25 +Iogjmx))exp,2(expz(pj,-Hog2mj,-Hogi f())exp(exp2(,

+log4(2- 1, М)))ехр (expj( k + +logjm,,+log2(1, M))).

Если PX или рц отрицательные, то результирующее выражение соответственно будет

9 у (2 тпд)..-«.

35 + k + log mj+log d, M)));

,

(2 -m,) exp2(exp2(-pj,+

+ k + lof, , M)));

30

.2 -my

exp,(-exp,.,(p,,+

40

если p и Pjj отрицательные, то результирующее выражение будет

ч -Рх (2 m J

сг- н-т.

exp2(-exp2(-p,j +

45 +k+log2m,jH-log,2(1, M))).

При отрицательной степени (), если р и Ру положительные, тс результирующее выражение будет

50

55

(),(-exp(p., +k+lop,2m,j+log2(1. К)));

,если PJ, или р отрицательные, то результирующее выражение соответственно будет

-а -р, /K-t- a) (2 -m,) exp,2(expj,(-py +

+k+logjmj+log2(1, К)));

или

-PS

.4 р 2 ( ( . ш,)

ехр2(-ехр

+k+logjm,j+log2(1, М)));

если PJ, и рц отрицательные, то зультирующее выражение будет

-%.(,)

ехр2.(ехр2((.,)

+k+log2m,j+log(l, М)));

где Iog,,in logjm.+exp2 (

logjS m);

log,,n,.,exp, (log,

+ );

log2(1,M)log,(1, M);+exp(

+iog2 S (1, M));

-К 1 , M 2 (px log,m p .

Обозначим A log,,m,,+log (1, M) и . , где ir ЗЛ ближайшее целое число не больше А , тогда

ехр,,А;+ехр,(1оЙ2.+1о8/А

Обозначим также С ехр2 ехрдА и W, как целая часть С , ci Sw - как дробная часть С, тогда знак порядка результата (sign р), порядок р и мантисса ш результата определяются выражениями

sign sign my;

р Г § г | то-н1 ,если sign

. дехрг V; m2 exp2V exp V; +exp(log +

+log2 V);

где

„ Гйw,ecли sign l-Swy если sign

Б приведенных вьше формулах приняты следующие обозначения: т,,,, т., (1, M)J , А} и,V - старшая зн ачащая часть т,, та, (1, М), А и V} Sm, Smj., u(1. К), SA и V - приращение m,ttiijj (1,-М), АН V, йш, um,j, Д(1, т), 4 А и дУ - шаг табличных значений функций logid, М), ехр2 А и ;4.1og2m,..

Д1ор,Шу;, , М),Дехр2Д;и Aexp2Vi - приращение функций , , , М), ехр2 А и первого порядка.

Предполагается, что числа х и у нормализованы, не равны нулю и ман тисса inj( положительная (функция log m,j определена только для ), Мантиссы та и Шмчисел хну представляются состоящими из последовательных частей: 1 в старшем разряде после запятой, старших разрядов мантиссы Шу; и и младших разрядов мантиссы tn и га,.. В блоках 1, 3

и 17 памяти логарифма хранятся одинаковые значения, а выбираются соответственно: log т,, , log

log,.. ,log,.,0,Ю,,

log,fffP . в блоках 2, 4, 18,

27 и 39 памяти логарифма поправки хранятся одинаковые значения, а вы- бираются соответственно: , log,.,m,j, log, S(1, M), log2SAи , В блоках 6, 8, 23, 39 и 41 памяти экспоненты поправки хранятся одинаковые значения, а выбираются соответт

ственно exp,( ), ,,Ц),ехр, .

/т iloggCf, М), , - г,,. „. ,.

°g А(1,М) .

exp dog -SSl-L. + ) и exp,j

( + log.V). В блоках

26 и 38 памяти экспоненты-хранятся одинаковые значения, а выбираются

соответственно

expj А; , log,

uA

„ exp.v; , log,lHP .

Знаки (sign px и sign Py) порядков Py и РЛ подаются соответственно на входы 57 и 54 устройства, а значения порядков р и Ру - соответственно на входы 56 и 55 устройства. Знак (sign Шу) мантиссы Год подается на вход 53 устройства. Старшие г разрядов мантисс т х; и чисел х и у

подаются соответственно на входы 58 и 60 устройства, а младшие t разрядов мантисс Гтх соответственно на входы 59 и 61 устройства.

Из блока 3 памяти логарифма выбираются значения и .

PlPji и

um.,

поступают соответственно

на первые входы 50 суммирования сумматора 24 и на первые входы сумматора 6 поправки, на вторые входы которого поступает значение из блока 4 памяти логарифма поправки. В сумматоре 6 поправки вычисляется

lopj,Alog tny;

urn,,

log, У

га,, и по

полученному значению из блока 8 памяти экспоненты поправки выбирается

значение exp dog- .+ logjEm.),

2 лт,.

которое передается на шестые входы 51 суммирования сумматора 24.

Одновременно с этим из блока 1. памяти логарифма выбираются значения

11 Л1ОР2П1 ri

log-m и lop. и поступают на

Ainj(

первые входы соответственно сумматора 9 и сумматора 5 поправки, на вторые входы которого поступает значение из блока 2 памяти логарифма поправки. В сумматоре 5 поправ1 ul OR, п.; ки вычисляется сумма loR,- 2-1 +

i &Щ

,K по полученному значению из блока 7 памяти экспоненты Поправки выбирается значение ехр (log- . ), которое передаU Шц

ется на вторые входы сумматора 9. В сумматоре 9 вычисляется сумма,т.е. зна1 V fi loe,m. чение Iog2ni lo),.+exp(

, с л.

+lopbifi), и поступает на информационны

входы групп элементов И 10 и И 12. Если порядок РЖ отрицательньй, то сигнал с входа 57 устройства открьшает группу элементов И 10, подключая выходы сумматора 9 к входам блока 14 формирования дополнения. В блоке 14 значение log т, преобразуется в дополнительный код (вычисляется значение 1-1 ) и через группу элементов ИЛИ 15 поступает на первые входы нормализатора 16. Одновременно с эти порядок с входов 56 устройства посту пает в счетчик 13, а сигнал с входа 57 устройства подается на вход 44 Вычитание единицы счетчика 13. В

результате в счетчике 13 вычисляется разность (рх-1), если знак порядка р отрицательный. Результат () или Pj (для положительного р, ) с выходов счетчика 13 поступает на вторые входы нормализатора 16. Если порядок Ру положительный, то сигнал с входа. 57 устройства через элемент НЕ 11 подается на управлякщий вход группы элементов И 12, подключая выходы сумматора 9 через группу элементов И 12 и группу элементов ИЛИ 15 и первым входом нормализатора 16. Таким образом, в нормализатор 16 поступает логарифм основания степени (). - целая часть из счетчика 13, а дробная часть из блока 14 формирования дополнения или из сумматора 9. Нормализатор 16 выполняет нормализацию числа на его входах, форкшруя на выходах старших разрядов характеристику k , а на выходах младших разрядов - нормализованную мантиссу, представленную положительным числом 1,М (М - произвольная комбинация двоичных нулей и единиц). По.значению (1, M)j старшей части младших разрядов нормализатора 16 из блока 17 памяти логарифма выбираются значения

, Ю, и

uloggd, М);

М)

и по

, uiogat.

сумма log,-TTi

ди ,

ступают соответственно на вторые входы 48 суммирования сумматора 24 и на первые входы сумматора 22 поправки. На вторые входы сумматора 22 поправки поступает значение log,J(1,M), выбираемое по значению (1,М) младшей части младших разрядов нормализатора 16 из блока 18 памяти логарифма поправки, и в сумматоре 22 вычисляется

М); ).

М)

По полученной сумме из блока 23 памяти экспоненты поправки выбирается

ехо flop l°g.); ./. „ч +

значение

Д(1,М)

+ , М)) и передается на седьмой вход 49 суммирования сумматора 24. Таким образом, в малых разрядах сумматора 24 вычисляется сумма А

1ор (1 К)- + ехр (1ор ul°Pz(1.M)i +

ifgjVI, liA exp VlOJ jдх-7 57

+ , М)) + log,, + exp(log2 + lop,ym,j)log,,(1,M)nog,m,,.

Значение k из старших разрядов нор .мализатора 16 поступает на третьи входы 47 суммирования сумматора 24. Порядок р. с входов 55 устройства поступает на информационные входы групп памяти И 19 и И 21. Если порядок Рц положительньй, то сигнал с входа 54 устройства открьшает группу элементов И 19 и порядок Рц поступает на входы 45 вычитания сумматора 24. Если порядок p положительньй, то сигнал с вхбда 54 устройства через элемент НЕ 20 открьюает группу элементов И 21 и порядок р поступает на пятые входы 46 суммирования сумматора 24. Таким образом, в старших разрядах сумматора 24 вычисляется разность В (с -Р + П или сумма В К + П , где П - возможный перенос из младших разрядов.

Знак sign р порядка результата определяет элементом ИСКЛЮЧАЩЕЕ ШШ, реализующий логическую функцию Сумма по модулю 2, и подается на выход 62 устройства.

По значению А; , содержащемуся в старшей части младших разрядов сумматора 24, из блока 26 памяти экспоненты выбираются значения

- лехр2А, и log Ifм поступают на первые

ДМ

входы соответственно сумматора 30 и сумматора 28 поправки. По значению Уд , содержащемуся в младшей части младших разрядов сумматора 24, из блока 27 памяти логарифма поправки выбирается значение и поступает на вторые входы сумматора 28 поЛравки. В сумматоре 28 вычисляется

дехргА; , гл

+ , по котосумма дд

рой из блока 29 памяти экспоненты

поправки выбирается значение ехр (log, + ) и передается

на вторые входы сумматора 30. В сумматоре 30 вычисляется сумма, т.е.

значение ехр2А ехр2 А;

Д expzA; , г.. ч

--д+ log ) и поступает на

информационные входы блока 31 сдвига, а на другие его входы подается значение В из старших разрядов сумматора 24. Блок 31 сдвига осуществляет сдвиг значения ехр., А вправо или влево в зависимости от знака В на число разрядов, равное числу Р ,

10

281018

т.е. вычисляется с ехр 6 ехр2А . Таким образом, на выходах блока 31 сдвига уст анавливается целая часть W в старших разрядах и дробная часть 5 8w в младших разрядах. Значение Fw с выходов младших разрядов блока 31 сдвига поступает на информационные входы групп элементов И 39 и И 40, а значение w с вьшодов старших разрядов - в счетчик 33.

При отрицательном порядке результата на выходе элемента исключакицее ИЛИ 25 устанавливается Единичный сигнал, который открьшает группу

15 элементов И 39, подключая выходы младших разрядов блока 31 сдвига к входам блока 36 формирования дополнения. В блоке 36 вычисляется дополнение V (1- Jw) - дополнительный

20 код значения (-Sw). При положительном порядке результата на выходе элемента ИСКЛЮЧАЮЩЕЕ ШШ 25 формируется Нулевой сигнал, который через элемент НЕ 32 открьшает группу

25 элементов И 35, подключая выходы младших разрядов блока 31 сдвига к входам группы элементов ИЛИ 37. По значению V; старших разрядов группы элементов ИЛИ 37 из блока 38 памяти экспоненты выбираются

д ехр .У,. 2 uV

и посылаются на первые входы соответственно сумматора 42 и сумматора 35 40. поправки. По значению Sv младших разрядов группы элементов ИЖ 37 из блока 39 памяти логарифма поправки выбирается значение и посылается на вторые входы сумматора 40 поправки. В. сумматоре 40 вычист aexpi V, , 1 л„ ляется сумма logv + log iV,

по которой из блока 41 памяти экспоненты поправки выбирается значение

30

40

45

ся значения , log

.-, uexp 2 V; exp,,(log2- + ) и ПОСЫЛУ .„

лается на вторые входы сумматора 42.

В сумматоре 42 вычисляется сумма, т.е. мантисса т, ехр У- + ехр. (log

50 AV

-- + ) результата , и подается на выходы 64 устройства. Одновременно с этим значение w из старших разрядов блока 31 сдвига посту- пает в счетчик 33. При отрицательном порядке результата на вход 52 Сложение единицы счетчика 33 сигнал не подается и содержимое w счетчика 33,

т.е. порядок Рг W результата подается на выходы 63 устройства. При положительном, порядке -результата на вход 52 Сложение единицы счетчика 33 подается сигнал, с его содержимым (w) суммируется единица и результат (w+1), т.е. порядок р W+1, подается на выходы 63 устройства.

Мантисса т результата на выходах 64 устройства всегда получается нормализованной и положительной.

Формула изобретения

Устройство для возведения в степень, содержащее три блока памяти логарифма, два блока памяти экспоненты, первый сумматор, нормализатор, блок сдвига, два счетчика, два блока формирования дополнения, шесть групп элементов И, две группы элементов ИЛИ, три элемента НЕ и элемент ИС- 1ШЮЧАЮЩЕЕ ИЛИ, причем старшие разряды вкода мантиссы основания степени устройства соединены с адресным входом первого блока памяти логарифма, старшие разряды вкода мантиссы показателя степени устройства, подключены к адресному входу второго блока памяти логарифма, выходы стар- пшх разрядов которого соединены с первой группой входов первого сумматора, вход знака порядка основания степени устройства подключен к управляющему входу первого счетчика, управлякнцим входам элементов И первой группы, входу первого элемента НЕ и к первому входу элемента ИС1ШО- ЧАЩЕЕ ИЛИ;, выходы элементов И первой группы подключены к входам первого блока формирования дополнения, разрядные входы которого подключены к первым входам элементов ИЛИ первой группы, вторые входы которых соединены с выходами элементов И второй группы, выходы элементов ИЛИ первой группы подключены к входу мантиссы нормализатора, вход порядка которого соединен с выходом первого счетика, информационньй вход которого одключен к входу порядка основания тепени устройства, выход первого лемента НЕ соединен с управляющими ходами элементов И второй группы, ыходы старшей части младших разряов норма.лизатопа соединены с адресыми входами третьего блока памяти огарифма выход старших разрядов

которого подключен к второму входу первого сумматора, третий вход .кото- рого соединен с выходом старших разрядов нормализатора, четвертьй и

пятьй входы первого сумматора соединены соответственно с выходами элементов И третьей и четвертой групп, информационные входы которых подгао- чены к входу порядка показателя степени устройства, вход ..знака порядка показателя степени устройства соединен с управляющими входами элементов И третьей группы и входом второго элемента НЕ, выход которого

подключен к управляющим входам элементов И четвертой группы, выходы старшей части младших разрядов первого сумматора соединены с адресными входами первого блока памяти экспоненты, выходы старших разрядов первого сумматора соединены с входами управления сдвигом блока сдвига, выхо ды младших разрядов которого подключены к информационным входам злементов И пятой и шестой групп, выходы элементов И пятой группы подсоединены к входам второго блока формирования дополнения, разрядные входы которого подключены к первым входам элементов ИЛИ второй группы, вторые входы которых соединены с выходами эле- . ментов И шестой группы, первая группа выходов элементов ИЛИ второй группы подключена, к адресным входам второго блока памяти экспоненты, вход знака мантиссы показателя степени устройства подключен к второму входу элемента ИСКЛ10ЧАЮЩЕ.Е ИЛИ, выход которого соединен с управляющими входами элементов И пятой группы, выходом знака порядка результата .устройства и входом третьего элемента НЕ, выход которого пoдкJпoчeн к управляющим входам элементов И шестой группы и к управляющему входу второго счетчика, информационные входы которого соединены с выходами старших разрядов блока сдвига, выход второго, счетчика подключен к выходу порядка результата устройства, отличающееся

тем, что, с целью сокращения объема используемой памяти, в него введены пять блоков памяти логарифма поправки, пять блоков памяти экспоненты поправки, пять сумматоров поправки,

три сумматора, входы младшвх разрядов мантиссы основания степени устройства соединены с aдpecны и входами первого блока памяти логарифма поп

11

равки, группы выходов старших и младших разрядов первого блока памяти логарифма соединены соответственно с первыми входами второго сумматора и первого сумматора поправки, выход перво- го блока памяти логарифма поправки подключен к второму входу первого сумматора поправки, выход которого соединен с адресным входом первого блока памяти экспоненты поправки, выход которого соединен с вторым входом второго сумматор а, выходы которого подключены к информационным входам элементов И первой и второй групп выходы младших разрядов второго бло- ка памяти логарифма соединены с первой группой входов второго сумматора поправки, входы младших разрядов мантиссы показателя .степени устройства подключены к-адресным входам второ- го блока памяти логарифма поправки, выход которого сбединен с вторым входом второго сумматора поправки, выход которого соединен с адресным входом второго блока памяти экспоненты поправки, выходы которого подключены к шестому входу первого сумматора, выходы младших разрядов третьего блока памяти логарифма соединены с первым входом третьего сумматора по- правки, разрядные .выходы младшей, части младших разрядов нормализатора . соединены с адресным входом третьего блока памяти логарифма поправки, выход которого соединен с входом третьего сумматора поправки, вькод

101

12

которого подключен к адресному входу третьего блока памяти экспоненты поправки, лыход которого соединен с седьмым входом первого сумматора, выходы старших и младших разрядов первого блока памяти экспоненты соединены соответственно с первыми входами третьего и четвертого сумматоров поправки, разрядные выходы младшей части младших разрядов первого сумматора соединены с адресным входом четвертого блока памяти логарифма поправки, выход которого соединен с вторым входом четвертого сумматора поправки, выход которого соединен с адресным входом четвертого блока памяти экспоненты поправки, выход которого соединен с информационным входом блока сдвига, разрядные выходы старших и младших разрядов второго блока памяти экспоненты соединены соответственно с первыми входами четвертого и пятого сумматоров поправки, вторая группа выходов элементов ИЛИ второй группы соединена с адресным входом пятого блока памяти логарифма поправки, выход которого соединен с вторыми входами пятого сумматора поправки, выход которого соединен с адресным входом пятого блока памяти экспоненты поправки, выход которого подключен к второму входу четвертого сз матрра, выход которого соединен с выходом мантиссы результата устройства.

53

5

5S 5f 57

58

59

BO

ff

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень | 1984 |

|

SU1171788A1 |

| Вычислительное устройство | 1988 |

|

SU1531091A1 |

| Цифровое вычислительное устройство | 1973 |

|

SU474012A2 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU409226A1 |

| Устройство для деления | 1986 |

|

SU1361545A1 |

| Вычислительное устройство | 1986 |

|

SU1399735A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1464156A1 |

| Цифровое логарифмическое устройство | 1983 |

|

SU1101819A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1986 |

|

RU2022338C1 |

| Цифровое логарифмирующее устройство | 1985 |

|

SU1262490A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и специализированных вычислительных устройствах. Цель изобретения - сокращение объема используемой памяти. Устройство содержит шестнадцать блоков памяти, восемь сумматоров, два блока элементов ИЛИ, четыре блока элементов И, два элемента НЕ, блок .формирования дополнения, блок сдвига, нормализатор. 1 ил.

---€

2ff

г

Ж.

I

}

ИмГ

;Ti

jr

о Mr w

t Jf Л

f2

JZ.

«I П

Составитель А.Шуляпов Редактор Ю.Середа Техред Г.Гербер Корректор В.Синицкая

- -----

Заказ 2303/49 Тираж 671 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для возведения в степень | 1984 |

|

SU1171788A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-30—Публикация

1984-05-21—Подача