торого подсоединен к входу знака порядка основания степени устройства, а выход соединен с управляющими входами элементов И нятой группы, выходом знака порядка результата устройства и входом третьего элемента НЕ, выход которого подключен к управляющим входам

элементов И щестой группы и к зттравляющему входу второго счетчика, информационные входы которого соединены с выходами старщих разрядов сумматора, а выходы - с выходом порядка результата устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень | 1984 |

|

SU1228101A1 |

| Вычислительное устройство | 1988 |

|

SU1531091A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для сложения последовательности чисел с плавающей запятой | 1984 |

|

SU1182512A1 |

| Устройство для вычисления экспоненциальной функции | 1986 |

|

SU1465884A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

УСТГОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ, содержащее два блока памяти, сдвигатель, сумматор, два элемента НЕ, о тл и чающее.с я тем, что, с целью расширения области применения за счет возведения в степень произвольных чисел, представленных в форме с плавающей запятой, в него введены три блока памяти, два счетчика, два блока формирования дополнения, нормализатор, элемент ИСКЛЮЧАКИЦЕЕ ИЛИ, третий злемент НЕ, шесть групп элементов И, две труппы элементов ИЛИ, адресные входы первого и второго блоков памяти соединены соответственно с входами мантиссы показателя степени и мантиссы основания степени устройства, выход первого блока памяти подключен к первому входу сумматора, выход второго блока памяти подключен к информационным входам элементов И первой и второй групп, выходы элементов И первой группы подключены к входам первого блока формирования дополнения, выходы которого подключены к первым входам элементов ИЛИ первой группы,вторые входы которых соединены с выходами элементов И второй группы, выходы элементов ИЛИ первой группы подключены к входам первой группы нормализатора, входы второй группы которого соединены с выходами первого счетчика, информационные входы которого подклю чены к входам порядка основания степени устройства, вход знака порядка основания степени- устройства соединен с управляющим входом первого счетчика, управляющими входами злементов И первой группы и входом первого злемента НЕ, выход которого подключен к управляющим входам злементов И второй группы, адресные входы третьего блока памяти соединены с выходами младших разрядов нормализатора, а выход подключен к второму входу .сумматора, третий вход которого соединен с выходами старших разрядов нормализатора, четвертый и пятый входы сумматора соединены соответственно с выходами злементов И третьей и четвертой групп, информациошгые входы которых подключейы к входу т порядка показателя степени устройства, вход знака порядка показателя степени устройства соединен с управляющими входами злементов . И третьей группы и входом второго элемента НЕ, выход которого подключен к управляющим входам злементов И четвертой группы, адресные входы четвертого блока памяти подключены к выходам младших разрядов сумматора, а выход подключен к информационному входу сдвигателя, управляющий вход которого 00 00 соединен с выходами старших разрядов сумматора, выходы младших разрядов сдвигателя подключены к информационным входам элемен тов И пятой и шестой групп, выходы элементов И пятой группы подключены к входам второго блока формирования дополнения, выход которого подключен к первым входам элементов ИЛИ второй группы, вторые входы которых соединены с выходами элементов И шестой группы, а выходы подключены к адресным входам пятого блока памяти, выход которого подсоединен к выходу мантиссы результата устройства, вход знака мантиссы показателя степени устройства подключен к первому входу элемента ИСК.ПЮТАНЩЕЕ ИЛИ, второй вход ко

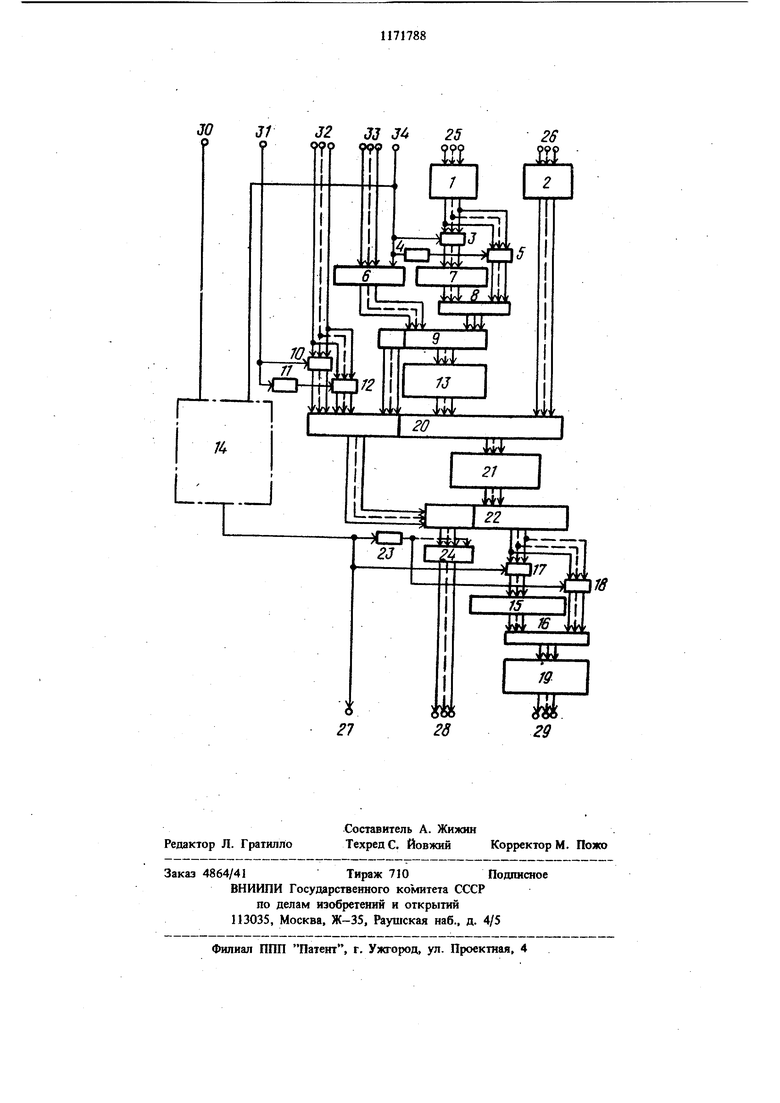

Изобретение относится к вычислительной тех нике и может быть использовано в цифровых вычислительных машинах и специализированных вычислительных устройствах. Цель изобретения - расщирение области при менения устройства за счет возведения в степе произвольных чисел, представленных в форме с плавающей запятой. На. чертеже представлена блок-схема устройства. Устройство содержит блоки 1 и 2 памяти (логарифма), группу элементов .ИЗ, элемент НЕ4, группу элементов И5, счетчик 6, блок 7 формирования дополнения, группу элементов ИЛИ8, нормализатор 9, группу элементов И10, элемент ЙЕН, группу элементов И12, блок 13 памяти (логарифма), элемент ИСКЛЮЧАНЩЕЕ ИЛИ 14, блок 15 формирования дополнения, группу элементов ИЛИ 16, группы элементов И 17 и 18, блок 19 памяти (экспоненты), сумматор 20, блок 21 памяти (экспоненты), сдвигатель 22, элемент НЕ 23, счетчик 24, вход 25 мантиссы основания степени, вход 25 мантиссы показателя степени, выход 27 знака порядка результата, выход 28 порядка результата, выход 29 мантиссы результата, -. вход 30 знака мантиссы показателя степени устройства, вход 31 знака порядка показателя степени, вход 32 порядка показателя степени, вход 33 порядка основания степени, вход 34 знака порядка основания степени. Устройство работает следующим образом. Возведение в произвольную степень чисел, представпейных в форме с плавающей запятой (х 2т, ,, , где т йт -мантисса, а РХ и Ру - порядок х и ч соответственно), с с использованием операций логарифмирования и экспоненцирования, реализуется по следующим алгоритмам. При положительной степени (), если РХ И Ру положительные, то (2 т) - ехр2(2т.,(Р,Ч2%)) exp2(exp,j ( ( )) ехр2 (ехрДр,,. Ео, m. «о Д 2 . 1, м))) Eog-jm i + ) , Если РХ или Ру отрицательные, то результирующее выражение равно г-щ% j ,(щ(-р,))V, / -р., 2 m, . . Z)( 2 m,) (-ехрДР,.К.(о,т (of.M)) Если РХ и Ру отрицательные, то результирующее выражение равно Vj (-€xp2(:P., + Во,1,«)) ) При отрицательной степени (т.,0), если РХ и Ру положительные, то результирующее выражение равно -V / Р, 1 ( 2 (:ехр2(Р,,+ к + Ро,„ + 4go,-f,M)) . Если РХ или Ру отрицательные, то результирующее выражение соответственно равно 7 , Х 2 (ехрДр,,+ .,4 )) илир -V / РХ Y( (2 (;exp2(-P,-K+eo 2m,,+ .M)) . Если РХ и Ру отрицательные, то результирующее выражение равно , -t / -РХ г (,) (2 (exp2(-R,, Чг.м)) , где l,M 2 lPx+eo5:,mJ. обозначим 4 eog-2mj + ,M и Ру4 ., где - ближайшее целое число, не больше А, а также обозначим ы - как целзто часть с , а fu) - как дробную ччль С, тогда знак порядка результата, порядок Р и мантисса mj результата определяются выражениями Р., г , ® т , U) , если Pj r, UJ+1 , если giifn Р 0; .и , Г .сЛю , если , если 3i&-n Р2 1; Числа X и :) нормализованы, не равны нулю и мантисса т положительная (для отрицательных т нет действительного значения Со В блоках 1, 2 и 13 памя ти (логарифма) хранятся значения логарифмов нормализованных чисел и выбираются соот ветственно значения j 1, л (ти блоки памяти взаимозаменяемы), а в блоках 21 и 19 памяти (зкспонен ты) хранятся значения зкспоненты и выбирак/гея соответственно значения ехр Л и expjL (зти блоки также взаимозаменяемы). Знаки Sign Р и sig-n Ру порядков РХ и Ру подаются соответственно на вход 34 знака порядка основания степени и вход 31 знака порядка показателя степени устройства, а значения порядков РХ и Ру - соответственно на вход 33 порядка основания степени и вход 32 порядка показателя степени устройства. Знак ,j мантиссы т подает ся на вход 30 знака мантиссы показателя ст пени устройства, а значения мантисс и m у подаются соответственно на вход 25 ман тиссы основания степени и на вход 26 мантиссы показателя степени устройства.. Из блока 1 памяти (логарифма) выбирается значение Во к поступает на информационные входы групп элементов И 3 и 5. Если порядок РХ отрицательный, то сигнал с входа 34 знака порядка основания степени устройства открывает группу элементов И 3, подключая выходы блока 1 памяти (логариф ма) к входам блока 7 формирования дополнения. В блоке 7 значение fog-. m преобразуется в дополнительный код (вычисляется значение J во х ) и через группу элементов ИЛИ 8 поступает на входы первой группы нормализатора 9. Одновременно с зтим порядок РХ с входа 33 порядка основания степени устройства поступает в счетчик 6, а сигнал с входа 34 знака порядка основания степени устройства подается на вход Вычитание единицы счетчика 6. В результате в последнем вычисляется разность (Рх-1), если знак порядка РХ отрицателен. Результат (РХ - I) для положительного РХ с выходов счетчика 6 поступает на вторые входы нормализатора 9. Если порядок РХ положительный, то сигнал с входа 34 знака порядка основания степени устройства через элемент НЕ 4 подается на управляющий вход группы элементов И 5, подключая выходы блока 1 памяти (логарифма) через группь элементов И 5 и ИЛИ 8 к первым входам нормализатора 9. Таким образом, в нормализатор 9 поступают целая часть из счетчика 6 и дробная часть из блока 7 формирования дополнения или из блока 1 памяти (логарифма). Нормализатор 9 выполняет нормализацию числа на его входах, формируя на выходах старших разрядов характеристику k , а на выхо дах младших разрядов - нормализационную мантиссу, представленную положительным числом (1,М), где М - произвольная комбинация двоичных нулей и едиииц. По значению 1 ,М младших разрядов нормализатора 9 из блока 13 памяти (логарифма) выбирается значение foo- 1,М и поступает на вторые входы суммирования сумматора 20, а на его первые входы суммирования поступает значение о у выбираемое из блока 2 памяти (логарифма). В младших разрядах сумматора 20 вычисляется сумма А о 1,М + + Ео m,j . Значение К из старших разрядов нормализатора 9 поступает на третьи входы суммирования сумматора 20. Порядок Ру с входа 32 порядка показателя степени устройства поступает на информационные входы групп элементов И 10 и 12. Если порядок Ру отрицательный, то сигнал с входа 31 знака порядка показателя степени устройства открывает третью группу элементов И 10 и порядок Ру поступает на входы вычитания сумматора 20. Если порядок Ру положительный, то сигнал с входа 31 знака порядка показателя степени устройства через элемент НЕ 11 открывает четвертую группу злементов И 12 и порядок Ру поступает на четвертые входы суммирования сумматора 20. Таким образом, в старших разрядах сумматора 20 вычисляется разность В К PV + П или сумма В К + Ру + П, где П А ближайшее целое число, не больше А, т.е. возможен перенос из младших разрядов. Знак порядка результата определяется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и подается на выход 27 знака порядка результата устройства. По значению А , содержащемуся в младих разрядах сумматора 20, из блока 21 памяти (экспоненты) выбирается значение экспоненты expj А и поступает на первые входы сдвигателя 22, а на другие его входы подается значение, В из старших разрядов сумматора 20. Сдвигатель 22 осуществляет сдвиг значения ехр вправо или влево в зависимости от знака 8 на число разрядов, равное числу В . Таким образом, на выходах сдвигателя 22 устанавливается целая часть to в старших разрядах и дробная часть cfui в младших разрядах. Значение сГш с выходов младших разрядов сдвигателя 22 поступает на информационные входы элементов И 17 и 18, а значение ш с выходов старших разрядов - в счётчик 24. При отрицательном порядке результата на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 устанавливается единичный сигнал, который открывает элементов И 17, подключая выходы младших разрядов сдвигателя 22 к входам блока 15 формирования дополнения. В блоке 15 вычисляется дополнение 0 1 - - с/хо - дополнительный код значения (-cfw ) и через группу элементов ИЛИ 16 поступает на адресный вход блока 19 памяти (экспоненты), соответственно которому из бло ка 19 выбирается значение экспоненты, т.е, м мантиссы m2 expjU результата, и подается на выходы 29 мантиссы результата устройства. В этом случае на вход Сложение единицы счетчика 24 сигнал не подается и его содержимое, т.е. порядок ) результата, передается на выход 28 порядка результата устройства. При положительном порядке результата на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 формируется нулевой сигнал, который через элемент НЕ 23 открывает элементы И 18, подключая выходы младших разрядов сдвигателя 22 к адресному входу блока 19 памяти (экспоненты) . Из блока 19 выбирается значение экспоненты, т.е. мантисса т ехр U результата, и подается на выход 29 мантиссы результата устройства. Одновременно с этим сигнал с выхода элемента НЕ 23 поступает на вход Сложение единицы счетчика 24, с его содержимым суммируется единица и результат, т.е. порядок р2 W + 1,. подается на выходы 28 порядка результата устройства. Мантисса т результата на выходе 29 мантиссы результата устройства всегда получается нормализованной и положительной.

29

28

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-07—Публикация

1984-03-07—Подача