Изобретение относится к цифровой и преобразовательной технике и предназначается в основном для использования в электроприводах постоянного и переменного токов с цифровым управлением.

Варианты изобретения объединены единым замыслом, состоящим в обнаружении ошибки функционирования на каждом такте работы, и характеризуют особенности выполнения устройства при нечетном и четном числах разрядов .

Цель изобретения - повышение достоверности функционирования.

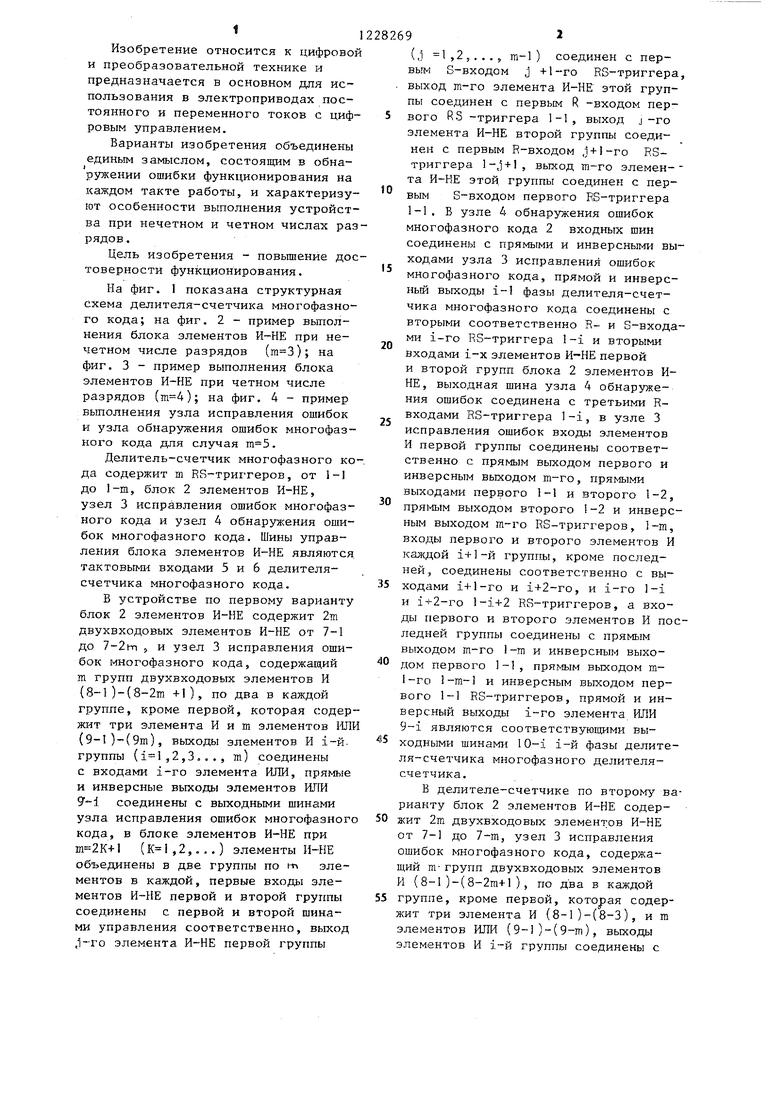

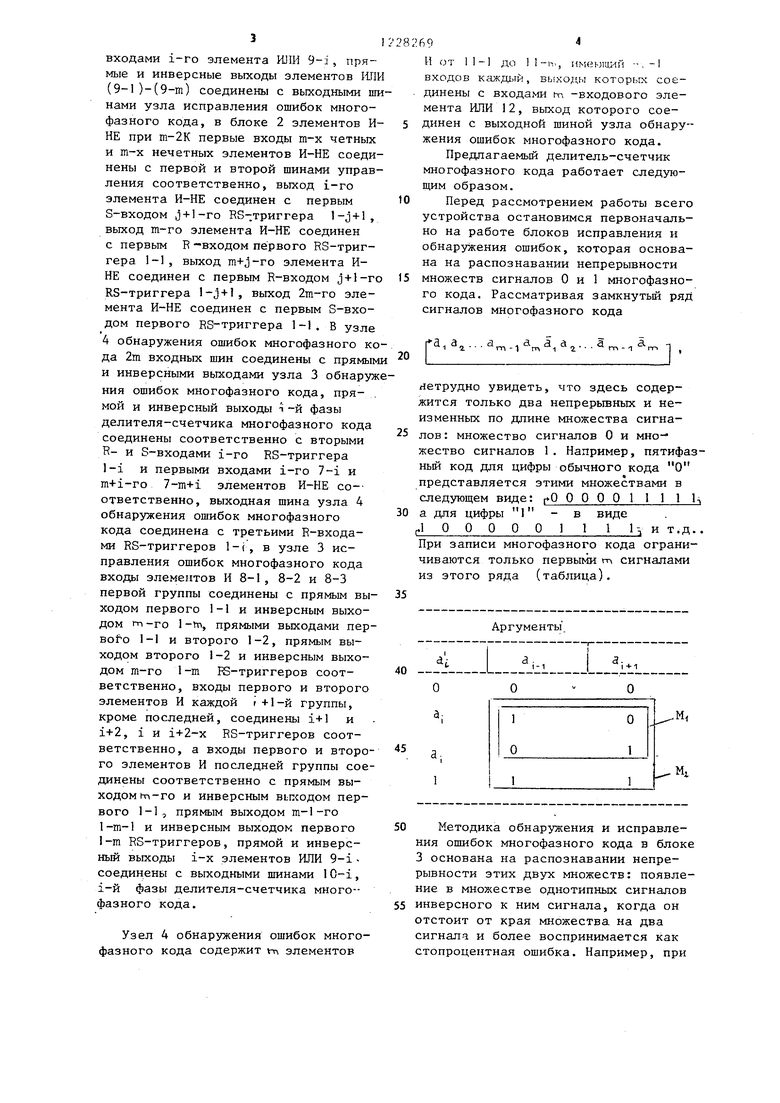

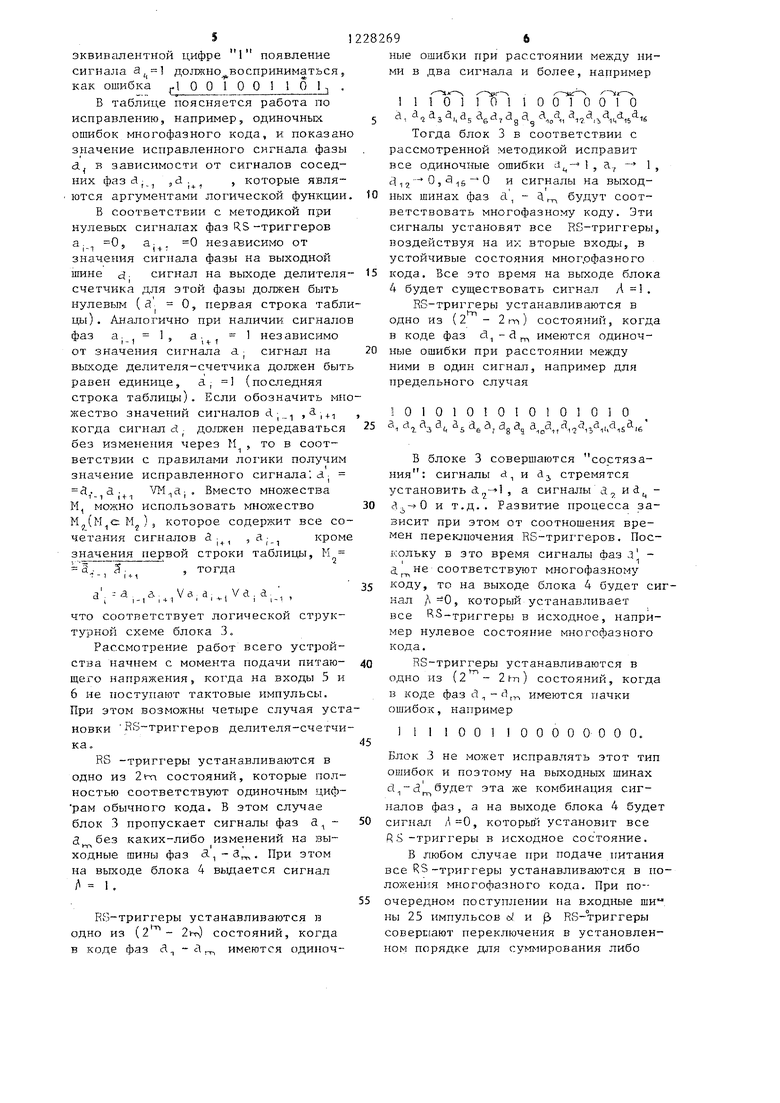

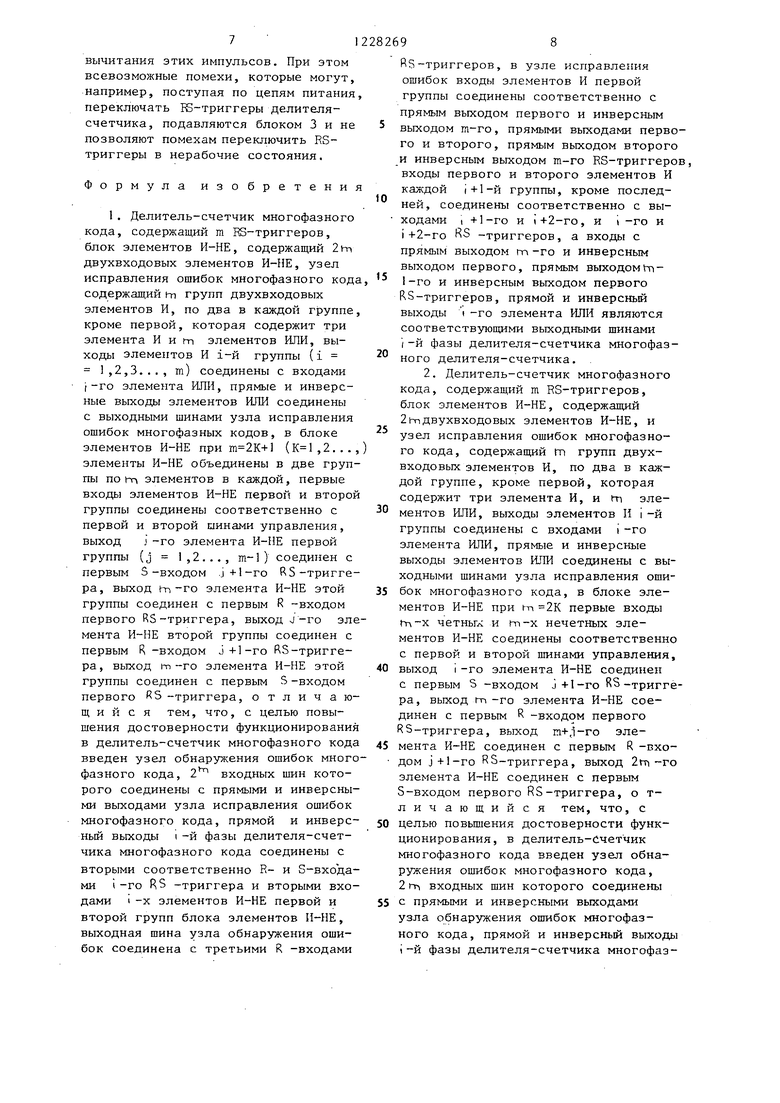

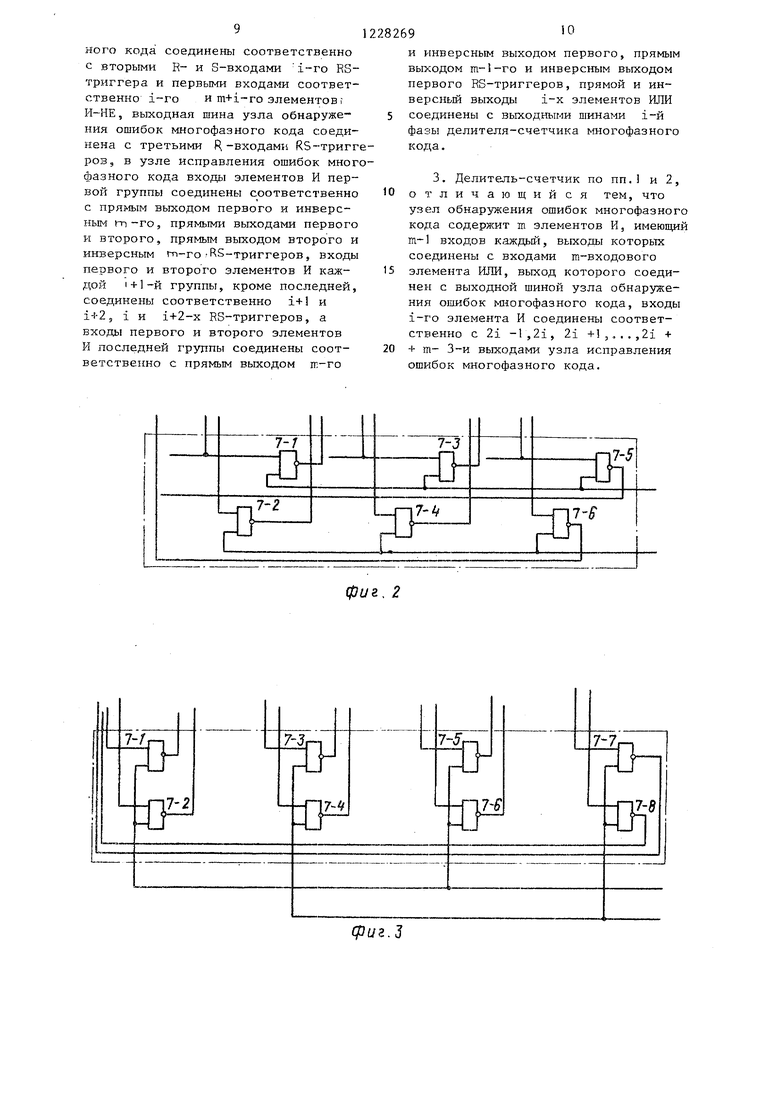

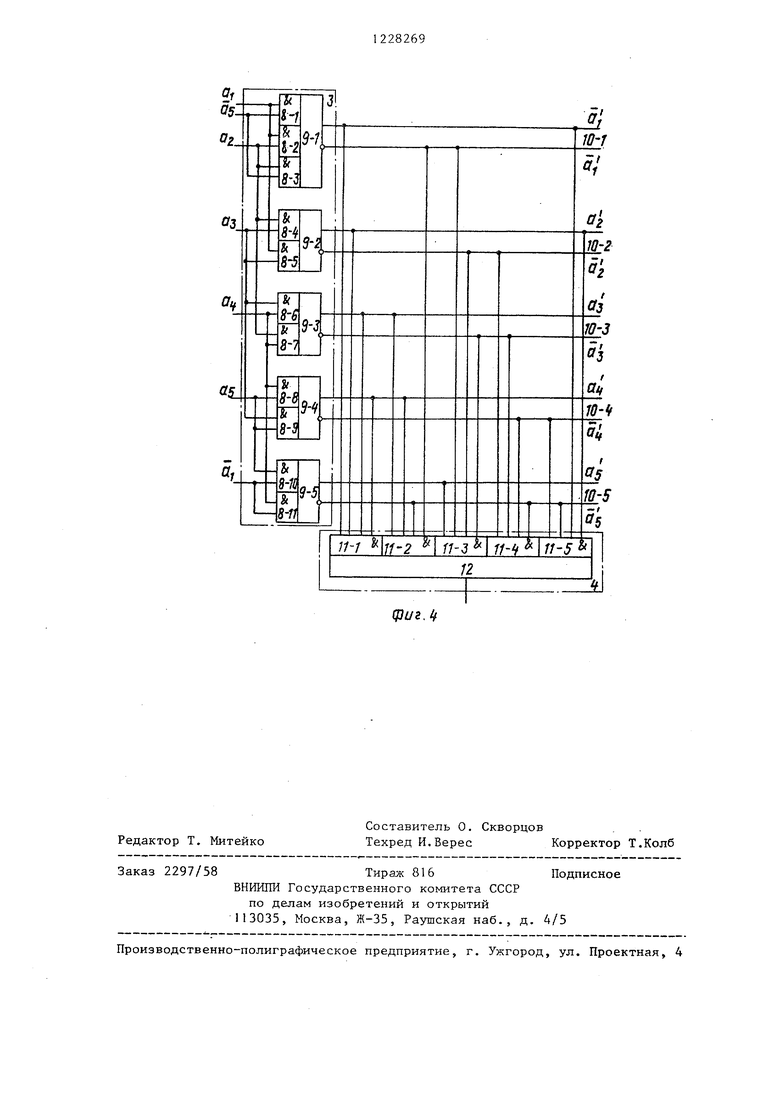

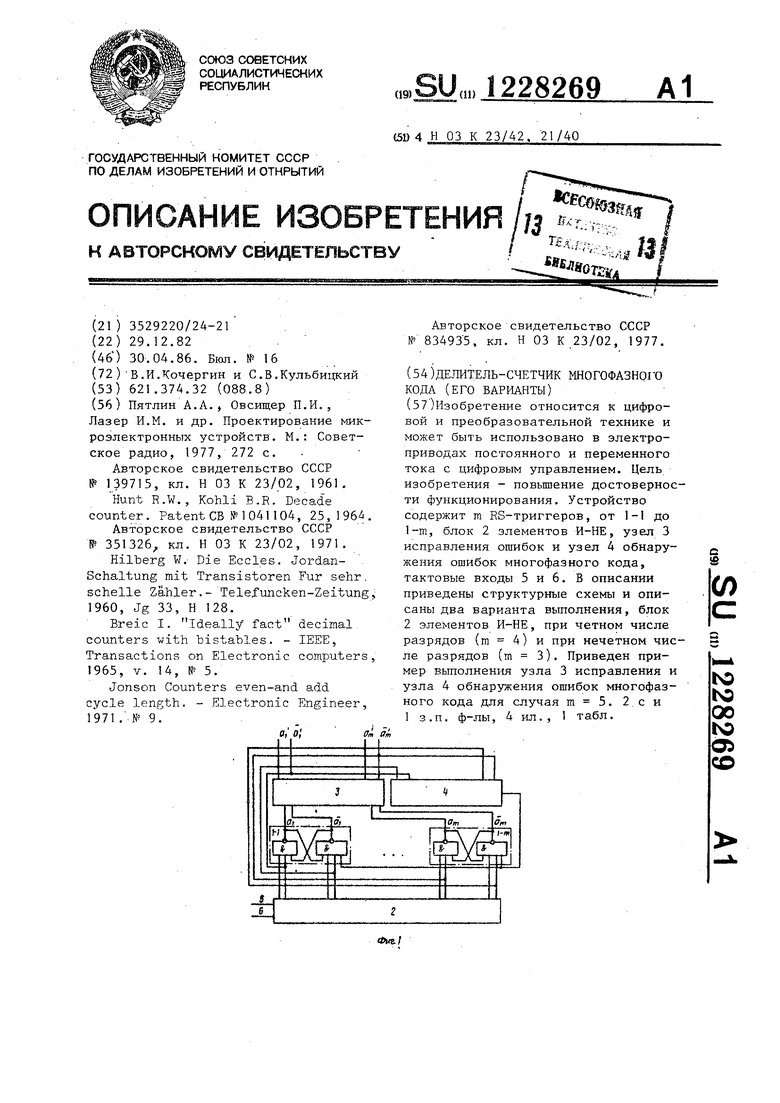

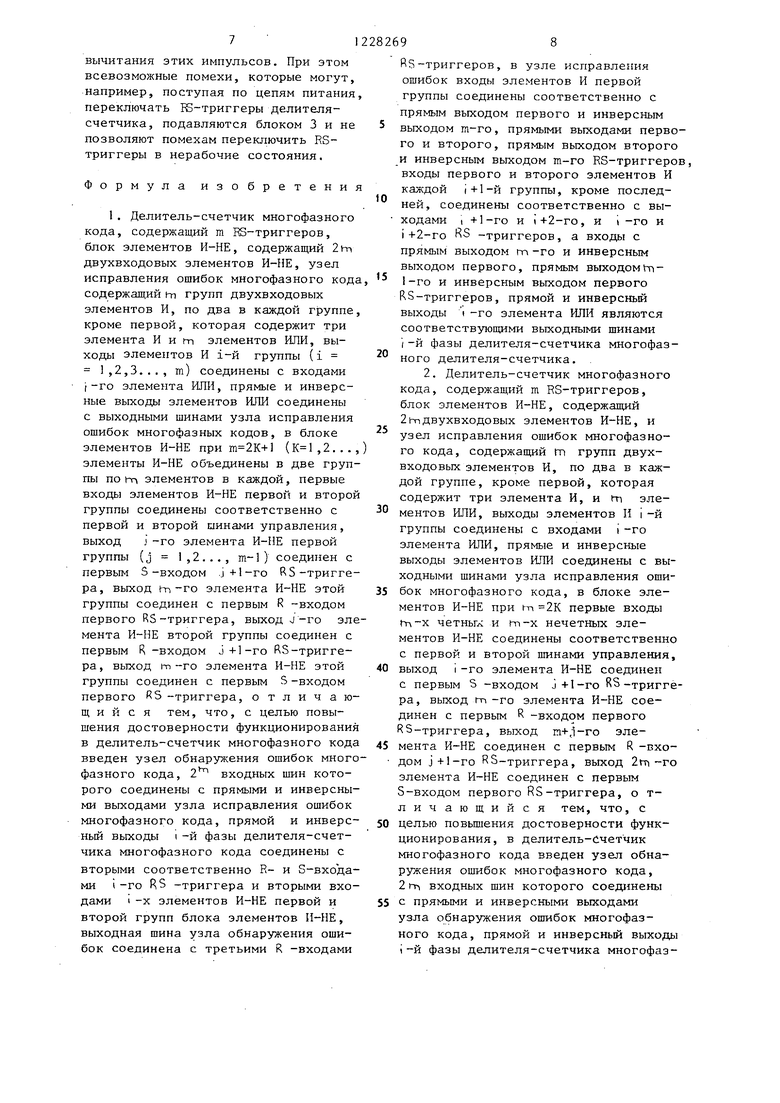

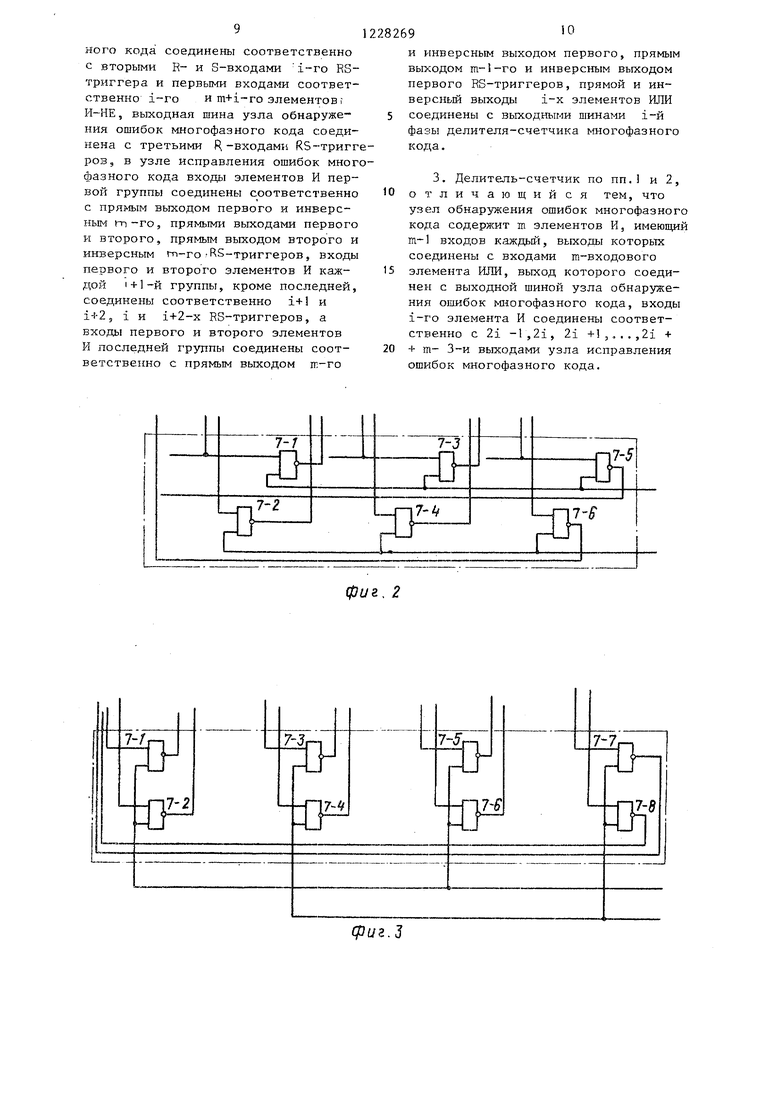

На фиг. 1 показана структурная схема делителя-счетчика многофазного кода; на фиг, 2 - пример выполнения блока элементов И-НЕ при нечетном числе разрядов (); на фиг. 3 - пример выполнения блока элементов И-НЕ при четном числе разрядов (); на фиг. 4 - пример выполнения узла исправления ошибок и узла обнаружения ошибок многофазного кода для случая .

Делитель-счетчик многофазного кода содержит m RS-триггеров, от 1-1 до 1-т, блок 2 элементов И-НЕ, узел 3 исправления опшбок многофазного кода и узел 4 обнаруясения ошибок многофазного кода. Шины управления блока элементов И-НЕ являются тактовыми входами 5 и 6 делителя- счетчика многофазного кода.

В устройстве по первому варианту блок 2 элементов И-НЕ содержит 2т двухвходовых элементов И-НЕ от 7-1 до 7-2т 5 и узел 3 исправления ошибок -1Ногофазного кода, содержащий m групп двухвходовых элементов И (8-1)-{8-2т +1), по два в каждой группе, кроме первой, которая содержит три элемента И и m элементов 11Л (9-l)-(9m), выходы элементов И i-й. группы (,2,3..., т) соединены с входами i-ro элемента ИЛИ, пр1ямые и инверсные выходы элементов ИЛИ соединены с выходными шинами узла исправления ошибок многофазног кода, в блоке элементов И-НЕ при (,2,,..) элементы И-НЕ объединены в две группы по элементов в каждой, первые входы элементов И-НЕ первой и второй группы соединены с первой и второй шинами управления соответственно, выход ,1-го элемента И-НЕ первой группы

5

0

5

(,1 1,2,..., т-1 ) соединен с первым Б-входом j +1-ГО RS-триггера, выход т-го элемента И-НЕ этой группы соединен с первым R -входом первого RS -триггера 1-1, выход j-го элемента И-НЕ второй группы соединен с первым R-входом ,1+1-го RS- триггера l-j + l, выход т-го элемен-- та И-НЕ этой группы соединен с первым S-входом первого PS-триггера 1-1. В узле 4 обнаружения ошибок многофазного кода 2 входных шин соединены с прямыми и инверсными выходами узла 3 исправления ошибок многофазного кода, прямой и инверсный выходы i-1 фазы делителя-счетчика многофазного кода соединены с вторыми соответственно R- и S-входа- ми i-ro RS-триггера 1-i и вторыми входами i-x элементов И-НЕ первой и второй групп блока 2 элементов И- НЕ, выходная шина узла 4 обнаружения ошибок соединена с третьими R- входами RS-триггера 1-i, в узле 3 исправления ошибок входы элементов И первой группы соединены соответственно с прямым выходом первого и инверсным выходом т-го, прямыми выходами первого 1-1 и второго 1-2, пря1-1ым выходом второго 1 -2 и инверсным выходом га-го RS-триггеров, 1-т, входы первого и второго элементов И каждой i+1-й группы, кроме последней, соединены соответственно с выходами i+1-го и i+2-го, и i-ro 1-i и i+2-го l-i+2 RS-триггеров, а входы первого и второго элементов И последней группы соединены с прямым выходом т-го 1-т и инверсным выходом первого 1-1, прямым выходом т- 1-го i-m-1 и инверсным выходом первого 1-1 RS-триггеров, прямой и инверсный выходы i-ro элемента ИЛИ 9-i являются соответствуюшими вы- ходн:ыми шинами 10-i i-й фазы делителя-счетчика многофазного делителя- счетчика.

В делителе-счетчике по второму варианту блок 2 элементов И-НЕ содер0 жит 2т двухвходовых элементов И-НЕ от 7-1 до 7-ш, узел 3 исправления ошибок ьшогофазного кода, содержащий т-групп двухвходовых элементов И (8-1)-(8-2т+1), по два в каждой

5 группе, кроме первой, которая содержит три элемента И (8-1)-(8-3), и m элементов ИЛИ (9-1 )-(9-in), выходы элементов И i-й группы соединены с

0

5

0

5

входами i-го элемента Ш1И 9-i, прямые и инверсные выходы элементов ИЛИ (9-1)-(9-т) соединены с выходными шинами узла исправления ошибок многофазного кода, в блоке 2 элементов И- НЕ при т-2К первые входы т-х четных и т-х нечетных элементов И-НЕ соединены с первой и второй шинами управления соответственно, выход i-ro элемента И-НЕ соединен с первым S-входом iJ + 1-го RS-.триггера 1-J + 1, выход т-го элемента И-НЕ соединен с первым R -входом первого RS-триг- гера 1-1, выход m+j-ro элемента И- НЕ соединен с первым Н-входом j+1-го RS-триггера 1-j + l , выход 2т-го элемента И-НЕ соединен с первым S-входом первого RS-триггера 1-1. В узле 4 обнаружения ошибок многофазного кода 2т входных шин соединены с прямым и инверсными выходами узла 3 обнаружния ошибок многофазного кода, пря- . мой и инверсный выходы -и фазы делителя-счетчика многофазного кода соединены соответственно с вторыми R- и 8-входами i-ro RS-триггера 1-i и первыми входами i-ro 7-i и m+i-ro 7-m+i элементов И-НЕ со-- ответственно, выходная шина узла 4 обнаружения ошибок многофазного кода соединена с третьими R-входа- ми RS-триггеров 1-(, в узле 3 исправления ошибок многофазного кода входы элементов И 8-1, 8-2 и 8-3 первой группы соединены с прямым выходом первого 1-1 и инверсным выходом 1-п -го 1 -т, прямыми выходами пер- Bofo 1-1 и второго 1-2, прямым выходом второго 1-2 и инверсным выходом т-го 1-т РБ-триггеров соответственно, входы первого и второго элементов И каждой ( группы, кроме последней, соединены i+1 и i+2, i и i+2-x RS-триггеров соответственно, а входы первого и второго элементов И последней группы соединены соответственно с прямым выходом hn-ro и инверсным вькодом первого 1-1, прямым выходом т-1-го 1-m-l и инверсным выходом первого I-т RS-триггеров, прямой и инверсный выходы i-x элементов ИЛИ 9-i- соединены с выходными шинами 10-i, i-й фазы делителя-счетчика много-фазного кода.

Узел 4 обнаружения ошибок многофазного кода содержит -п элементов

28: .69

И от 11-1 до П-п., имеющий -,-1 входов каждый, выходы KOTopt.ix сое- - динены с входами ьл -входового элемента ИЛИ 12, выход которого сое5 динен с выходной шиной узла обнаружения ошибок многофазного кода.

Предлагаемый делитель-счетчик многофазного кода работает следующим образом.

to Перед рассмотрением работы всего устройства остановимся первоначально на работе блоков исправления и обнаружения ошибок, которая основана на распознавании непрерывности

15 множеств сигналов О и 1 многофазного кода. Рассматривая замкнутый ряд сигналов многофазного кода

t

-Зп.-Ип

й...а.,а

J

нетрудно увидеть, что здесь содержится только два непрерьгоных и неизменных по длине множества сигналов: множество сигналов О и мно-жество сигналов 1. Например, пятифаз- ный код для цифры обычного кода О представляется этими множествами в следующем виде: О О О О 1 1

а для цифры 1 - в виде

1 О О О О О 1 1 1 1у и т.д.. При записи многофазного кода ограничиваются только первыьш гп сигналами из этого ряда (таблица).

35

Аргументы

40

45

Методика обнаружения и исправления ошибок многофазного кода в блоке 3 основана на распознавании непрерывности этих двух множеств: появление в множестве однотипных сигналов

инверсного к ним сигнала, когда он отстоит от края множества на два сигнала и более воспринимается как стопроцентная ошибка. Например, при

эквивалентной цифре 1 появление

должно восприниматься, И О О l О О 1 1 б К .

сигнала а как ошибка

В таблице поясняется работа по исправлению, например, одиночных ошибок многофазного кода, и показан значение исправленного сигнала фазы d в зависимости от сигналов соседних фазс1| 9 U1 которые являются аргументами логической функции

В соответствии с методикой при нулевых сигналах фаз RS -триггеров aj 0, а, 0 независимо от значения сигнала фазы на выходной игане cj. сигнал на выходе делителя счетчика для этой фазы должен быть нулевым (а О, первая строка таблцы) . Ан.алогично при наличии сигнало фаз а|, 1, а. , 1 независимо от значения сигнала а сигнал на вьLкoдe делителя-счетчика должен быт равен единице, а, 1 (поспедняя строка таблицы). Если обозначить мнжество значений сигналов Л когда сигнала долзкен передаваться без изменения через М , то в соответствии с правилами логики получим

1

значение исправленного сигнала , а Вместо множества

,d.

f-,,4i

М, можно использовать мнолсество

Mj()5 которое содержит все сочетания сигналов 2.

;-,

кром

значения первой строки таблицы, М

S.

(

- а

тогда

Va

а, . V а . а.

- 1 1 I

1 -1 I -t 1

что соответствует логической структурной схеме блока 3.

Рассмотрение работ всего устройства начнем с момента подачи питающего напряжения, когда на входы 5 и 6 не поступают тактовые импульсы. При этом возможны четыре случая устновки RS тpиггepoв делителя-счетчика,

RS -триггеры устанавливаются в одно из состояний, которые полностью соответствуют одиночным циф- рам обычного кода. В этом случае блок 3 пропускает сигналы фаз а - л без каких-либо изменений на I

ходные шины фаз 3., -3,. При этом на выходе блока 4 выдается сигнал ,

RS-триггеры устанавливаются )з одно из ( 2нл) состояний, когда в коде фаз Д т имеются одиноч1228269б

ные ошибки при расстоянии между ними в два сигнала и более, например

11101101100

А. &s

. а а

g Ti 1Ъ

Тогда блок 3 в соответствии с рассмотренной методикой исправит все одиночные ошибки 1 , а-,. - 1 , С.1 ,,/- О, ci 1S- О и сигналы на выходных шинах фаз а , - im будут соответствовать многофазному коду. Эти сигнапы установят все RS-триггеры, воздействуя на их вторые входы, в устойчивые состояния многрфазного кода. Все это время на выходе блока 4 будет существовать сигнал Д .

RS-триггеры устанавливаются в , ,

состоянии, когда

одно из ( 2 - 2 П-;) в коде фаз d -Д имеются одиноч- ные ошибки при расстоянии между ними в один сигнал, например для предельного случая

S0101010I010I010

S ..

а, d,a.a, а..

а, а, а„ а„ а..а,.,,.,д,5а,

в блоке 3 совершаются состязания : сигналы d и а-,, стремятся

0

5

0

5

0

установить d, , а сигналы

а, иа и т.д.. Развитие процесса зависит при этом от соотношения времен переключения RS-триггеров. Поскольку в это время сигналы фаз л - соответствуют многофазному коду, то на выходе блока 4 будет сигнал , который устанавливает

триггеры в исходное, напри5

в с е R S мер нулевое состояние многофазного

кода.

RS-триггеры устанавливаются в одно из (2 - 21-л) состояний, когда в коде фаз a,-d, имеются пачки ошибок, например

1 1 1 1001 100000000.

Блок 3 не может исправлять этот тип ошибок и поэтому на выходных шинах с(-сЗ будет эта же комбинация сигналов фаз, а на выходе блока 4 будет сигнал , который установит все RS-триггеры в исходное состояние.

В любом случае при подаче питания все RS -триггеры устанавливаются в но- ложения М1 огофазного кода. При по-- очередном поступлении на входные ши ны 25 импульсов сх и RS-°TpHrrepbi соверпают переключения в установленном порядке для суммирования либо

вычитания этих импульсов. При этом всевозможные помехи, которые могут, например, поступая по цепям питания, переключать Ю-триггеры делителя- счетчика, подавляются блоком 3 и не позволяют помехам переключить RS- триггеры в нерабочие состояния.

Формула изобретения

1. Делитель-счетчик многофазного кода, содержащий га RS-триггеров, блок элементов И-НЕ, содержащий 2t-n двухвходовых элементов И-НЕ, узел

10

RS-триггеров, в узле исправления ошибок входы элементов И первой группы соединены соответственно прямым выходом первого и инверсны выходом т-го, прямыми выходами пе го и второго, прямым выходом втор и инверсным выходом т-го RS-тригг входы первого и второго элементо каждой 1+1-и группы, кроме посл ней, соединены соответственно с ходами 1 +1-ГО и i+2-го, и i -го i+2-ГО RS -триггеров, а входы с прямым выходом m-го и инверсным выходом первого, прямым выходомVn

исправления ошибок многофазного кода, . инверсным выходом первого

содержащий hi групп двухвходовых элементов И, по два в каждой группе, кроме первой, которая содержит три элемента И и i-n элементов ИЛИ, выходы элементов И i-й группы {i 1,2,3..., m) соединены с входами i-го элемента ИЛИ, прямые и инверсные выходы элементов ИЛИ соединены с выходными шинами узла исправления ошибок многофазных кодов, в блоке элементов И-НЕ при (,2...,) элементы И-НЕ объединены в две группы по hr элементов в каждой, первые входы элементов И-НЕ первой и второй группы соединены соответственно с первой и второй шинами управления, выход J-го элемента И-НЕ первой группы (j 1,2..., m-1 ) соединен с первым S-входом .j+1-го RS-триггера, выход t-n-го элемента И-НЕ этой группы соединен с первым R -входом первого RS-триггера, выход J-го элемента И-НЕ второй группы соединен с первым R -входом J +1-го RS-тригге- ра, выход т-го элемента И-НЕ этой группы соединен с первым S-входом первого RS -триггера, о т л и ч а ю- щ и и с я тем, что, с целью повышения достоверности функционирования

20

25

RS-триггеров, прямой и инверсньй выходы ( -го элемента ИЛИ являются соответствующими выходными шинами )-и фазы делителя-счетчика многофазного делителя-счетчика.

2. Делитель-счетчик многофазного кода, содержащий m RS-триггеров, блок элементов И-НЕ, содержащий 2hnдвухвходовых элементов И-НЕ, и узел исправления ошибок многофазного кода, содержащий m групп двухвходовых элементов И, по два в каждой группе, кроме первой, которая содержит три элемента И, и tn эле ментов ИЛИ, выходы элементов И i -и группы соединены с входами i-го элемента ИЛИ, прямые и инверсные выходы элементов ИЛИ соединены с выходными шинами узла исправления оши35 бок многофазного кода, в блоке элементов И-НЕ при гп 2К первые входы четных и tn-x нечетных элементов И-НЕ соединены соответственно с первой и второй шинами управления,

40 выход 1-го элемента И-НЕ соединен с первым S -входом J +1-го RS-триггера, выход m -го элемента И-НЕ соединен с первым R -входом первого

RS-триггера, выход n+j-ro эле- в делитель-счетчик многофазного кода 45 мента И-НЕ соединен с первым R -вхо- введен узел обнаружения ошибок много- . дом j+1-го RS-триггера, выход 2ni го

элемента И-НЕ соединен с первым S-входом первого RS-триггера, о т- личающийся тем, что, с

фазного кода, 2 входных шин которого соединены с прямыми и инверсными выходами узла исправления ошибок

многофазного кода, прямой и инверс- 50 целью повьш1ения достоверности функньш выходы I -и фазы делителя-счетчика многофазного кода соединены с вторыми соответственно R- и 8-вход,а- ми i-го RS -триггера и вторыми входами I-X элементов И-НЕ первой и второй групп блока элементов И-НЕ, выходная шина узла обнаружения ошибок соединена с третьими R -входами

RS-триггеров, в узле исправления ошибок входы элементов И первой группы соединены соответственно с прямым выходом первого и инверсным выходом т-го, прямыми выходами первого и второго, прямым выходом второго и инверсным выходом т-го RS-триггеров, входы первого и второго элементов И каждой 1+1-и группы, кроме последней, соединены соответственно с выходами 1 +1-ГО и i+2-го, и i -го и i+2-ГО RS -триггеров, а входы с прямым выходом m-го и инверсным выходом первого, прямым выходомVn. инверсным выходом первого

RS-триггеров, прямой и инверсньй выходы ( -го элемента ИЛИ являются соответствующими выходными шинами )-и фазы делителя-счетчика многофазного делителя-счетчика.

2. Делитель-счетчик многофазного кода, содержащий m RS-триггеров, блок элементов И-НЕ, содержащий 2hnдвухвходовых элементов И-НЕ, и узел исправления ошибок многофазного кода, содержащий m групп двухвходовых элементов И, по два в каждой группе, кроме первой, которая содержит три элемента И, и tn элементов ИЛИ, выходы элементов И i -и группы соединены с входами i-го элемента ИЛИ, прямые и инверсные выходы элементов ИЛИ соединены с выходными шинами узла исправления ошибок многофазного кода, в блоке элементов И-НЕ при гп 2К первые входы четных и tn-x нечетных элементов И-НЕ соединены соответственно с первой и второй шинами управления,

выход 1-го элемента И-НЕ соединен с первым S -входом J +1-го RS-триггера, выход m -го элемента И-НЕ соединен с первым R -входом первого

ционирования, в делитель-Счетчик многофазного кода введен узел обнаружения ошибок многофазного кода, 2 гг, входных шин которого соединены 55 с прямыми и инверсными выходами узла обнаружения ошибок многофазного кода, прямой и инверсный выходы i-и фазы делителя-счетчика многофазного кода соединены соответственно с вторыми R- и 3 входами i-ro RS- триггера и первыми входаьш соответственно i-ro и m+i-ro элементов 1 И-НЕ, выходная шина узла обнаруже- ния ошибок многофазного кода соединена с третьими R-входами RS-триггров, в узле исправления ошибок многфазного кода входы элементов И первой группы соединены соответственно с прямым выходом первого и инверсным т-го, прямыми выходами первого и второго, прямым выходом второго и инверсным гл-го RS-триггеров, входы первого и второго элементов И каж- дои 1+1-и группы, кроме последней, соединены соответственно i+ и 1+25 i и i+2-x RS-триггеров, а входы первого и второго элементов И последней группы соединены соот- ветственно с прямым выходом ге-го

и инверсным выходом первого, прямым выходом т-1-го и инверсным выходом первого RS-триггеров, прямой и инверсный выходы i-x элементов ИЛИ соединены с выходными шинами i-й фазы делителя-счетчика многофазного кода.

3. Делитель-счетчик по пп. и 2, отличающийся тем, что узел обнаружения ошибок многофазног кода содержит m элементов И, имеющи т-1 входов каждый, выходы которых соединены с входами т-входового эл€;мента ИЛИ, выход которого соединен с выходной шиной узла обнаружения ошибок многофазного кода, входы 1-го элемента И соединены соответственно с 21 -1,21, 21 +1,...,21 + + т- 3-й выходами узла исправления ошибок многофазного кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1385294A1 |

| Устройство для управления многофазным инвертором | 1978 |

|

SU955837A1 |

| Реверсивное счетное устройство | 1985 |

|

SU1398091A1 |

| Устройство для деления | 1984 |

|

SU1252772A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1129636A1 |

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде с постоянным весом К | 1982 |

|

SU1149260A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для сравнения кодов | 1982 |

|

SU1080134A1 |

| Вентильный двигатель | 1980 |

|

SU944472A2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКОГО КОДА ХЕММИНГА | 2004 |

|

RU2270521C1 |

Изобретение относится к цифровой и преобразовательной технике и может быть использовано в электроприводах постоянного и переменного тока с цифровым управлением. Цель изобретения - повышение достоверности функционирования. Устройство содержит m RS-триггеров, от 1-1 до 1-т, блок 2 элементов И-НЕ, узел 3 исправления ошибок и узел 4 обнаружения ошибок многофазного кода, тактовые входы 5 и 6. В описании приведены структурные схемы и описаны два варианта выполнения, блок 2 элементов И-НЕ, при четном числе разрядов (т 4) и при нечетном числе разрядов (т 3). Приведен пример вьтолнения узла 3 исправления и узла 4 обнаружения ошибок многофазного кода для случая m 5. 2.с и 1 з.п. ф-лы, 4 ил., 1 табл. йя ffm i (Л N IsD 00 N О CO

фиг, 2

фиг.З

Редактор Т. Митейко

Заказ 2297/58Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фиг.

Составитель 0. Скворцов

Техред И.Верес Корректор Т.Колб

| Пятлин А.А., Овсищер П.И., Лазер И.М | |||

| и др | |||

| Проектирование микроэлектронных устройств | |||

| М.: Советское радио, 1977, 272 с | |||

| Устройство для генерирования импульсов управления ионными преобразователями тока | 1958 |

|

SU139715A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Decade counter | |||

| Устройство для штамповки жидкостью зубных коронок | 1980 |

|

SU1041104A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Hilberg W | |||

| Die Eccles | |||

| Jordan- Schaltung mit Transistoren Fur sehr | |||

| Пробочный кран | 1925 |

|

SU1960A1 |

| Breic I | |||

| Ideally fact decimal counters with bistables | |||

| - IEEE, Transactions on Electronic computers, 1965, V | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Jonson Counters even-and add cycle length | |||

| - Electronic Engineer, 1971 | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| g s, , Авторское свидетельство СССР tP 834935, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-30—Публикация

1982-12-29—Подача