Изобретение относится к автомати- ,ке и вычислительной технике и может быть использовано, например, для регистрации информации в автоматизированных системах обработки информации

Целью изобретения является увеличение быстродействия устройства.

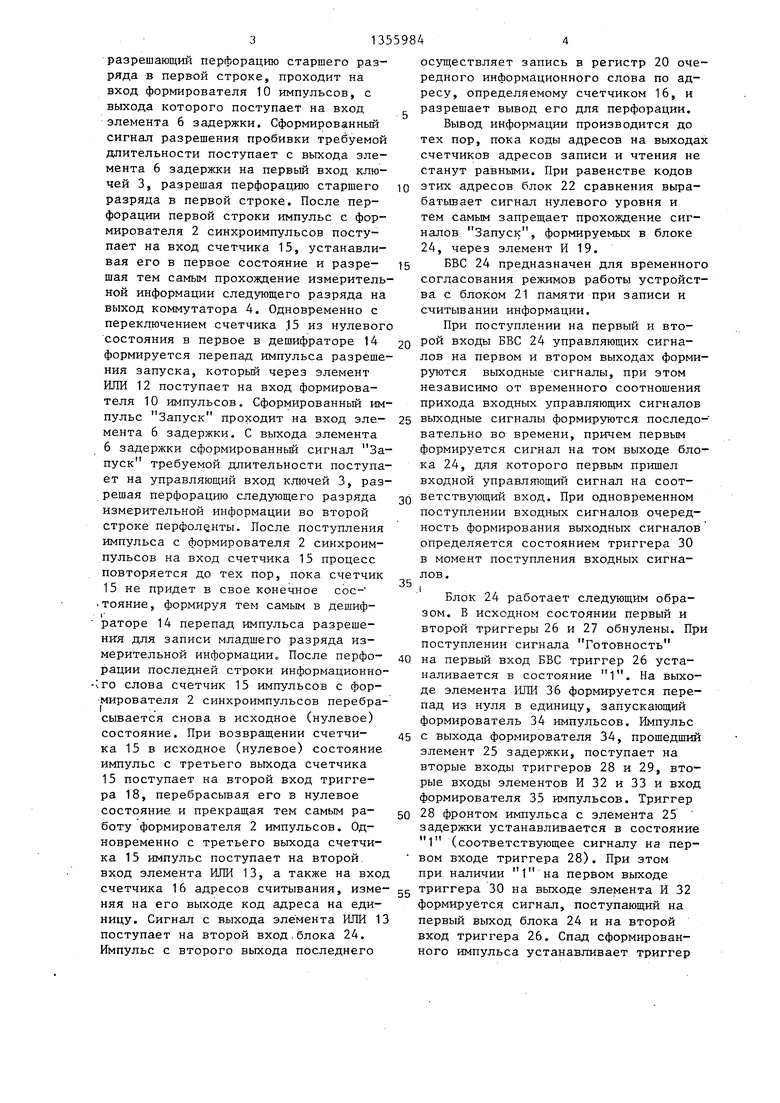

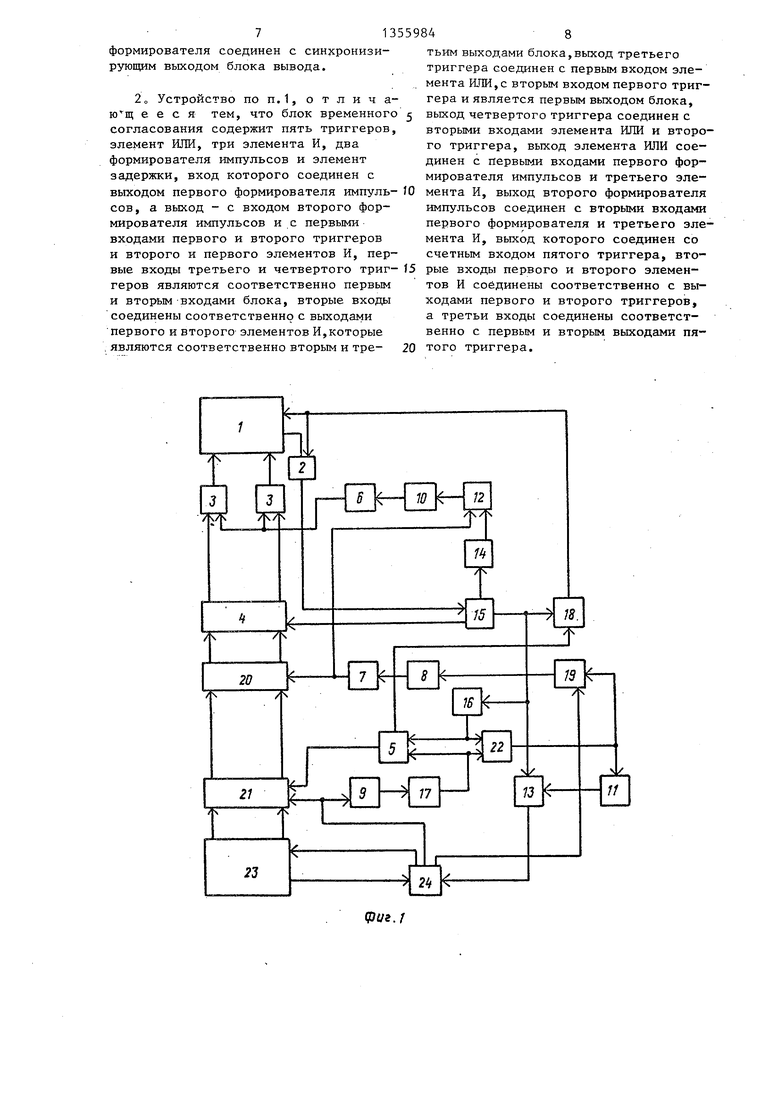

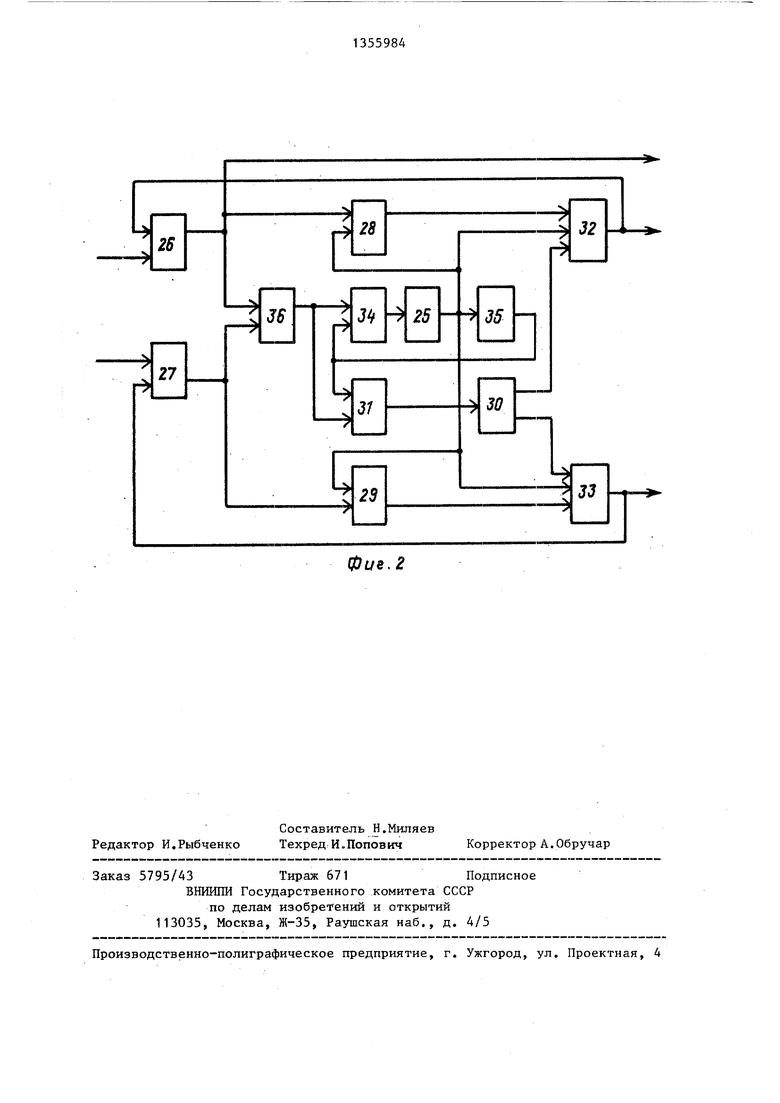

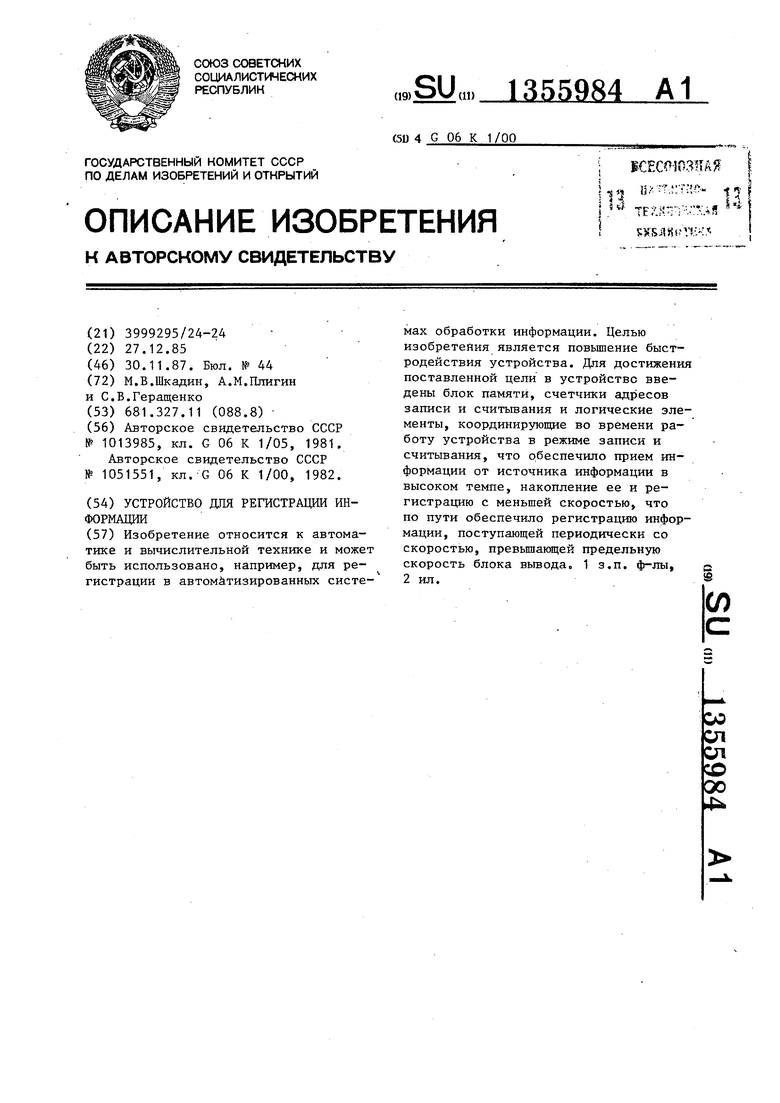

На фиг,1 представлена функциональная схема устройства; на фиг,2 - функциональная схема блока временного согласования.

Устройство содержит блок 1 вывода информации, второй формирователь 2 импульсов, ключи 3, первый коммутатор 4, второй коммутатор.5, первый, второй, третий и четвертый элементы 6-9 задержки, первьй и третий формирователи 10 и 11 имщтьсов, первый и второй элементы ИЛИ 12 и 13, дешифратор 14, счетчики 15, 16 и 17 циклов регистрации, адресов считывания и записи, первый триггер 18, первый элемент И 19, регистр 20, блок 21 памяти, блок 22 сравнения, источник 23 информации, блок 24 временного согла- сования (ВВС), состоящий из элемента 25 задержки, триггеров 26-30, элементов И 31, 32, 33, формирователей 34 и 35 импульсов и элемента ИЛИ 36„

Устройство работает следующим образом,

В начале цикла регистрации счетчики 15, 16 и 17, а также триггер 18 установлены в нулевое состояние От источника информации в параллельном коде подается информация на информационные входы блока 21 памяти. На первый вход ВВС 24 от источника 23 информации поступает импульс готовности, С первого выхода блока 24 сформированный импульс Запись поступает на блок 21 памяти и осуществляет запись поступающего от источника информационного слова по нулевому адресу. Одновременно сигнал Запись через элемент 9 задержки поступает на вход счетчика 17 адресов записи и увеличивает на его выходах значение кода адреса на единицу, С выхода счетчика 17 код адреса поступает через коммутатор 5 на адресные входы блока 21 памяти, подготавливая его для записи поступающего от источника

35

записи и счетчика 16 адресов считывания коды адресов записи и считывания подаются на блок 22 сравнения, на выходе которого формируется сигнал с уровнем О в том случае если коды поступающих на его входы адресов равны. Так как код на выходе счетчиков адресов записи увеличился, на выходе блока 22 сравнения сформирован сигнал с уровнем который одновременно поступает на первьш вход эле-, мента 19 и на вход формирователя 11, .Формирователь 11 по перепаду из нуля в единицу формирует положительный импульс, который через элемент 13 поступает на второй вход блока 24, С второго выхода блока 24 импульс Запуск поступает на второй вход элемента И 19, на первом входе которого присутствует сигнал с уровнем 1, поступающий с выхода блока 22 сравнения. Сигнал Запуск в дальнейшем используется для управления чтением информации из блока 21 памяти и выводом ее на перфорационную ленту, С выхода элемента 19 сигнал поступает на вход элемента 8 задержки, а с его выхода - на управляющий вход коммутатора 5,, который коммутирует код адреса, поступающий на его второй вход со счетчика 16,, на блок 20 памяти, В соответствии с KOMr-iyTHpyeMbM кодом адреса производится считывание информации; записанной в блок 21 памяти. С выхода элемента 8 задержки сигнал

Запуск поступает одновременно на вход элемента 9 задержки и на первый вход триггера 13, С выхода элемента 7 задержки задерж.анный сигнал поступа40 ет на регистр 20 и служит для записи в него информационного слова из блока 21 памяти по предварительно уста новленному коду адреса Сигнал, поступающий на триггер 18 с элемента 8

45 задержки, перебрасывает его в сос- .тояние, разрешающее запуск формирователя 2 синхроимпульсов до окончания перфорации измерительной информации построчно, начиная со старших разря50 дов и кончая младшими на перфоленте.

В начале .цикла вывода информации счетчик 15 находится в нулевом состоянии, разрешая прохождение старшего информации очередного информационного разряда измерительной информации на вы- слова. На втором выходе блока 24 фор- ход коммутатора 4, С выхода элемен- мируется сигнал готовности устройства та 7 задержки задержанный сигнал За- к приему очередного информационного пуск поступает на первый вход эле- слова. С выходов счетчика 17 адресов мента ИЛИ 12, Далее сигнал Запуск,

5

О

5 0

0

5

записи и счетчика 16 адресов считывания коды адресов записи и считывания подаются на блок 22 сравнения, на выходе которого формируется сигнал с уровнем О в том случае если коды поступающих на его входы адресов равны. Так как код на выходе счетчиков адресов записи увеличился, на выходе блока 22 сравнения сформирован сигнал с уровнем который одновременно поступает на первьш вход эле-, мента 19 и на вход формирователя 11, .Формирователь 11 по перепаду из нуля в единицу формирует положительный импульс, который через элемент 13 поступает на второй вход блока 24, С второго выхода блока 24 импульс Запуск поступает на второй вход элемента И 19, на первом входе которого присутствует сигнал с уровнем 1, поступающий с выхода блока 22 сравнения. Сигнал Запуск в дальнейшем используется для управления чтением информации из блока 21 памяти и выводом ее на перфорационную ленту, С выхода элемента 19 сигнал поступает на вход элемента 8 задержки, а с его выхода - на управляющий вход коммутатора 5,, который коммутирует код адреса, поступающий на его второй вход со счетчика 16,, на блок 20 памяти, В соответствии с KOMr-iyTHpyeMbM кодом адреса производится считывание информации; записанной в блок 21 памяти. С выхода элемента 8 задержки сигнал

Запуск поступает одновременно на вход элемента 9 задержки и на первый вход триггера 13, С выхода элемента 7 задержки задерж.анный сигнал поступа0 ет на регистр 20 и служит для записи в него информационного слова из блока 21 памяти по предварительно уста новленному коду адреса Сигнал, поступающий на триггер 18 с элемента 8

5 задержки, перебрасывает его в сос- .тояние, разрешающее запуск формирователя 2 синхроимпульсов до окончания перфорации измерительной информации построчно, начиная со старших разря0 дов и кончая младшими на перфоленте.

разрешающий перфорацию старшего разряда в первой строке, проходит на вход формирователя 10 импульсов, с выхода которого поступает на вход элемента 6 задержки. Сформированный сигнал разрешения пробивки требуемой длительности поступает с выхода элемента 6 задержки на первый вход ключей 3, разрешая перфорацию старшего разряда в первой строке. После перфорации первой строки импульс с формирователя 2 синхроимпульсов поступает на вход счетчика 15, устанавливая его в первое состояние и разрешая тем самым прохождение измерительной информации следующего разряда на выход коммутатора 4, Одновременно с

При поступлении на первый и втопереключением счетчика ,15 из нулевого состояния в первое в дешифраторе 14 20 Р° входы ВВС 24 управляющих сигна- формируется перепад импульса разреше- лов на первом и втором выходах форми- ния запуска, который через элемент PfflH 12 поступает на вход формирователя 10 импульсов. Сформированный импульс Запуск проходит на вход элемента 6 задержки. С выхода элемента 6 задержки сформированный сигнал Запуск требуемой длительности поступает на управляющий вход ключей 3, раз30

решая перфорацию следующего разряда измерительной информации во второй строке перфоленты. После поступления импульса с формирователя 2 синхроимпульсов на вход счетчика 15 процесс повторяется до тех пор, пока счетчик 15 не придет в свое конечное сое- Тояние, формируя тем самым в дешиф раторе 14 перепад импульса разрешения для записи младшего разряда измерительной информациио После перфорации последней строки информационно;го слова счетчик 15 импульсов с фор- мирователя 2 синхроимпульсов перебрасывается снова в исходное (нулевое) состояние. При возвращении счетчика 15 в исходное (нулевое) состояние импульс с третьего выхода счетчика 15 поступает на второй вход триггера 18, перебрасывая его в нулевое состояние и прекращая тем самым работу формирователя 2 импульсов. Одновременно с третьего выхода счетчика 15 импульс поступает на второй вход элемента ИЛИ 13, а также на вход счетчика 16 адресов считывания, изменяя на его выходе код адреса на единицу. Сигнал с выхода элемента ИЛИ 13 поступает на второй вход,блока 24. Импульс с второго выхода последнего

руются выходные сигналы, при этом независимо от временного соотношения прихода входных управляющих сигналов 25 выходные сигналы формируются последо- вательно во времени, причем первым формируется сигнал на том выходе блока 24, для которого первым пришел входной управляющий сигнал на соответствующий вход. При одновременном поступлении входных сигналов очередность формирования выходных сигналов определяется состоянием триггера 30 в момент поступления входных сигналов. I

35

40

Блок 24 работает следующим образом. В исходном состоянии первый и второй триггеры 26 и 27 обнулены. При поступлении сигнала Готовность на первый вход ББС триггер 26 уста- наливается в состояние 1. На выходе элемента 1ШИ 36 формируется перепад из нуля в единицу, запускающий формирователь 34 импульсов. Импульс 45 с выхода формирователя 34, прошедший элемент 25 задержки, поступает на вторые входы триггеров 28 и 29, вторые входы элементов И 32 и 33 и вход формирователя 35 импульсов. Триггер 28 фронтом импульса с элемента 25 задержки устанавливается в состояние 1 (соответствующее сигналу на первом входе триггера 28). При этом при наличии 1 на первом выходе триггера 30 на выходе элемента И 32 формируется сигнал, поступающий на первый выход блока 24 и на второй вход триггера 26. Спад сформированного импульса устанавливает триггер

50

55

9844

осуществляет запись в регистр 20 очередного информационного слова по адресу, определяемому счетчиком 16, и разрешает вывод его для перфорации.

Вывод информации производится до тех пор, пока коды адресов на выходах счетчиков адресов записи и чтения не станут равными. При равенстве кодов этих адресов блок 22 сравнения выра- батьшает сигнал нулевого уровня и тем самым запрещает прохождение сигналов Запуск, формируемых в блоке 24, через элемент И 19.

ВВС 24 предназначен для временного согласования режимов работы устройства с блоком 21 памяти при записи и считывании информации.

При поступлении на первый и вто5

10

15

20 Р° входы ВВС 24 управляющих сигна- лов на первом и втором выходах форми- 0 Р° входы ВВС 24 управляющих сигна- лов на первом и втором выходах форми-

0

руются выходные сигналы, при этом независимо от временного соотношения прихода входных управляющих сигналов 5 выходные сигналы формируются последо- вательно во времени, причем первым формируется сигнал на том выходе блока 24, для которого первым пришел входной управляющий сигнал на соответствующий вход. При одновременном поступлении входных сигналов очередность формирования выходных сигналов определяется состоянием триггера 30 в момент поступления входных сигналов. I

5

0

Блок 24 работает следующим образом. В исходном состоянии первый и второй триггеры 26 и 27 обнулены. При поступлении сигнала Готовность на первый вход ББС триггер 26 уста- наливается в состояние 1. На выходе элемента 1ШИ 36 формируется перепад из нуля в единицу, запускающий формирователь 34 импульсов. Импульс 5 с выхода формирователя 34, прошедший элемент 25 задержки, поступает на вторые входы триггеров 28 и 29, вторые входы элементов И 32 и 33 и вход формирователя 35 импульсов. Триггер 28 фронтом импульса с элемента 25 задержки устанавливается в состояние 1 (соответствующее сигналу на первом входе триггера 28). При этом при наличии 1 на первом выходе триггера 30 на выходе элемента И 32 формируется сигнал, поступающий на первый выход блока 24 и на второй вход триггера 26. Спад сформированного импульса устанавливает триггер

0

5

51

26 в состояние О. При наличии О на первом выходе триггера 30 и поступлении импульса готовности на первый вход триггера 26 формирователи 34 и 35 запускаются дважды, при этом первый импульс с выхода формирователя 35 проходит через элемент И 31 и устанавливает триггер 30 в состояние 1, а второй импульс с формировате ля 34 проходит элемент 25 задержки и элемент И 32 и поступает на первый выход блока 24; второй и мпульс с формирователя 35 не проходит на вход триггера 30, так как к этому времени триггер 26 установлен в состояние О и на выходе элемента Р1 31 - 0 Последующие импульсы готовности, поступающие на вход триггера 26, приводят к формированию сигнала на первом выходе ВВС при первом запуске формирователя 34 при условии отсутствия управляющего сигнала на втором входе ВВС, Формирование сигнала на втором выходе ВВС 24 при поступлении сигнала на второй вход происходит аналогично рассмотренному выше.

ВВС 24 позволяет осуществить асинхронное независимое обращение к блок памяти- при чтении и записи информации.

Та.ким образом, введение в устройство элементов управления режимами записи и чтения блока памяти и блока временного согласования позволяет регистрировать на перфоленте информацию, поступающую с неравномерным темпом от источника информации, и, таки образом, существенно повысить скорость регистрации информации от источника, сохраняя скорость работы блока вывода.

Формула изобретения

йены с соответств лощими информационными входами регис;тра5 а адресные входы с соответствующими выходами второго коммутатора, выходы регистра соединены с соответствующими входами первого ко гмутатора.э выход третьего элемента задержки соединен с управляющим входом регистра и с вторым входом первого элемента ИЛИ, выход элемента И соединен через четвертый элемент задержки с: входом третьего элемента задержки,, с управляющим входом второго кo мyтaтopa и с установочным входом триггера, выход переполнения счетчика циклов регистрации

1. Устройство для регистрации информации, содержащее блок вывода информации, информационные входы которого соединены с выходами ключей, последовательно соединенные первый элемент И.ТШ, первый формирователь тл- Q coepy iieii с.-ву оцои-вто- ого счетчика счк- пульсов и первый элемент задержки, тывания и с первым Е;ХОДОМ второго эле- выход которого соединен с управляющими входами ключей, первый коммутатор, выходы которого соединены с ин

мента ИЛИ, блока сравнения соединен с входом третьего формирователя импульсов и с вторым входом элемента

формационными входами ключей, счетчик 55 код третьего формирователя имциклов регистрации, вход которого соединен с выходом второго формирователя импульсов, информационные ходы соединены с входами дешифратора

и адресными входами первого коммута- тора, а выход переполнения соединен с входом Сброс первого триггера, выход которого соединен с первым входом второго формирователя, выход дешифратора соединен с первым входом первого элемента ИЛИ, отличающееся тем, что, с целью увеличения быстродействия устройства, оно содержит регистр, блок памяти, блок сравнения, второй коммутатор, второй, третий и четвертый элементы задержки, счетчики адресов записи и считывания, второй элемент ИПИ, элемент И, третий

формирователь импульсов и блок временного согласования, первый вход которого является входом Готовность устройства, второй вход блока временного согласования соединен с выходом

второго элемента )4ЛИ, первый выход является выходом устройства, второй выход соединен с входом записи блока памяти и через второй элемент задержки - с входом счетчика адресов записи, а третий выход блока временного согласования соединен с первым входом элемента И, информационные выходы счетчиков ад эесов записи и считывания соединены соответственно с

информационными входами первой и второй групп блока сравнения и второго коммутатора, инфо эмационные входы блока памяти являются информационными входами устройсугва, выходы соедийены с соответств лощими информационными входами регис;тра5 а адресные входы с соответствующими выходами второго коммутатора, выходы регистра соединены с соответствующими входами первого ко гмутатора.э выход третьего элемента задержки соединен с управляющим входом регистра и с вторым входом первого элемента ИЛИ, выход элемента И соединен через четвертый элемент задержки с: входом третьего элемента задержки,, с управляющим входом второго кo мyтaтopa и с установочным входом триггера, выход переполнения счетчика циклов регистрации

coepy iieii с.-ву оцои-вто- ого счетчика счк- тывания и с первым Е;ХОДОМ второго эле-

coepy iieii с.-ву оцои-вто- ого счетчика счк- тывания и с первым Е;ХОДОМ второго эле-

мента ИЛИ, блока сравнения соединен с входом третьего формирователя импульсов и с вторым входом элемента

пульсов соединен с вторым входом второго элемента Из выход триггера соединен с управляющим входом блока вывода информации, второй вход первого

формирователя соединен с синхронизирующим выходом блока вывода.

2 о Устройство по П.1, о т л и ч а- е е с я тем, что блок временного с согласования содержит пять триггеров, элемент ИЛИ, три элемента И, два формирователя импульсов и элемент задержки, вход которого соединен с

8

тьим выходами блока,выход третьего триггера соединен с первым входом элемента ИЛИ,с вторым входом первого триггера и является первым выходом блока, выход четвертого триггера соединен с вторыми входами элемента ИЛИ и второ го триггера, выход элемента ИЛИ соединен с первыми входами первого формирователя импульсов и третьего эле-л. .-.liiijwj. j. A V-tiJ l J JJIC

ВЫХОДОМ первого формирователя импуль-tO мента И, выход второго формирователя

сов, а выход - с входом второго фор мирователя импульсов и с первыми входами первого и второго триггеров

импульсов соединен с вторыми входами первого формирователя и третьего элемента И, выход которого соединен со счетным входом пятого триггера, втои

второго и первого элементов И, перимпульсов соединен с вторыми входам первого формирователя и третьего эл мента И, выход которого соединен со счетным входом пятого триггера, вто

вые входы третьего и четвертого триг- 15 рые входы первого и второго элеменгеров являются соответственно первым и вторым входами блока, вторые входы соединены соответственно с выходами первого и второго элементов И,которые : являются соответственно вторым и тре20

тов и соединены соответственно с вы ходами первого и второго триггеров, а третьи входы соединены соответственно с первым и вторым выходами пятого триггера.

8

тьим выходами блока,выход третьего триггера соединен с первым входом элемента ИЛИ,с вторым входом первого триггера и является первым выходом блока, выход четвертого триггера соединен с вторыми входами элемента ИЛИ и второго триггера, выход элемента ИЛИ соединен с первыми входами первого формирователя импульсов и третьего эле-л. .-.liiijwj. j. A V-tiJ l J JJIC

мента И, выход второго формирователя

импульсов соединен с вторыми входами первого формирователя и третьего элемента И, выход которого соединен со счетным входом пятого триггера, вторые входы первого и второго элеменрые входы первого и второго элемен

тов и соединены соответственно с выходами первого и второго триггеров, а третьи входы соединены соответственно с первым и вторым выходами пятого триггера.

Редактор И.Рыбченко

Составитель Н.Миляев Техред И.Попович

Заказ 5795/43 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фие,2

Корректор А.Обручар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в блоках интегральной оперативной памяти | 1988 |

|

SU1605281A1 |

| Цифровой фильтр | 1990 |

|

SU1730718A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1238093A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1989 |

|

SU1679535A1 |

| Ретранслятор сообщений | 1990 |

|

SU1734227A1 |

| Устройство для автоматического измерения гидрологических параметров | 1985 |

|

SU1325301A1 |

| Устройство для ввода информации | 1989 |

|

SU1649529A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано, например, для регистрации в автоматизированных системах обработки информации. Целью изобретения является повьшение быстродействия устройства. Для достижения поставленной цели в устройство введены блок памяти, счетчики адресов записи и считьшания и логические элементы, координирующие во времени работу устройства в режиме записи и считывания, что обеспечило прием информации от источника информации в высоком темпе, накопление ее и регистрацию с меньшей скоростью, что по пути обеспечило регистрацию информации, поступающей периодически со скоростью, превьшающей предельную скорость блока вьгоода. 1 з.п. ф-лы, 2 ил. Ш (Л о: ел СП СО ОС

| Устройство для регистрации информации | 1981 |

|

SU1013985A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для регистрации информации | 1982 |

|

SU1051551A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-30—Публикация

1985-12-27—Подача