«

Изобретение относится к вычислительной технике и может быть использовано в цифровых устройствах с аппаратным исправлением ошибок.

Целью изобретения является повышение надежности функционирования.

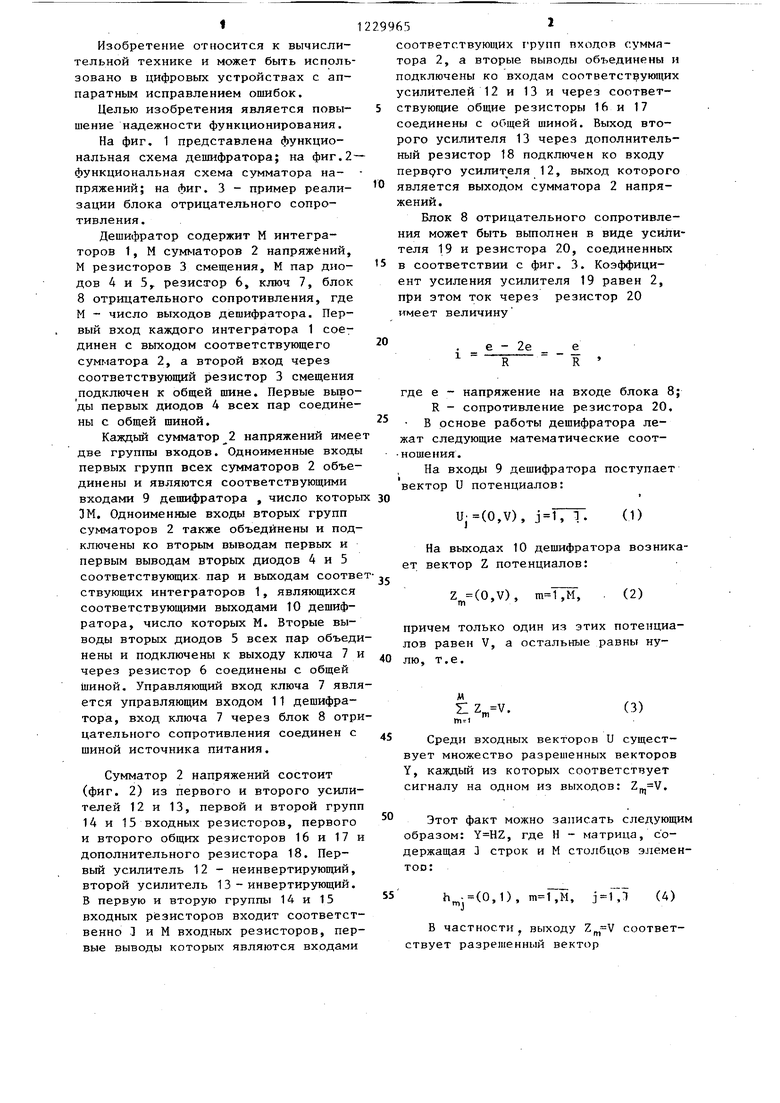

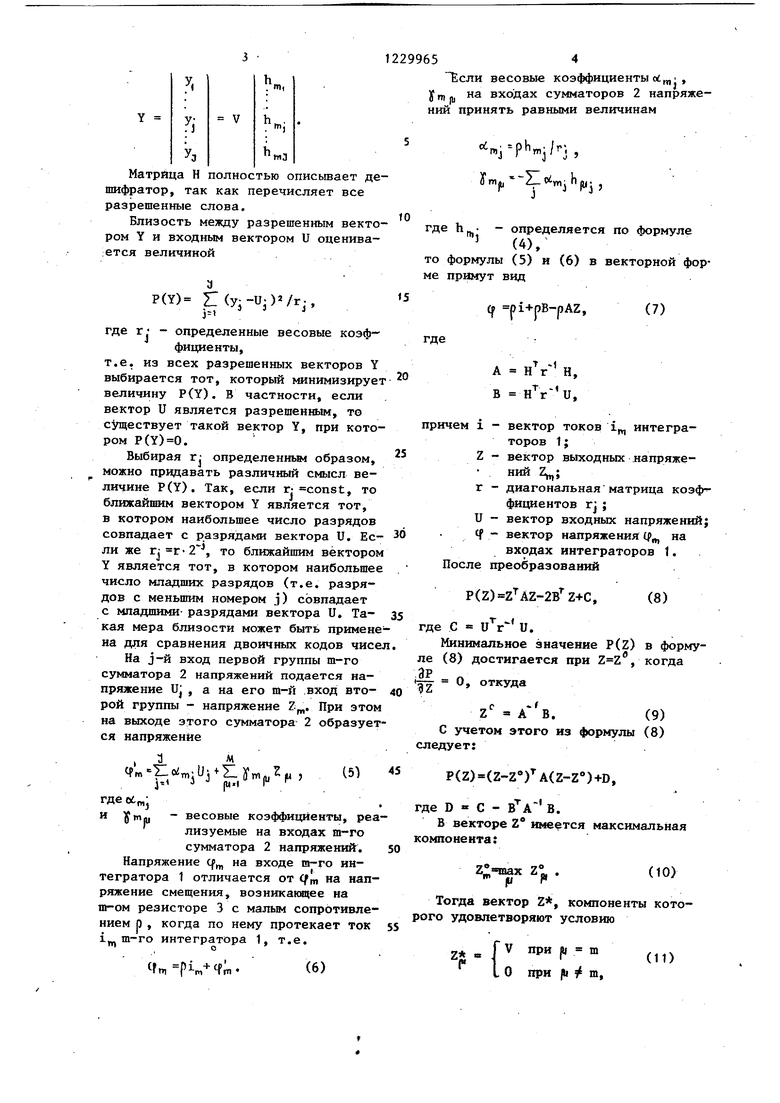

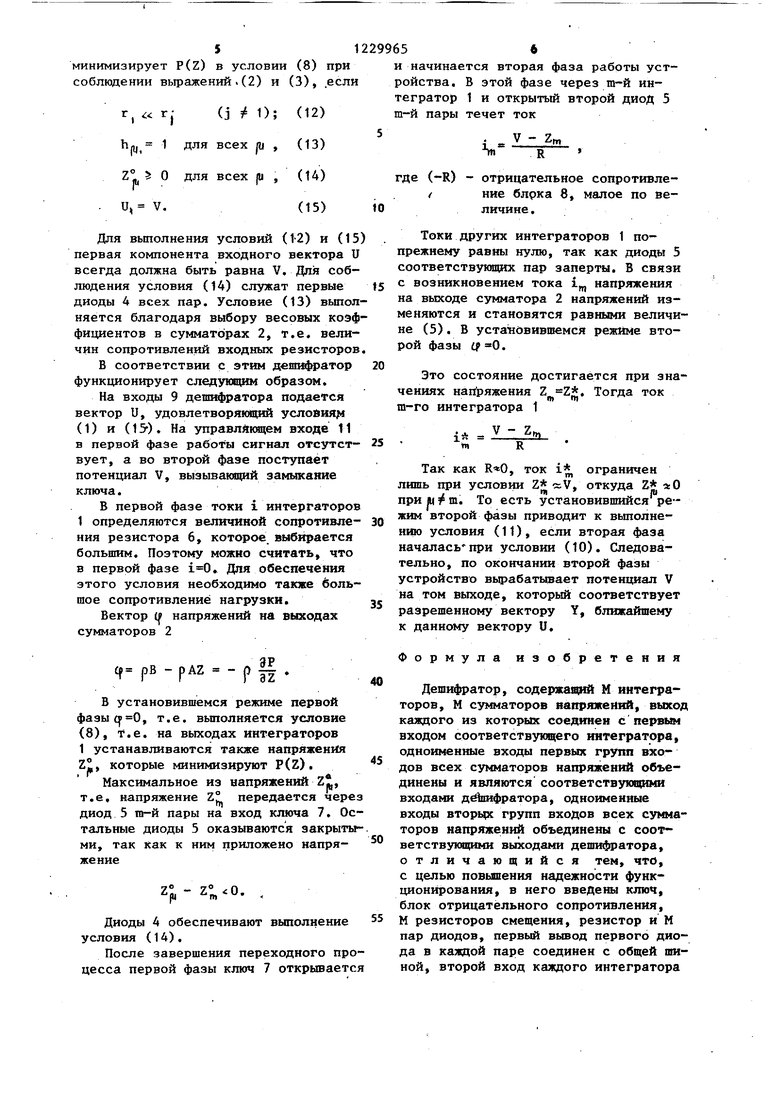

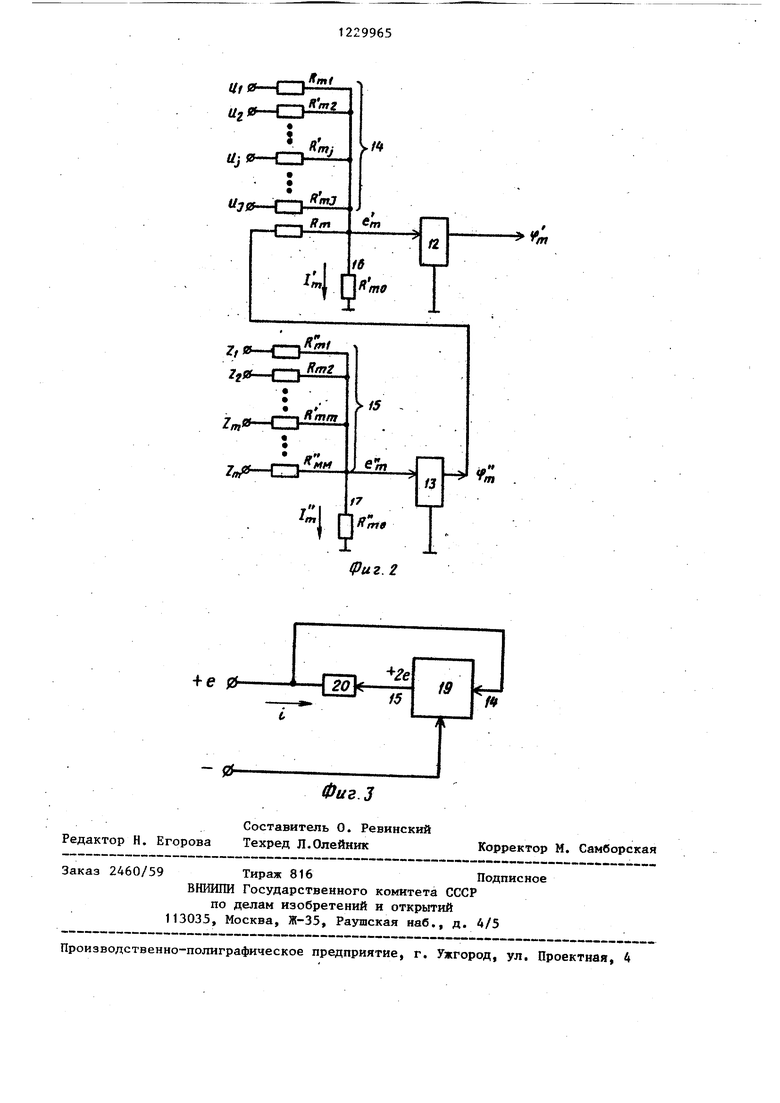

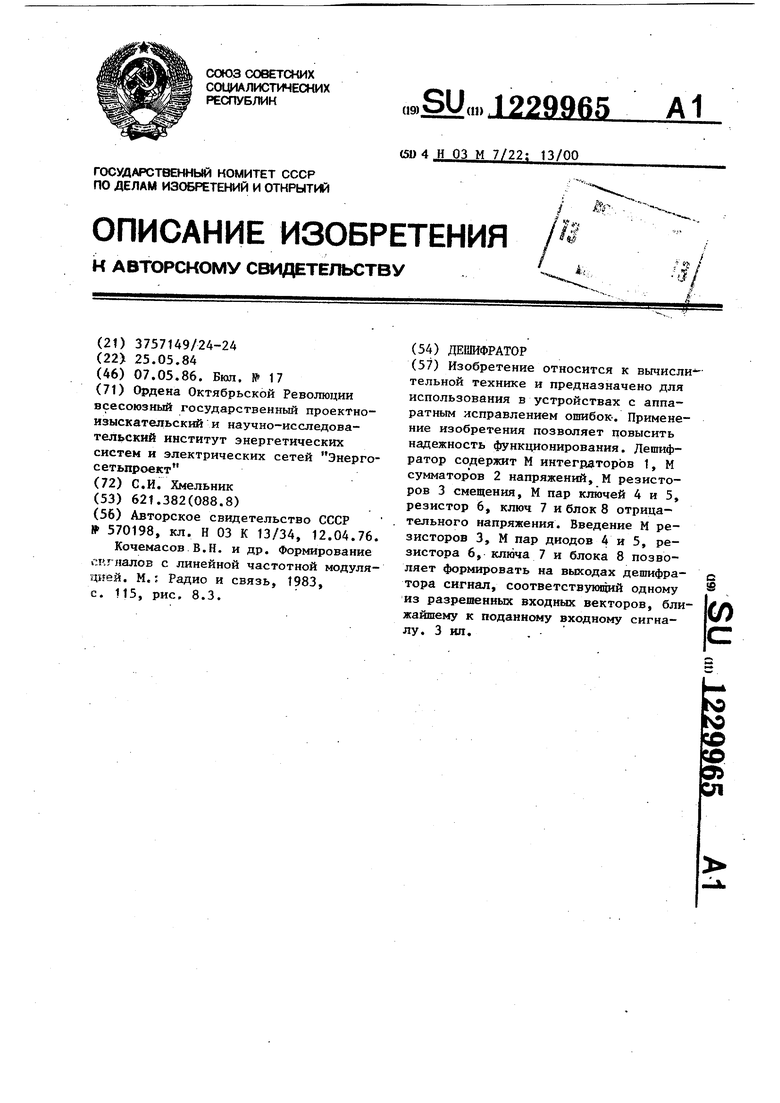

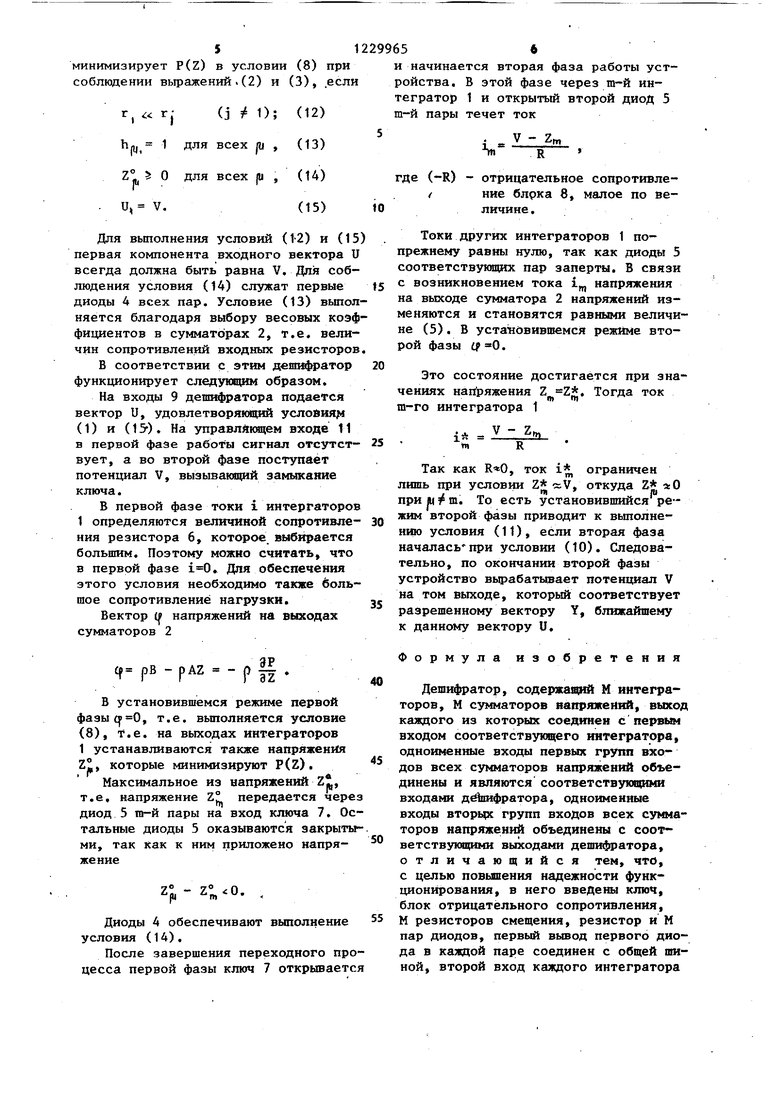

На фиг. 1 представлена функциональная схема дешифратора; на фиг.2 функциональная схема сумматора напряжений; на Лиг. 3 - пример реализации блока отрицательного сопротивления.

Дешифратор содержит М интеграторов 1, М сумматоров 2 напряжений, М резисторов 3 смещения, М пар диодов 4 и 5,. резистор 6, ключ 7, блок 8 отрицательного сопротивления, где М - число выходов дешифратора. Первый вход каждого интегратора 1 соединен с выходом соответствующего сумматора 2, а второй вход через соответствующий резистор 3 смещения подключен к общей шине. Первые выво ды первых диодов 4 всех пар соединены с общей шиной.

Каждый сумматор 2 напряжений име две группы входов. Одноименные вход первых групп всех сумматоров 2 объединены и являются соответствующими входами 9 дешифратора , число котор ЗМ. Одноименные входы вторых групп сумматоров 2 также объединены и подключены ко вторым выводам первых и первым выводам вторых диодов 4 и 5 соответствующих пар и выходам соотв ствующих интеграторов 1, являющихся соответствующими выходами 10 дешифратора, число которых М. Вторые выводы вторых диодов 5 всех пар объеднены и подключены к выходу ключа 7 через резистор 6 соединены с общей Шиной. Управляющий вход ключа 7 явлется управляющим входом 11 дешифратора, вход ключа 7 через блок 8 отрцательного сопротивления соединен с шиной источника питания.

Сумматор 2 напряжений состоит (фиг. 2) из первого и второго усилителей 12 и 13, первой и второй групп 14 и 15 входных резисторов, первого и второго общих резисторов 16 и 17 и дополнительного резистора 18. Первый усилитель 12 - неинвертирующий, второй усилитель 13 - инвертирующий. В первую и вторую группы 14 и 15 входных р1езисторов входит соответственно 1 и М входных резисторов, первые выводы которых являются входами

соответствующих г рупп входов сумматора 2, а вторые выводы объединены и подключены ко входам соответствующих усилителей 12 и 13 и через соответствующие общие резисторы 16 и 17 соединены с общей шиной. Выход второго усилителя 13 через дополнительный резистор 18 подключен ко входу перврго усилит еля 12, выход которого является выходом сумматора 2 напряжений .

Блок 8 отрицательного сопротивления может быть выполнен в виде усилителя 19 и резистора 20, соединенных в соответствии с фиг. 3. Коэффициент усиления усилителя 19 равен 2, при этом ток через резистор 20 имеет величину

1

е - 2е

R

R

где е - напряжение на входе блока 8; R - сопротивление резистора 20,

В основе работы дешифратора лежат следующие математические соотношения.

На входы 9 дешифратора поступает вектор и потенциалов:

Uj(0,V), , 1.

(1)

На выходах 10 дешифратора возникает вектор Z потенциалов:

Z(0,V),

,М,

(2)

причем только один из этих потенциалов равен V, а остальные равны ну- лю, т.е.

(3)

Среди входных векторов U существует множество разрешенных векторов Y, каждый из которых соответствует сигналу на одном из выходов: .

Этот факт можно записать следующим образом: , где И - матрица, с о- держащая 3 строк и М столбцов элементов:

(0,1), ,M,

В частности

tj ui j-i v-r,tJ, j -

ствует разрешенный вектор

j M (4) выходу Z V соответm,

Y

i

V

wa

Матрица Н полностью описьтает дешифратор, так как перечисляет все разрешенные слова.

Близость между разрешенным вектором Y и входным вектором U оценива- ;ется величиной .

P(Y) r(yj-Uj)Vrj ,

где г- - определенные весовые коэф-фициенты,

т.е. из всех разрешенных векторов Y выбирается тот, который в нимизиpyeт величину P(Y). В частности, если вектор и является разрешенным, то существует такой вектор Y, при котором P(Y)0.

Выбирая г; определениьм образом, можно придавать различшлй смысл величине P(Y). Так, если Г; «const, то ближайшим вектором Y является тот, в котором наибольшее число разрядов совпадает с разрядами вектора U. Если же , то ближайшим вектором Y является тот, в котором наибольшее число младших разрядов (т.е. разрядов с меньшим номером j) совпадает с младшими- разрядами вектора U. Такая мера близости может быть применена для сравнения двоичных кодов чисе

На j-й вход первой группы т-го сумматора 2 напряжений подается напряжение Uj , а на его т-й вход вто- рой группы - напряжение Z. При зтом на выходе этого сумматора 2 образуется напряжение

а

На

i

м

У

|U I

- весовые коэффициенты, реализуемые на входах т-го

сумматора 2 напряжений. Напряжение Cf на входе т-го интегратора 1 отличается от fm на напряжение смещения, возниканщее на т-ом резисторе 3 с мальм сопротивлением р, когда по нему протекает ток i т-го интегратора 1, т.е.

tfm pi-m- q

(6)

12299654

TlcnH весовые коэффициенты , у на входах сумматоров 2 напряжений принять равными величинам

,j/r ;,

(I те

,.,

где h.

3

определяется по формуле

(4),

то формулы (5) и (6) в векторной форме примут вид

15

pi+pB-pAZ,

(7)

где

А В

Н,

,

причем 1 - вектор токов ip, интеграторов 1;

Z - вектор выходных напряжений

т - диагональная матрица козф фициентов rj ;

и - вектор входных напряжений;

.

30

tf - вектор напряжения If на

входах интеграторов После преобразований

1.

P(Z)Z AZ-2B Z+C,

(8)

.

4035

uV и.

где С

Минимальное значение P(Z) в форму , когда

ле (8) ЗР

W

достигается при О, откуда

л .f

Z А В,

(9) (8)

45

С учетом атого из формулы следует:

P(Z)((Z-Z )+D,

где D « С - В.

В векторе Z имеется максимальная компонента:

«max

уО

Р«

(10)

Тогда вектор Z, компоненты которого удовлетворяют условию

f

to

при PI m при р э m.

(11)

512299656

минимизирует P(Z) в условии (8) при и начинается вторая фаза работы уст- соблюдений выражений .(2) и (3), .если ройства. В этой фазе через т-й интегратор 1 и открытый второй диод 5 т-й пары течет ток

Г,, Г|

bfu. 1

(j i 1); (12) для всех , (13)

п

V - Zn R

Z° 5 О для всех fu , (14)

(15)

и, V.

Для вьшолненил условий (1-2) и (15) первая компонента входного вектора U всегда должна быть равна V, Для соблюдения условия (14) служат первые диоды 4 всех пар. Условие (13) выполняется благодаря выбору весовых коэффициентов в сумматорах 2, т.е. величин сопротивлений входных резисторов.

В соответствии с этим дешифратор функционирует следующим образом.

На входы 9 дешифратора подается вектор и, удовлетворякщий услойия 1 (1) и (15-). На управлйкщем входе 11 в первой фазе работы сигнал отсутст- вует, а во второй фазе поступает потенциал V, вызывающий замыкание ключа.

В первой фазе токи i интергаторов 1 определяются величиной сопротивле- ния резистора 6, которое выбирается большим. Поэтому можно считать, что в первой фазе Для обеспечения этого условия необходимо также большое сопротивление нагрузки.

Вектор ц напряжений на выходах сумматоров 2

9 рв - р

в - pAZ Р

ЭР 9Z

В установившемся режиме первой фaзыq 0, т.е. вьшолняется условие (8), т.е. на выходах интеграторов 1 устанавливаются также напряжения

7

h

которые минимизируют P(Z). Максимальное из напряжений Zl,

пО. С

т.е. напряжение Z передается через диод 5 т-й пары на вход ключа 7. Остальные диоды 5 оказываются закрытыми, так как к ним приложено напряжение

7° - 1

.

Диоды 4 обеспечивают выполнение условия (14).

После завершения переходного процесса первой фазы ключ 7 открывается

п

V - Zn R

где (-R) - отрицательное сопротивле- ние блрка 8, малое по величине.

Токи других интеграторов 1 по- прежнему равны нулю, так как диоды 5 соответствующих пар заперты. В связи с возникновением тока i напряжения на выходе сумматора 2 напряжений изменяются и становятся равными величине (5). В установившемся режиме второй фазы 6f 0.

Это состояние достигается при зна- иях нап ряжения I т-го интегратора 1

чениях нап ряжения Z Z. Тогда ток

1 Щ

V - Z

IJL.

R

5

0 j

0

5

5

Так как , ток i, ограничен лишь при условии Z c:;V, откуда Z 0 прим/ш. То есть установившийся режим второй фазы приводит к вьшолнению условия (11), если вторая фаза началась при условии (10). Следовательно, по окончании второй фазы устройство вырабатывает потенциал V на том выходе, который соответствует разрешенному вектору Y, ближайшему к данному вектору U.

Формула изобретения

Дешифратор, содержащий И интеграторов, М сумматоров напряжений, выход каждого из которых соединен с первым входом соответствующего интегратора, одноименные входы первых групп входов всех сумматоров напряжений объединены и являются соответствующими входами дешифратора, одноименные входы вторцх групп входов всех сумматоров напряжений объединены с соответствующими выходами дешифратора, отличающийся тем, что, с целью повышения надежности функционирования, в него введены ключ, блок отрицательного сопротивления, М резисторов смещения, резистор и М пар диодов, первый вывод первого диода в каждой паре соединен с общей шиной, второй вход каждого интегратора

через соответствующий резистор смещения подключен к общей шине, выход каждого интегратора соединен с вторым выводом первого и первым выводом второго диодов в соответствующей паре и является соответствукицим выходом . дешифратора, вторые выводы вторых ди9 ч

одов всех пар объединены и подключены к выходу ключа и через резистор - к общей шине, управляющий вход ключа является управляющим входом деигифра- тора, вход ключа через блок отрица- тельного сопротивления подключен к шине источника питания.

/О ч

и, у 2

J S

±:)

Zi 22/от /Af

II

Фиг.З

Редактор Н. Егорова

Составитель О. Ревинский Техред Л.Олейник

Заказ 2460/59 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор М. Самборская

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор для исправления ошибок | 1985 |

|

SU1305873A1 |

| Устройство для регулирования частоты вращения асинхронного электродвигателя | 1990 |

|

SU1758823A1 |

| Амплитудно-фазовый анализатор гармоник | 1985 |

|

SU1272272A2 |

| Табличный преобразователь кодов | 1989 |

|

SU1649669A2 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| Устройство для спектрально-корреляционного анализа | 1987 |

|

SU1467557A1 |

| Устройство для моделирования электромагнитных процессов в асинхронных машинах | 1988 |

|

SU1594569A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1984 |

|

SU1216834A1 |

| Устройство для контроля линейного объекта управления | 1989 |

|

SU1753454A1 |

Изобретение относится к вычисли- тельной технике и предназначено для использования в устройствах с аппаратным исправлением ошибок. Применение изобретения позволяет повысить надежность функционирования. Дешифратор содержит М интеграторов 1, М сумматоров 2 напряжений, М резисторов 3 смещения, М пар ключей 4 и 5, резистор 6, ключ 7 и блок 8 отрицательного напряжения. Введение М резисторов 3, М пар диодов 4 и 5, резистора 6, ключа 7 и блока 8 позволяет формировать на выходах дешифратора сигнал, соответствующий одному из разрешенных входных векторов, ближайшему к поданному входному сигналу. 3 ил. (/

| Дешифратор с коррекцией ошибок | 1976 |

|

SU570198A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кочемасов В.Н | |||

| и др | |||

| Формирование сигналов с линейной частотной модуляцией | |||

| М.: Радио и связь, 1983, с | |||

| Ударно-долбежная врубовая машина | 1921 |

|

SU115A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1986-05-07—Публикация

1984-05-25—Подача