1

Изобретение относится к области цифровой вычислительной техники и может быть использовано, например, в ЭВМ и радиоэлектроннык устройствах.

Известны дешифраторы, исправляющие ошиб-5 ки аходиой информации, в которой используются корректирующие коды 1 .

Недостатками этих устройств является невысокая эффективность исправления многократных ошибок и сложность структур- 10 ных схем.

Известен дешифратор с коррекцией ошн бок, содержащий входной регистр на триггер, трансформато{:)ы, /входные обмотки которьрс подключены в противофазе к выхсн- 15 дам соответствующих триггеров входного регистра 2 .

Недостаток - низкая надежность дешифрации при наличии ошибок в корректирующем коде.20

Целью изобретения является повышение надежности дешифрации при наличии ошибок в корректирующем коде. Для этого дешифратор с коррекцией ошибок, содержащий входной регистр на триггерах, транс4)орматары, вход-25

ные обмотки которых подключены в противофазе к выходам соответствующих триггеров входного регистра, а выходные обмотки, соответствующих трансформаторов соединены последовательно и подключены ко входам пороговых усилителей, содержит дополнительные трансформаторы, пороговые усипитвли выходной ступени и элементы И-ИЛИ. Входы основных и дополнительных пороговых усилителей соединены между собой, а выходы подключены ко нходным обмоткам дополнительных трансформаторов, выходные обмотки которых .соединены последовател1 но и подключены ко входам соответствующих пороговых усилителей выходной ступени, выходы которых подключены к первым входам соответствующих элементов И-ИЛИ, вторые входы которых подключены к выходам дополнительных пороговых усилителей, а выходы элементов И-ИЛИ - к соответствующим выходным шинам.

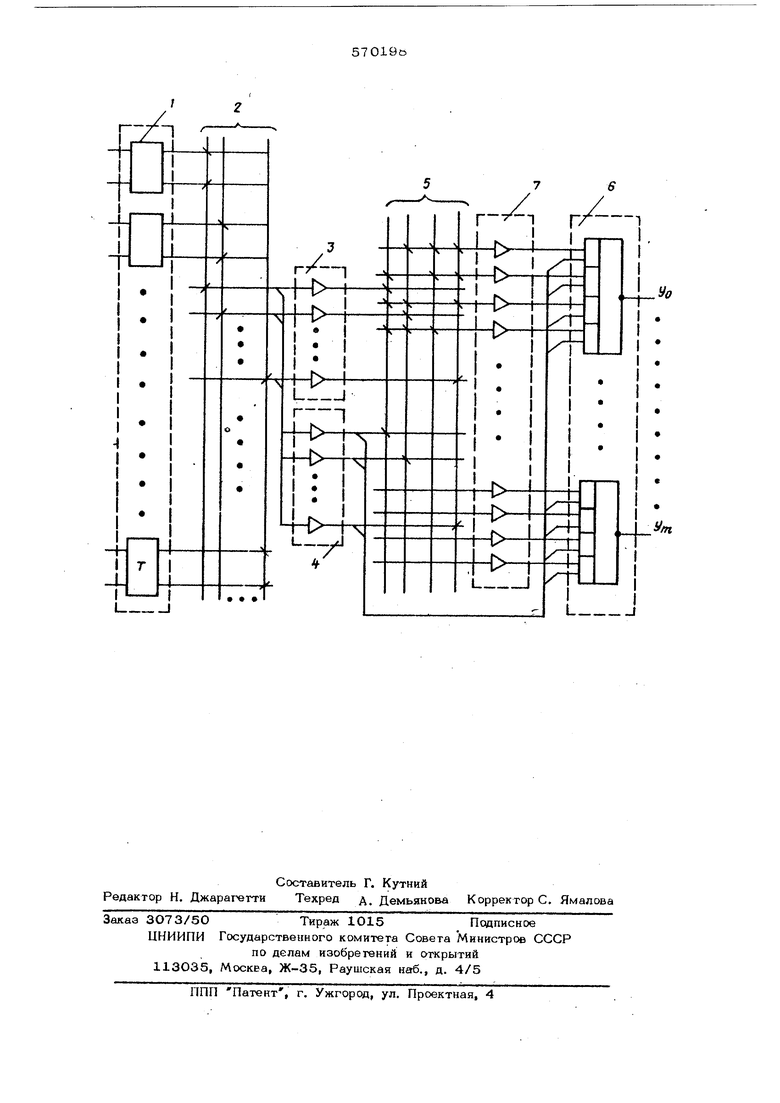

На чертеже представлена струкгурння схема дешифратора.

Она .содержит п триггеров aapf ciioro регистра 1, биполярные Bi.isonbE KOToptifx Подключены к управляющим обмоткам соответственно i - трансформаторов 2 первой ступени. Выходные обмотки каждой t -трансформаторов соединены последовательно в соответствии с матрицей аходных кодов и подкгаочены ко входам дополнительных 3 и основных 4; пороговых усилителей. Порог срабатьшания основных усилителей выбран таким образом, чтобы усиливать сигналы только при совпадении. ЭД С. выходных обмоток всех ( -трансформаторов. Порог срабатывания дополнительных усилителей 3, соответствует сумме ЭДС при наличии одиночной ошибки в данной группе. -С -разрядов адреса. Таких групп может быть неско/хыо (например, четыре). Выход каждого усилителя первой степени нагружен на управляющую обмотку fpanc форматора 5 второй ступени. На первые вхо ды И логических элементов И-ИЛИ выходниго регистра в подключены пороговые уси литьли 7 второй ступени, на входах которы суммируются сигналы с выходных обмоток соответствующих трансформаторов 5, а на вторые В.ХОДЫ логических элементов И-ИЛИ 6 подключены выходы основных пороговых усилителей. Устройство работает следующим; образом В исходном состоянии триггера входного регистра. 1 установлены в соответствии с кодом адреса. При этом ЭДС в выходных обмотках все.х трансформаторов дешифратора нравна нулю, пороговые усилители закрыты и потенциалы выходных шин дешиф ратора. соответствуют невозбужденному ростоянию. При поступлении стробируюд1его импульс на входной регистр 1 (в.ход триггеров вход ного регистра 1) сигналы, соогвегствующие коду адреса намагничивают сердечники трансформаторов первой ступени к на в.ходах пороговых усилителей первой ступени формируются сигналы, равные сумме ЭДС выходных обмоток е подключенных трансформаторов. В группе основных пороговых усилителей первой ступени выходные сиг- налы формируются только в те.х усилителях, на в.ходах которых все f. ЭДС будут иметь рабочую полярность, в группе дополнительных пороговых усилителей выходные сигналы формируются также и при наличии одиночных ошибок в любой группе 2 -разрядов адреса. Сформированные выходные сигналы у основных пороговых усилителей первой ступени с помощью возбуждающих оСмоток намагнитят сердечники ряда трансформаторов второй ступени, вследствие чего на входах соответствующн.х пороговых усилителей второй ступени потенциалы превысят порог срабатывания. Выходные сигналы этих усилителей поступают иа входы И логических элементов И/ИЛИ 6 выход 0 ° регистра. При этом рабочий потен«иал будет сформирован на вьгеоде того элемента И-ИЛИ, для которого .хотя бы на дной иа схем И совпадут входные сигналы, поступающие с выходов основных пороговых усилителей и с выходов пороговых усилителей второй ступени. Соотношение сигнал/ помеха на входах пороговых усилителей при двухступенчатой схеме построения дешифратора оказывается выше чем в извест ных одноступенчатых схемах магнитных дешифраторов. Формула изобретения Дешифратор с коррекцией ошибок, содержаший входной регистр на триггерах, трансформаторы, входные обмотки которых подключены в противофазе к выходам соответствующих триггеров входного регистра, а выходные обмотки соответствующих трансформаторов соединены .последовательно и подключены) ко входам пороговых усилителей, о т личающийся том, что, с целью повышения надежности дешифрации, при наличии ошибок в корректируюшем коде , он содержит дополнительные трансформаторы, пороговые усилители, пороговые усилители выходной ступени и элементы И-ИЛИ, причем входы основных и дополнительных пороговых усилителей соединены между собой, а выходы подключены ко входным обмоткам дополнительных трансформаторов, выходные обмотки которых соединены последовательно И подключены ко входам соответствующих пороговых усилителей выходной ступени, выходы которых подключены к первым входам соответствуюших элементов И-ИЛИ, вторые входы которых, подключены к выходам дополнительных пороговых усилителей, а выходы элементов И-ИЛИ к соответствующим выходным щинам. Источники информации, принятые во вни-j мание при экспертизе; 1,Авторское свидетельство СССР № 226944, кл. G 06 F 5/ОО, 1968. 2.Зыков Ф, Н. Синтез трансформаторных схем с избыточным ко/ 1ированием . Наукова думка , Киев, 1970, с. 29-32, рис. 8.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1978 |

|

SU743039A1 |

| Запоминающее устройство | 1982 |

|

SU1016832A1 |

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| ЬИЬЛИО', ЕКА | 1973 |

|

SU365707A1 |

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ из постоянного ТРАНСФОРМАТОРНОГО ЗАПОМИНАЮЩЕГО | 1973 |

|

SU377868A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Запоминающее устройство | 1973 |

|

SU560256A1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

Авторы

Даты

1977-08-25—Публикация

1976-04-12—Подача