Изобретение относится к интегральной электронике и может быть исполь- зовано для установки триггерных схем в исходное состояние непосредственно при включении напряжения питания, а таже в интегральных схемах (БИС) на дополняющих МДП-транзисторах

Цель изобретения - упрощение устройства при интегральном исполнении.

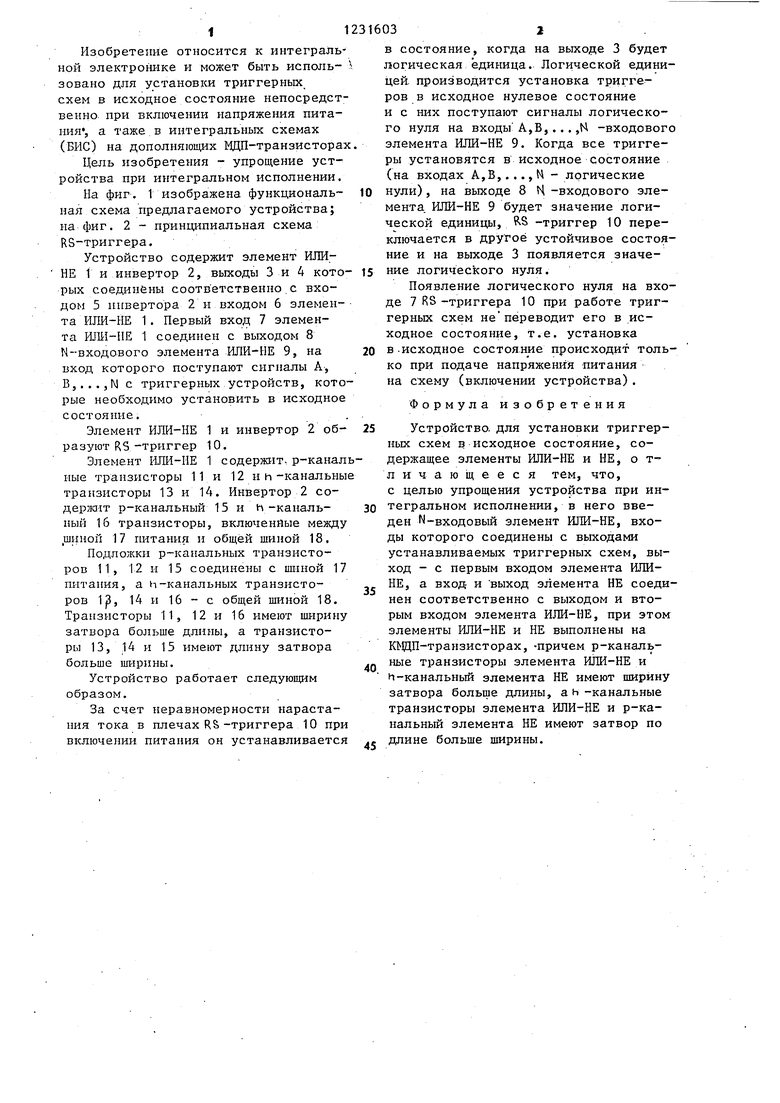

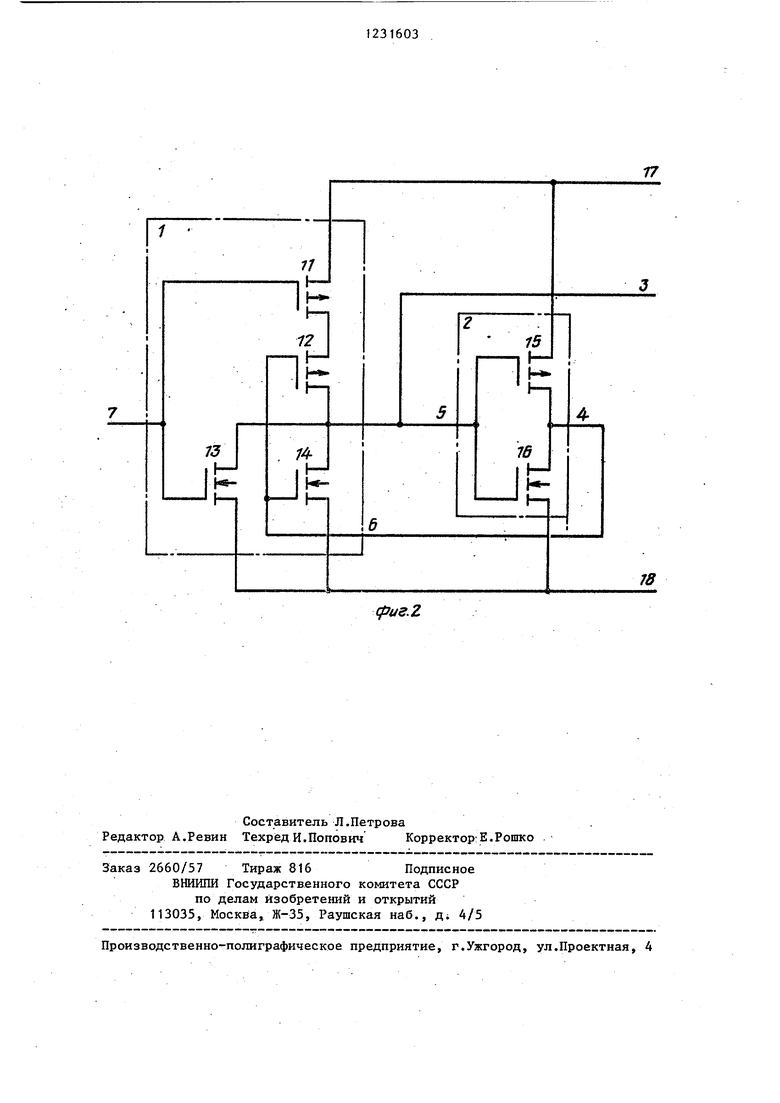

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 принципиальная схема RS-триггера.

Устройство содержит элемент ИЛИ- НЕ 1 и инвертор 2, выходы 3 и 4 кото- рых соединены соотв етственно. с входом 5 инвертора 2 и входом 6 элемента ИЛИ-НЕ 1. Первый вход 7 элемента ШШ-ПЕ 1 соединен с выходом 8 N-входового элемента ИЛИ-ИЕ 9, на вход которого поступают сигналы А, B,...,N с триггерных устройств, которые необходимо установить в исходное состояние.

Элемент ИЛИ-НЕ 1 и инвертор 2 образуют RS -триггер 10.

Элемент 1ШИ-ПЕ 1 содержит, р-канал ные транзисторы 11 и 12 иh-канальны транзисторы 13 и 14. Инвертор 2 содержит р-канальный 15 и h -канальный 16 транзисторы, включенные между ,шцной 17 питания и общей шиной 18.

Подложки р-канальных транзисторов 11, 12 и 15 соединены с шиной 17 питания, а и-канальных транзисторов 1, 14 и 16 - с общей шиной 18. Транзисторы 11, 12 и 16 имеют ширину затвора больше длины, а транзисторы 13, 14 и 15 имеют длину затвора больше ширины.

Устройство работает следующим образом.

За счет неравномерности нарастания тока в плечах RS-триггера 10 при включении питания он устанавливается

;

12316032

в состояние, когда на выходе 3 будет логическая единица. Логической едини

0

S

.

5

0

5

0

цей производится установка триггеров в исходное нулевое состояние и с них поступают сигналы логического нуля на входы А,Б,... ,Ы -входового элемента ИЛИ-НЕ 9. Когда все триггеры установятся в исходное состояние (на входах A,B,...,N - логические нули), на выходе 8 U -входового элемента. ИЛИ-НЕ 9 будет значение логической единицы, RS -триггер 10 переключается в другое устойчивое состояние и на выходе 3 появляется значение логического нуля.

Появление логического нуля на входе 7 RS-триггера 10 при работе триггерных схем не переводит его в исходное состояние, т.е. установка в.исходное состояние происходит только при подаче напряжения питания на схему (включении устройства).

Формула изобретения

Устройство, для установки триггерных схем в исходное состояние, содержащее элементы ИЛИ-НЕ и НЕ, отличающееся тем, что, с целью упрощения устройства при интегральном исполнении, в него введен М-входовый элемент ИЛИ-НЕ, входы которого соединены с выходами устанавливаемых триггерных схем, выход - с первым входом элемента ИЛИ- НЕ, а вход- и выход элемента НЕ соединен соответственно с выходом и вторым входом элемента ИЛИ-НЕ, при этом элементы ИЛИ-НЕ и НЕ выполнены на КЩП-транзисторах, -причем р-каналь- ные транзисторы элемента ИЛИ-НЕ и и-канальный элемента НЕ имеют ширину затвора больше длины, а h -канальные транзисторы элемента ИЛИ-НЕ и р-канальный элемента НЕ имеют затвор по длине больше ширины.

,h-J

73

14UСоставитель Л.Петрова Редактор A.Ревин Техред И.Попович Корректор;Е.Рошко

Заказ 2660/57 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва Ж-35, Раушская наб., д; 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

75

IiH- :

It7

KM

(.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УСТАНОВКИ ТРИГГЕРНЫХ СХЕМ В ИСХОДНОЕ СОСТОЯНИЕ | 2004 |

|

RU2262186C1 |

| Устройство считывания для программируемой логической матрицы | 1988 |

|

SU1566410A1 |

| Входное устройство для электронных часов | 1990 |

|

SU1774471A1 |

| Тактируемый @ -триггер | 1985 |

|

SU1267590A1 |

| РАДИАЦИОННО-СТОЙКАЯ ЭНЕРГОНЕЗАВИСИМАЯ ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 2014 |

|

RU2563548C2 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| @ @ -Триггер | 1983 |

|

SU1091315A1 |

| @ -Триггер с предпочтительной установкой в @ -состояние | 1982 |

|

SU1075380A1 |

Изобретение относится к инте- . тральной электронике. Предназначено для установки триггерных схем в исходное состояние непосредственно при включении напряжен ия питания. Может использоваться в интегральных схемах (БИС) на дополнительных ЬЩП-траизис- торах. .Цель изобретения - упрощение устройства в интегральном исполнении. Устройство содержит логический элемент (ЛЭ) ИЛИ-НЕ 1, инвертор 2,М-вхо- довый ЛЭ ИЛИ-НЕ-9. На вход этого элемента поступают сигналы от триггерных устройств, которые необходимо устанавливать в исходное состояние. ЛЭ ИЛИ-НЕ 1 и инвертор 2 образуют RS-триггер, принципиальная схема которого приводится в описании изобретения. 2. ил. 70 (Л В .8 /V 00 о: о 00

| Устройство установки триггерных схем | 1979 |

|

SU864579A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для формирования устано-ВОчНОгО иМпульСА | 1979 |

|

SU819964A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-05-15—Публикация

1984-07-20—Подача