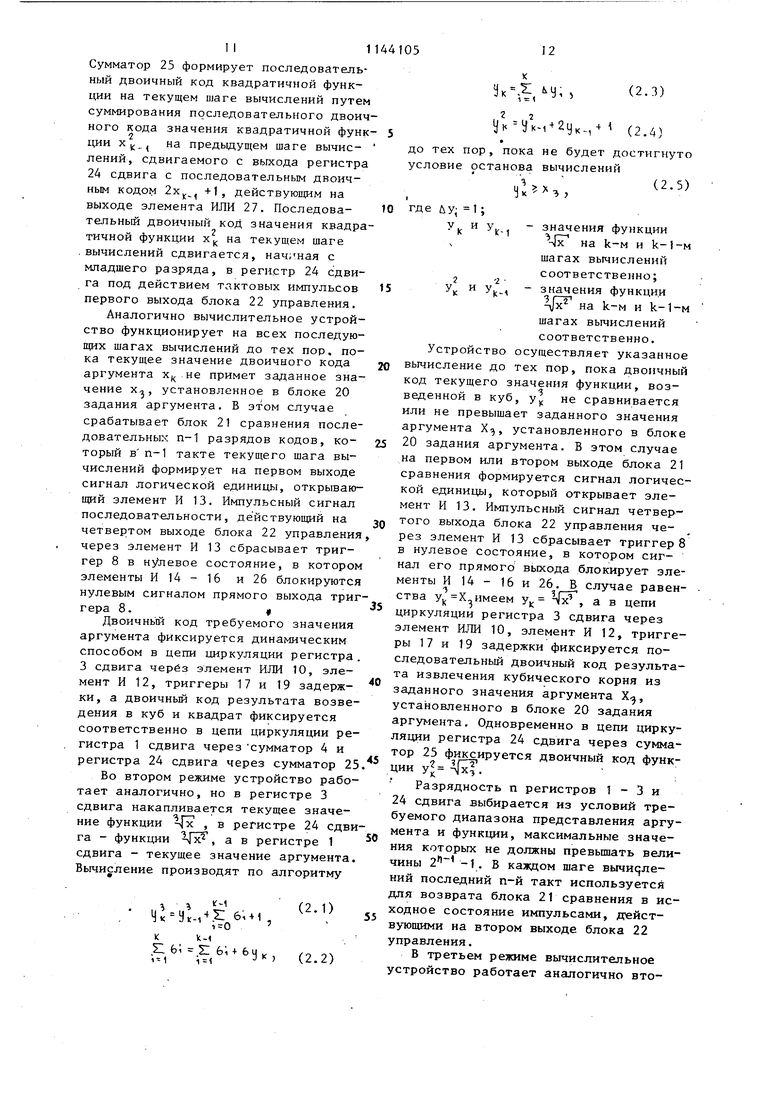

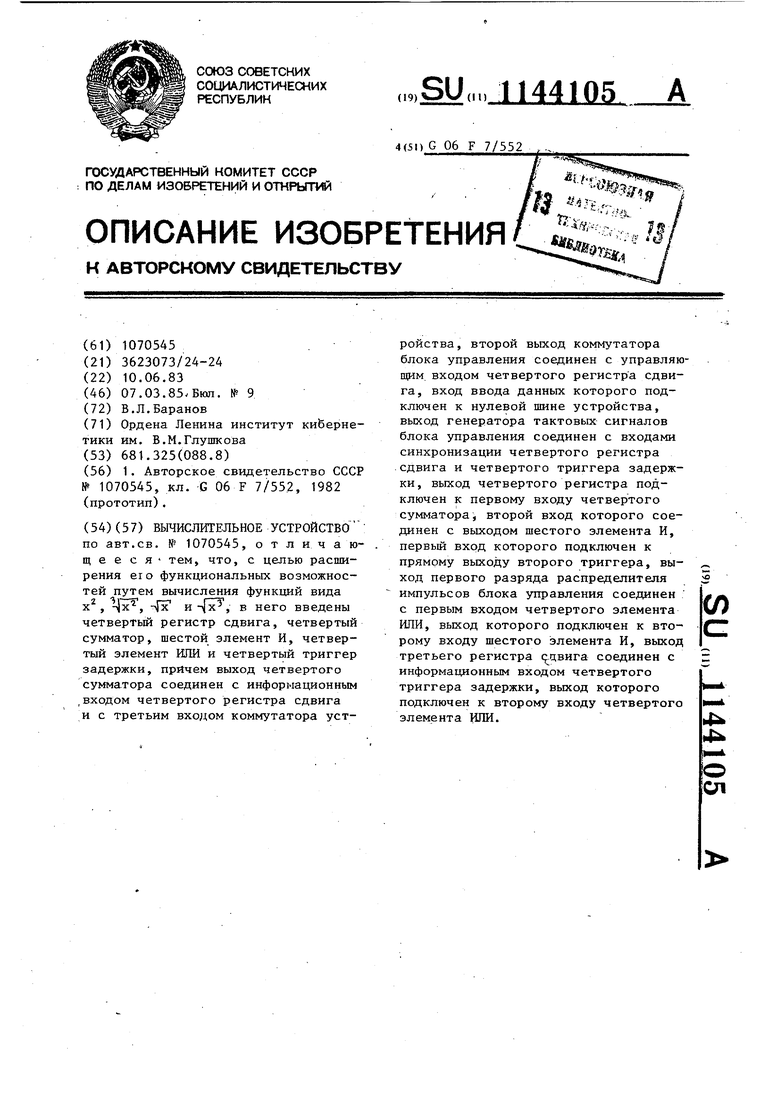

11 Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых системах управления и в устройствах воспроизведения функциональной зависимости, ilo основному авт.св. N 1070545, известно устройство содержащее три регистра сдвига, два сумматора, два триггера, три элемента ИЛИ, два элемента И, два трипера задержки, причем выход первого регистра сдвига соединен с первым входом первого сум матора, выход которого соединен с ий формационнь№ входом первого регистра сдвига, выход второго регистра сдвига соединен с первым входом первого элемента Ш1И и с первым входом второ го сумматора, выход которого соединен с информационным входом второго регистра сдвига, выход третьего регистра сдвига соединен с входом сбро са первого триггера и с первым входом второго элемента ИЛИ, выход кото рого соединен с первым входом первого элемента И, инверсный выход первого триггера соединен с вторым входом первого элемента И, выход которого соединен с информационным входом пер вого триггера задержки, выход треть го элемента ИЛИ соединен с первым входом второго элемента И, третий сумматор 5 блок сравнения, коммутатор блок задания аргумента, третий, четвертый, пятый элементы И, третий триггер задержки, блок управления, содержащий генератор тактовых импуль сов, распределитель импульсов, генератор одиночных импульсов, коммутатор, элемент НЕ и элемент задержки, причем выход генератора тактовых импульсов соединен с входом распределителя импульсов и с входом синхрони зации блока сравнения, выход П-1-го разряда распределителя импульсов сое дивен с информационным входом генера тора одиночных импульсов 5 выход П-го разряда распределителя импульсов сое динен с первым входом пятого элемента И и входом сброса блока сравнения выход первого разряда распределителя импульсов соединен с вторым входом первого элемента ИЛИ, выход /1-1-го разряда распределителя импульсов сое динен через элемент задержки с вторым входом второго элемента И, выход генератора одиночных импульсов соеди нен с информационным входом второго 52 триггера, вход управления генератора одиночных импульсов соединен с первым выходом коммутатора блока, управляющий вход коммутатора блока через элемент НЕ соединен с нулевой шиной устройства, второй выход коммутатора блока соединен с первым входом третьего элемента ИЛИ и с управляюид1ми входами первого, второго и третьего регистров сдвига, выходы с первого по П -и разрядов распределителя импульсов соединены соответственно с входами блока задания аргумента, второй вход первого сумматора соединен с выходом третьего элемента И, первый вход которого соединен с выходом первого элемента ИЛИ, второй вход второго сумматора соединен с выходом четвертого элемента И, первый вход которого соединен с выходом третьего сумматора, первый и второй вход которого соединены с выходами первого и третьего триггеров задержки соответственно, информационный вход третьего регистра сдвига соединен с выходом третьего триггера задержки, информационный вход которого соединен с выходом первого триггера задержки, вход синхронизации которого соединен с входами синхронизации второго и третьего триггеров задержки, с входами синхронизации первого, второго и третьего регистров сдвига, с входом синхронизации блока сравнения, прямой выход первого триггера соединен с информационным входом второго триггера задержки, выход которого соединен с вторым входом второго элемента ИЛИ, информационный вход первого триггера соединен с выходом пятого элемента И, прямой выход триггера соединен с вторыми входами третьего, четвертого и пятого элементов И, вход Сороса второго триггера соединен с выходом второго элемента И, первый и второй выходы блока сравнения соединены соответственно .с вторым и третьим входами третьего элемента ИЛИ, входы ввода данных первого, второго и третьего регистров сдвига соединены с нулевой шиной устройства, первый и второй информационные входы блока сравнения соединены соответственно с выходами коммутатора устройства и блока задания аргумента, первый и второй входы коммутатора устройства соединены с выходами первого сумматора и первого элемента И соответственно 1J . Недостаток известного устройства заключается в том, что оно не может |-3 I- вычислять функции вида х ,-S х , -чх и Чх Цель изобретения - расширение функциональных возможностей путем вычисления функций вида х , Чх , -ix и-{. Поставленная цель достигается тем что в вычислительное устройство введены четвертый регистр,сдвига, четвертьй сумматор, шестой элемент И, четвертый элемент ИЛИ и четвертый триггер задержки, причем выход четвертого сумматора соединен с информа ционным входом четвертого регистра сдвига и с третьим входом коммутатора устройства, второй выход коммутатора блока управления соединен с управляющим входом четвертого регистра сдвига, вход-ввода данных которого подключен к нулевой шине устройства, выход генератора тактовых сигналов блока управления соединен с входами синхронизации четвертого регистра сдвига и четвертого триггера задержки, выход четвертого регистра сдвига подключен к первому входу четвертого сумматора, второй вход которого соединен с выходом шестого элемента И, первый вход которого подключен к пря мому выходу второго триггера, выход первого разряда распределителя импульсов блока управления соединен с первым входом четвертого элемента ИЛИ, выход которого подключен к второму входу шестого элемента И, выход третьего регистра сдвига соединен с информационньм входом четвертого триггера зaд epжки, выход которого подключен к второму входу четвертого элемента ИЛИ. На фиг 1 изобрай:ена структурная схема вычислительного устройства; на фиг. 2 - структурные схемы блока задания аргумента и блока управления Вычислительное устройство содержит первый, второй и третий регистры 1 - 3 сдвига, первый, второй и третий сумматоры 4 - 6, первый RSтриггер 7, второй RS-триггер 8, первый, второй и третий элементы ИЛИ 9 - И, первый, второй, третий, четвертьй и пятый элементы И 12 - 16, первый, второй и третий триггеры 17-19 задержки, блок 20 задания аргумента, блок 21 сравнения, блок 22 управления, коммутатор 23 и допол нительно четвертый.регистр 24 сдвига, четвертый сумматор 25, шестой элемент И 26, четвертый элемент ИЛИ 27 и четвертый триггер 28 задержки. Выход регистра 1 сдвига соединен с первым входом сумматора 4, выход которого соединен с информационным входом регистра 1 сдвига. Выход регистра 2 сдвига соединен с первым входом элемента ИЛИ 9 и с первым входом сумматора 5, выход которого соединен х: информационным входом регистра 2 сдвига. Выход регистра 3 сдвига соединен с входом сброса триггера 7 и с первым входом элемента ИЛИ 10, выход которого соединен с первым входом элемента И 12. Инверсный выход триггера 7 соединен с вторым входом элемента И 12, выход которого соединен через триггер 17 задержки . с информационным входом триггера 19 задержки. Выход элемента ИЛИ 11 соединен с первым входом элемента И 13. Второй вход сумматора 4 соединен с выходом элемента И 14, первый вход которого соединен с выходом элемента ИЛИ 9. Второй вход сумматора 5 соединен с выходом элемента И 15, первый вход которого соединен с выходом сум-: матора б, первый и второй входы которого соединени соответственно с выходами триггеров 17 и 19 задержки. Информационный вход регистра 3 сдвига соединен с выходом триггера 19 задержки, вход синхронизации которого соединен с входами синхронизации триггеров 17 и 18 задержки, с входами синхронизации регистров 1 - 3 сдвига, с входом синхронизации блока 21 сравнения и с первым выходом блока 22 управления.. Прямой выход триггера 7 соединен через триггер 18 задержки с вторым входом элемента ИЛИ 10. Информационный вход триггера 7 соединен с выходом элемента И 16, вход которого соединен с входом сброса блока 21 сравнения и с вторым вьКодом блока 22 управления. Прямой выход триггера 8 соединен с вторыми входами элементов И 14 - 16. Третий и четвертый выходы блока 22 управления соединены соответственно с вторым входом элемента ИЛИ 9 и с вторым входом элемента И 13. Вход сброса и информационный вход триггера 8. соединены соответствеино с выходом элемента И 13 и с пятым выходом блока 22 управления. Первый и второй

выходы блока 21 сравнения соединены соответственно с вторым и третьим входами элемента ИЛИ t1, первый вход которого соединен с шестым выходом блока 22 управления и с управляющи- 5 ми входами регистров 1 - 3 сдвига, входы ввода данных которых соединены с нулевой шиной устройства. Первый и второй информационные входы блока 21 сравнения соединены соответ- Ю ственно с выходом коммутатора 23 и с выходом блока 20 задания аргумента , входы которого соединены с соответствующими выходами седьмой группы выходов блока 22 управления. Пер- tS вый и второй входы коммутатора 23 соединены соответственно с выходами сумматора 4 и элемента И 12.

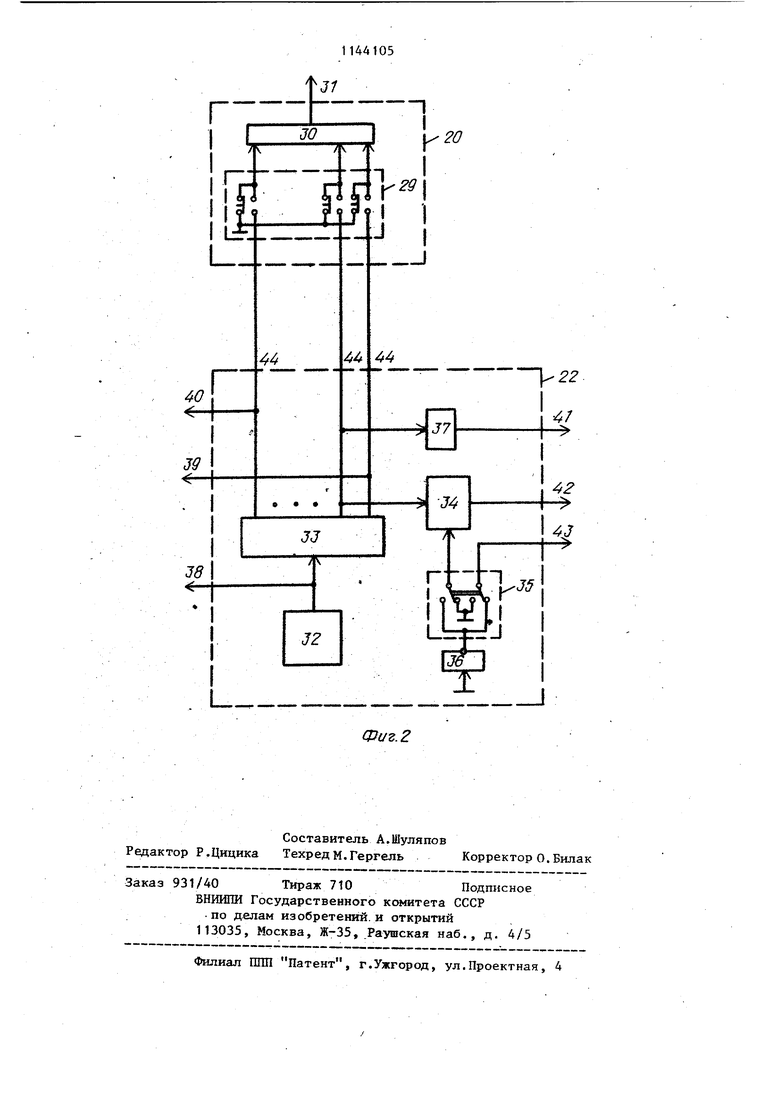

Информационный вход регистра 24 сдвига соединен с третьим входом ком-20 мутатора 23 и с выходом сумматора 25, первый и второй входы которого соединены соответственно с выходом регистра 24 сдвига и выходом элемента И 26. Первый выход блока 22 управле- 25 ния соединен с входами синхронизации регистра 24 сдвига и триггера 28 задержки, информационный вход которого соединен с выходом регистра 3 сдвига. Шестой выход блока 22 управ- ЗО ления соединен с управляющим входом регистра 24 сдвигаj вход ввода данных которого соединен с нулевой вмной устройства. Третий выход блока 22 управления соединен с первь1м вхо- j. дом элемента ИЛИ 27, второй вход кс- . .торого соединен с выходом триггера 28 задержки. Прямой выход триггера 8, соединен с первым входом элемента И 26, второй вход которого соединен о с выходом элемента ИЛИ 27

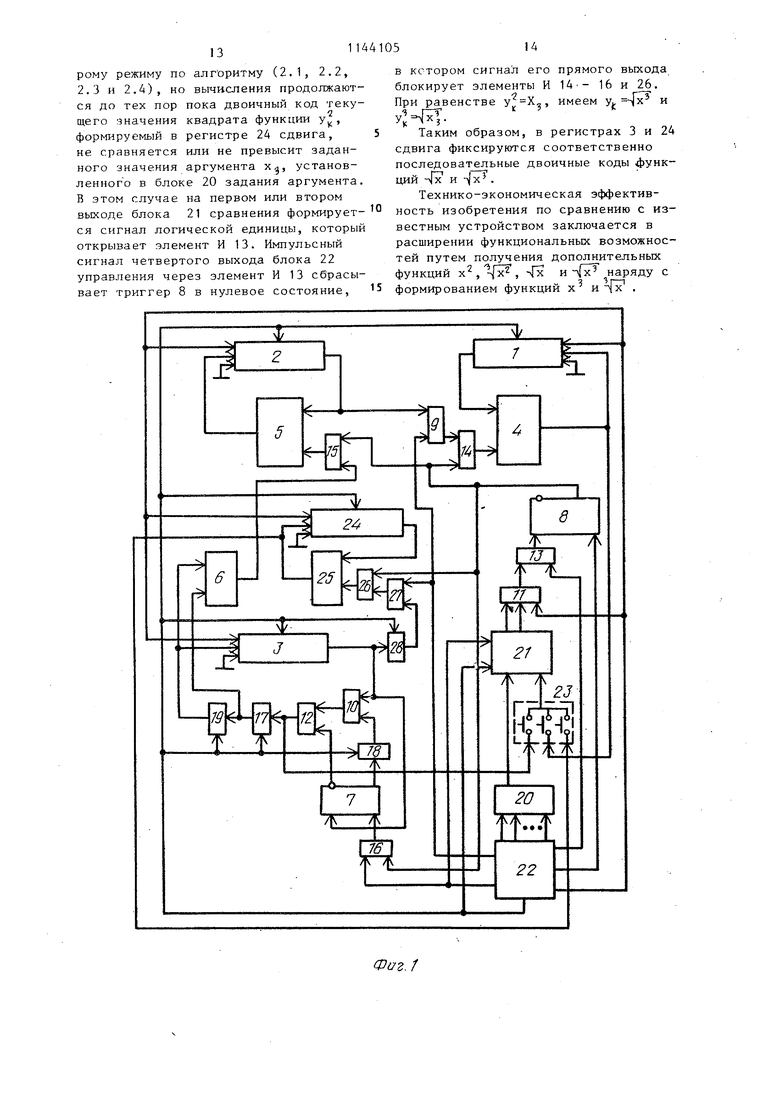

Блок 20 задания аргумента (фиг«2) содержит коммутатор 29 и элемент ИЛИ 30,

Входы коммутатора 29 соединены с 45 соответствующими входами блока 20 задания аргумента. Выходы коммутатора 29 соединены с соответствующими входами элемента ИЛИ 30, выход которого является выходом 31 блока 20 50 задания аргумента.

Блок 22 управления (фиг, 2) содержит генератор 32 тактовых импульсов, распределитель 33 импульсов генератор 34 одиночных кмпульсов, коммутатор 35, элемент НЕ 36 и элемент 37 задержки на длительность тактового : импульса. Выход генератора 32

вых импульсов соединен с входом pacпределителя 33 импульсов и является первым выходом 38 блока 22 управления. Выход п-го и первого разрядов распределителя 33 импульсов соединены соответственно шинами 39 и 40 с вторым и третьим выходами блока,. 22 управления. Выход п-1-го разряда распределителя 33 импульсов соединен с информационным входом генератора 34 одиночных импульсов и через элемент 37 задержки - с четвертым выходом 41 блока 22 управления, пятый выход 42 которого соединен с выходом генератора 34 одиночных импульсов, вход управления которого соединен с первым выходом коммутатора 35, вход которого через элемент НЕ 36 соедине с нулевой шиной устройства. Второй выход коммутатора 35 соединен с шестым выходом 43 блока 22 управления, выходы с первого по п-й разряды распределителя 33 импульсов являются седьмой группой выходов 44 блока 22 управления.

Вычислительное устройство работает следующим образом.

В исходном состоянии на шестом выходе блока 22 управления действует сигнал логической единицы, который поступает на управляющие входы регистров 1 - 24 сдвига и устанавливает их в нулевое состояние , поскольку на их входах ввода данных действует сигнал логического нуля с нулевой шины устройства. Сигнал логической единицы на шестом выходе блока 22 отправления формируется с помощью коммутаторов 35. В исходном состоянии коммутатор 35 подключает выход элемента НЕ 36 к шине 43 шестого выхода блока 22 управления (фиг. 2). Сигнал логической единицы шестого выхода блока 22 управления через элемент ИЛИ 11 открьшазт элемент И 13, через который на вход сброса триггера 8 поступает последовательность импульсов четвертого выхода блока 22 управления, на пятом выходе которого действует сигнал логического нуля. Триггер 8 устанавливается в нулевое состояние и блокирует сигналом прямого выхода элементы И 14 - 16 и 26. Триггер 7 устанавливается в нулевое состояние нулевым сигналомвыхода регистра 3 сдвига.

Таким образом, в исходном состояНИИ регистры 1 - 3 и 24 сдвига, а также триггеры 7 и 8 находятся в нулевом состоянии. Из сигналов генератора тактовых импульсов распределитель 33 импульсов формирует на п выходах (п-ко лическо разрядов регистров 1, 2 и 24) п последовательностей импульсов длительностью t, периодом и , сдвинутых одна относительно:другой б 1/, где f - частота такна время товых импульсов С помощью коммутатора 29 блока 20 задания аргумента набирают требуемый двоичный код аргумента-, Комму татор 29, выполненный, например, в виде переключателя на п направлений подключает в единичных разрядах празрядного двоичного кода аргумента соответствующий выход распределителя 33 импульсов к входу элемента ИЛИ 30, на выходе которого формирует ся последовательный двоичный код заданного значения аргумента. С помощью коммутатора 23, выполненного, например, в виде переклювают требуемый операционный режим работы вычислительного устройства. В первом режиме формирования фун ций X и х коммутатор 23 подключае к первому информационному входу бло ка 21 сравнения выход элемента И 12 Во втором и третьем режимах комм татор 23 подключает к первому инфор мационному входу блока 21 сравнения сумматоров 4 и 25 соответственно. Во втрром режиме вычислитель ное устройство формирует.функции -«х и П Д в третьем режиме - функци -{з и -4х. : Рассмотрим работу в первом режиме, т.е. в режиме формирования квад ратичной и кубической функций. В этом режиме вычислительное уст ройство реализует следуншр1е соотношения. а К-Ч .-fi: б;м i 1 К |с, .ZI 6i SI 6i -t-exwi«t,.,.2Xk.,4 где Хц - значение аргумента на k-M шаге вычисления ;значения квадратичной функции на k-Mи k-1-м шагах вычисления ; уЗ х значения кубичесл,, л,. кой функции на k-M и k-1-м шагах выч-числения. После установки в блоке 20 зада- i ния аргумента двоичного кода заданного значения аргумента и установки коммутатором 23 режима работы осуществляется пуск устройства посредством коммутатора 35 блока 22 управ-i ления. Переключение коммутатора 35 в режим вычислений обеспечивает поступление сигнала логической единицы с выхода элемента НЕ 36 на вход управления генератора 34 одиночных импул г сов, который формирует из последова-: тельности импульсов п-1-го разряда I распределителя 33 иг-шульсов одиночный импульс, поступающий по шине 42 : на пятый выход блока 22 управления и на информационный вход триггера 8, Триггер 8 устанавливается в единичное состояние, в котором сигнал логической единицы его прямого выхода открывает элементы И14-1би26. Элемент И 16 подключает информационный вход триггера 7 к второму выходу блока 22 управления, на котором действует последовательность импульсов п-го разряда распределителя 33 импульсов. Каждый импульс этой последовательности определяет конец однрго шага вычислений. За один шаг вычислений содержимое регистра 3 сдвига имеет п-2 двоичных разрядов и дополняется триггерами 17 и 19 задержки на такт до п разрядов. В регистре 3 сдвига формируется текзпций двоичный код аргумента Xi согласно соотношения (1.3). Рассмотрим работу регистра 3 сдвига на k-M шаге вычислений в течение п тактов, так как предьщущие и все последующие шаги вычислений выполняются аналогичным образом. Триггер 7 устанавливается в единичное срстояние в п-м такте k-1-го шага вычислеНИИ импульсом второго выхода блока 22 управления. К моменту первого такта следующего k-ro шага на выходе триггера 18 задержки на такт формируется сигнал логической едини1№1, который через элемент ИЛИ 10 поступает на первый вход элемента И 12, закрытого сигналом логического нуля инверсного выхода триггера 7. Возвра триггера 7 в нулевое состояние обеспечивает первый нулевой сигнал в любом разряде, начиная с младшего двоичного кода, который сдвигается с выхода регистра 3 сдвига под действи ем тактовых импульсов первого выхода блока 22 управления. Например, если рассматривается восьмой шаг (), то с выхода регистра 3 сдвига сдвигается двоичный код 0111 (). В этом случае триггер 7 сбросится в нулевое состояние нулевым сигналом четвертого разряда двоичного кода. сдвигаемого с выхода регистра 3 сдви га. Зозврат триггера 7 в нулевое состояние приводит к формированию на выходе элементам 12 импульсного сиг нала благодаря действию на выходе триггера 18 задержки в течение такта сигнала логической единицы предыдущего состояния триггера 7. В результате в регистр 3 сдвига через триггеры 17 и 19 задержки вместо дво ичного кода 0111 (семь) записывается двоичный код 1000 (восемь), соответствуюшзнй номеру текущего шага вычислений . Таким образом, двоичный код в регистре 5 сдвига на каждом шаге вычислений увеличивается- на единицу, и на выходе элемента И 12 формируется последовательный двоич-. ный код, соответствующий текущему но меру шага вычислений или текущему значению аргумента Xj.. На выходах триггеров 17 и 19 задержки формируются сдвинутые соответ ственно на такт и на два такта посл довательные двоичные коды текущего значения аргумента. Сумматор 6 формирует двоичный код величины 6хц 4x.+2xц. Сумматор 5 суммирует двоич ный код, сдвигаемьй под действием тактовых импульсов первого выхода блока 22 управления с выхода п-разрядного регистра 2 сдвига с величиной , а двоичный код результата согласно соотношению (1.2) записьша ется в регистр 2 сдвига. Так как ве личина Хб , формируемая в регистре 2 сдвига, является четной, то в млад шем разряде ее всегда содержится ну .левой код. Элемент ИЛИ 9 формирует двоичный код величины , так как в младший разряд двоичного кода сдвигаемого с выхода регистра 2 сдвига через элемент ИЛИ 9 поступает единичный сигнал третьего выхода блока 22 управления в первом такте на каждом шаге вычислений. Сумматор 4 суммирует последовательный двоичный код значения кубической функдии на предыдущем шаге вычислений, сдвигаемый под действием тактовых импульсов первого выхода блока 22 управления с выхода п-разрядного регистра 1 сдвига, с последовательным двоичным кодом величины 26, +1, поступающим с выхода элемента ИЛИ 9 через элемент И 14. Последовательный двоичный код текущего значения функции xj,, формируемый на выходе сумматора 4, сдвигается, начиная с младшего разряда, в регистр 1 сдвига под действием тактовых импульсов первого выхода блока 22 управления. Одновременно с формированием кубической функции вычислительное устройство реализует квадратичную функцию по соотношению (1.4) следующим образом. После пуска вычислительного устройства и установки триггера 8 в единичное состояние элемент И 26 подключает выход элемента ИЛИ 27 к второму входу сумматора 25. Б первом такте первого шага вычислений импульс первого разряда распределителя 33 импульсов поступает на третий выход блока 22 управления и через элементы ИЛИ 27, И 26 и сумматор 25 записывается в регистр 24 сдвига под действием такт.овьй импульсов первого выхода блока 22 управления. На втором и всех последующих шагах вычислений на выходе элемента ИЛИ 27 формируется последовательный двоичный код величины 2х, +1. С выхода регистра 3 сдвига под действием тактовых импульсов первого выхода блока 22 управления сдвигается, начиная с младших разрядов, последовательный двоичный код значения аргумента х на предыдущем k-1-м шаге вычислений, который задерживается на такт триггером 28 задержки и поступает на выход элемента ИЛИ 27. В младший разряд последовательного двоичного кода 2xj,,, , действующего на выходе триггера 28 задержки, записывается импульс, поступающий с третьего выхода блока 22 управления на выход элемента ШШ 27. II1 Сумматор 25 формирует последовательный двоичный код квадратичной функции на текущем шаге вычислений путем суммирования последовательного двоич ного кода значения квадратичной функ ции Xj,, на предыдущем шаге вычислений, сдвигаемого с вьгхода регистра 24 сдвига с последовательным двоичным кодом 2Х|,, +1, действующим на выходе элемента ИЛИ 27. Последовательный двоичный код значения квадра тичной функции X1 на текущем шаге вычислений сдвигается, начиная с младшего разряда, в регистр 24 сдвига под действием тактовых импульсов первого выхода блока 22 управления. Аналогично вычислительное устройство функционирует на всех последующих шагах вычислений до тех пор. пока текущее значение двоичного кода аргумента х, не примет за/данное значение х, установленное в блоке 20 задания аргумента. В этом случае срабатывает блок 21 сравнения последовательных п-1 разрядов кодов, который в п-1 такте текущего шага вычислений формирует на первом выходе сигнал логической единицы, открывающий элемент И 13, Импульсный сигнал последовательности, действующий на четвертом выходе блока 22 управления через элемент И 13 сбрасывает триггер 8 в нулевое состояние, в котором элементы И 14 - 16 и 26 блокируются нулевым сигналом прямого выхода триг гера 8. Двоичньй код требуемого значения аргумента фиксируется динамическим способом в цепи циркуляции регистра 3 сдвига через элемент ИЛИ 10, элемент И 12, триггеры 17 и 19 задержки, а двоичньш код результата возве дения в куб и квадрат фиксируется соответственно в цепи циркуляции ре гистра 1 сдвига через сумматор 4 и регистра 24 сдвига через сумматор 2 Во втором режиме устройство рабо тает аналогично, но в регистре 3 сдвига накапливается текущее значение функции Vx , в регистре 24 сдви га - функции Vx, а в регистре 1 сдвига - текущее значение аргумента Вычисление производят по алгоритму Ч у1-1..б, + 1 , 2l.6i-ZI6i+6U.,. /9 о Ы ( 05 t|K yVn2y,, + 1 (2.4) до тех пор, пока не будет достигнуто условие останова вычислений где АУ; 1 ; - значения функции на k-M и k-1-м шагах вычислений соответственно; - значения функции на k-M и k-1-м шагах вычислений соответственно. Устройство осуществляет указанное вычисление до тех пор, пока двоичный код текущего значения функции, возведенной в куб, у не сравнивается или не превышает заданного значения аргумента Х, установленного в блоке 20 задания аргумента. В этом случае на первом или втором выходе блока 21 сравнения формируется сигнал логической единицы, который открывает элемент И 13. Импульсный сигнал четвертого выхода блока 22 управления через элемент И 13 сбрасывает триггер 8 в нулевое состояние, в котором сигнал его прямого вьгхода блокирует элементы И 14 - 16 и 26. В случае равенства у Х имеем у, Ц, а в цепи циркуляции регистра 3 сдвига через элемент ИЛИ 10, элемент И 12, триггеры 17 и 19 задержки фиксируется последовательный двоичный код результата извлечения кубического корня из заданного значения аргумента Х, установленного в блоке 20 задания аргумента. Одновременно в цепи циркуляции регистра 24 сдвига через сумматор 25 фи1 сируется двоичный код функции у Цх. Разрядность п регистров 1 - 3 и 24 сдвига выбирается из условий требуемого диапазона представления аргумента и функции, максимальные значения которых не должны превышать величины -1. В каяздом шаге вычи лений последний п-й такт используется для возврата блока 21 сравнения в исходное состояние импульсами, действующими на втором выходе блока 22 управления. В третьем режиме вычислительное устройство работает аналогично второму режиму по алгоритму (2.1, 2.2, 2.3 и 2.4), но вычисления продолжаются до тех пор пока двоичный код текущего значения квадрата функции у, формируемый в регистре 24 сдвига, не сравняется или не превысит заданного значения аргумента х, установленного в блоке 20 задания аргумента В этом случае на первом или втором выходе блока 21 сравнения формируется сигнал логической единицы, который открывает элемент И 13. И тульсный сигнал четвертого выхода блока 22 управления через элемент И 13 сбрасывает триггер 8 в нулевое состояние. в котором сигнал егопрямого выхода блокирует элементы И14- 16 и 26. При равенстве у Х,,,имеем у,, --Jx и j ifу -J If Таким образом, в регистрах 3 и 24 сдвига фиксируются соответственно последовательные двоичные коды функций Чх и . Технико-экономическая эффективность изобретения по сравнению с известным устройством заключается в расширении функциональных возможностей путем получения допо тнительных функций х , -{ , и Чх наряду с и Ч . формированием функций х

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Устройство для вычисления экспоненциальной функции | 1982 |

|

SU1057944A2 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО по авт.св. № 1070545, о т л и ч а ющ е е с я тем, что, с целью расширения ег о функциональных возможностей путем вычисления функций вида х , -)7с, -тПГ и -{х в него введены четвертьй регистр сдвига, четвертый сумматор, шестой элемент И, четвертый элемент ШШ и четвертый триггер задержки, причем выход четвертого сумматора соединен с информационным .входом четвертого регистра сдвига и с третьим входом коммутатора устройства , второй выход коммутатора блока управления соединен с управляюпщм входом четвертого регистра сдвига, вход ввода данных которого подключен к нулевой шине устройства, выход генератора тактовых сигналов блока управления соединен с входами синхронизации четвертого регистра сдвига и четвертого триггера задержки, выход четвертого регистра подключен к первому входу четвертого сумматораi второй вход которого соединен с выходом шестого элемента И, первьй вход которого подключен к прямому выходу второго триггера, выход первого разряда распределителя импульсов блока управления соединен (Л с первым входом четвертого элемента ИЛИ, выход которого подключен к второму входу шестого элемента И, выход третьего регистра с цвига соединен с информационным входом четвертого триггера задержки, выход которого подключен к второму входу четвертого 4 4; элемента ИЛИ.

Фаг.1

tj;

л

Фаг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-03-07—Публикация

1983-06-10—Подача