сравнения и является первым входом задатчика данных, второй вход которого соединен с первым информационным входом блока сравнения, второй информационный вход которого соеди.нен с выходом элемента задержки, второй вход которого соединен с выходом элемента ИЛИ и первым входом первого элемента И, второй вход которого соединен с вхрдом третьегр коммутатора и прялаш выходом DF-триггера, D-вход которого подключен к первомувыходу первого коммутатора, второй выход которого является вторым выходбм задатчика данных, выход первого разряда распределителя импульсов соединен с первым выходом задатчика ; данных и входом сброса блока сравнений, выход которого соединен с первым входом второго элемента И, второй вхо

которого соединен с выходомл-го разряда распределителя импульсов, с информационным входом генератора одиночных импульсов и с F-входом DF-триггера, вход первого коммутатора соединен с выходом генератора одиночных импульсов, управлянмций вход которого соединен с выходом второго коммутатора, вход которого соединен с выходом элемента НЕ, вход которого заземлен, .выходы распределителя импульсов соединены с входами четвертого коммутатора, выходы которого соединен вы с входами элемента ИЛИ, выходы с третьего по седьмой задатчика данных соединены соответственно с вы ходом второго элемента И, первым,вторым, третьим выходами третьего коммутатора и вы ходом первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления экспоненциальной функции | 1982 |

|

SU1057944A2 |

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

| Вычислительное устройство | 1983 |

|

SU1144105A2 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

1.УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ПОЛИНОМА BTOPOtl СТЕПЕНИ, содержащее первый регистр сдвига, второй регистр сдвига, сумматор, первый элемент ИЛИ, второй элемент ИЛИ, элемент И, элемент задержки, триггер, причем выход первого регистра сдвига соединен с первым входом сумматора, выход которого -соединен с информационным входом первого регистра сдвига, выход второго регистра сдвига соединен с первым входом первого-элемента ИЛИ, второй вход которого соединен с выходом элемента задержки, вход которого соединен с прямым выходом триггера, вход сброса которого соединен с выходом второго регистра сдвига, инверсный выход триггера соединен с первым входом элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, а выход соедиHeiH с информационным входом второго регистра сдвига, выход которого соединен с первым входом второго э;1емента ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены третий регистр сдвига, второй сумматор, задатчик данных, второй триггер, второй элемент И, третий элемент И, генератор тактовых импульсов , причем выход генератора тактовых импульсов соединен с первым входом задатчика данных, второй вход которого соединен с выходом первого элемента И, первый выход задатчика данных соединен с первым входом второго элемента И, второй вход.которого соединен с прямым выходом второго триггера и первым входом третьего элемента И, второй вход которого соединен с выходом второго сумматора, первый вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с информационным входом первого триггера и выходом второго элемента И, второй выход задатчика данных соединен с информационньм входом второго триггера, вход сброса которого соединен с третьим i выходом эадатчика данных,: четвертый выход которого ..соединен с входом за(Л пуска первого регистра сдвига, вход синхронизации которого соединен с входом синхронизации второго и третье го регистров сдвига, входом синхронизации элемента задержки и выходом генератора тактовых импульсов, пятый и шестой Выходы эада.тчика данных соединены соответственно с входами запуска второго и третьего регистров сдвига, выход третьего регистра сдвига соедиьэ нен с вторым входом второго сумматора, и со своим инфо1 «ационнымвходом,седьл мой выход задатчика данных соединен с входами ввода дав{шх первого, вто- рого и етьего регистров сдвига, выход третьего элемента И соединен с вторым входом первого сумматора. 2. Устройство по п. 1, о т л и ч аю щ е е с я тем, что задатчик данных содержит DF-триггер, распределитель импульсов, элемент задержки, элемент ИЛИ, блок сравнения, генератор одиночных импульсов, элемент НЕ, первый и второй элементы И, первый, второй, третий и четвертый коммутаторы, причем вход распределителя импульсов соединен с первым входом элемента задержки, с управляющим входом блока

- - Изобретение относится к автомати ке и вычислительной технике и предназначено для вычисления полинома второй степени. Известен квадратор, содержсцций д счетчика, блок умножения, сумматор, два элемента задержки и элемент ИЛИ Недостаток такого квадратора закл чается в ограниченных функциональных возможностях, которые не позволяют формировать полином второй степени. Наиболее близким техническим решением к предлагаемому является квад ратор, содержащий первый регистр сдв га, второй регистр сдвига, сумматор первый элемент ИЛИ, второй элемент ИЛИ, элемент И, элемент задержки, триггер, причем выход первого реги стра сдвига соединен с первым входом сумматора, выход которого соеди нен с информационным входом первого регистра сдвига, выход второго регистра сдвига соединен с первым входом первого элемента ИЛИ, второй вход ко торого соединен с выходом элемента задержки, вход которого соединен с прямьви выходом триггера, вход сброса которого соединен с выходом второго регистра сдвига, инверсный выход триггера соединен с первык; входом элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, а выход соединен с информационным входом второго perHctpa сдвига выход которого соединен с первым вхо дом второго элемента ИЛИ t Недостаток устройства заключается в ограниченных , функциональных возмож ностях, которые не позволяют формировать полином второй степени. Цель изобретения - расширение функ циональных возможностей. Поставленная цель достигается тем, что в устройство введены третий регистр сдвига, второй сумматор, задат чик данных, второй триггер, второй элемент И, третий элемент И, генера-, тор тактовых импульсов, причем выход генератора тактовых импульсов, соединен с первым входом задатчика данных, второй вхрд которого срединен с выходом первpro зле мента И, первый выход задатчика данных соединен с первым входом второго элемента И, второй вход которого срединен с прямым выходом второго триггера и п.ервым входом третьего элемен- та И, второй вход которого срединен с выхрдом второго сумматора, первый вход котррргр срединен с выхрдрм втрррго элемента ИЛИ, вторбй вход которого срединен с инфррмацирнным, вхрдрм первргр триггера и НЫХРДРМ втррргр элемента И, втрррй выхрд задатчика данных соединен с информационным входом второго триггера,г вход сброса которого соединен с третьим выходом задатчика данных, четвертый выход которого соединен с входом запуска пер- ; вого регистра сдвига, вход синхронизации которого соединен с входом синхронизации второго и третьего регистров сдвига, ВХРДРМ синхррнизации элемента задержки и ВЫХРДРМ генератора тактовых импульсов, пятый и шестой выходы задатчика данных соединенысо-, тветственно с входами запуска второго

и третьего регистров сдвига, выход третьего регистра сдвига соединен-с вторым входом второго сумматора и со своим информационна входом, седьмой выход задатчика данных соединен с входами ввода данных первого, второг и третьего регистров сдвига, выход третьего элемента И соединен с вторым входом первого сумматора.

Задатчик данных содержит DF-трйггер, распределитель импульсов, элеме задержки, элемент ИЛИ, блок сравнени генератор одиночных импульсов, элемент НЕ, первый и второй элементы И, первый, второй, третий и четвертый коммутатоЕи, причем вход распределителя импульсов соединен с первым входом элемента задержки, с управляю щим входом блока сравнения и является первьш входом эадатчика данных, второй вход которого соединен с первым информационньом входом блока сравнения, второй информационный вход которого соединен с выходом элемента задержки, второй вход которого соеди нен с выходом элемента ИЛИ и первым входом первого элемента И, второй вход которого соединен с входом третьего коммутатора и первым выходом ВРчтриггера, D-вход которого подключ к первому выходу первого коммутатора второй выход которого является вторым выходом задатчика данных, выход первого разряда распределителя импульсов соединен с первым выходом задатчика данных и входсж сброса бло ка сравнения, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом п-го разряда распределителя импульсоЁ, с информационньал входом генератора одиночных импульсов и с F-входом DF-триггера, вход первого KOMMyTaxopji -соединен с выходом генератора одиночных импульсов, управляющий вход которого соединен с выходом второго коммутатора, вход которого соединен с выходом элемента НЕ, вход которого заземлен, выходы распрделителя импульсов соединены с входами четвертого коммутатора, выходы ко.торого соединены с входами элемента ИЛИ, выходы с третьего по седьмой задатчика данных соединены соответственно с выходом второго элемента И, первым, втором/ третьим выходами третьего коквдутатора и выходом перч вого элемента И.

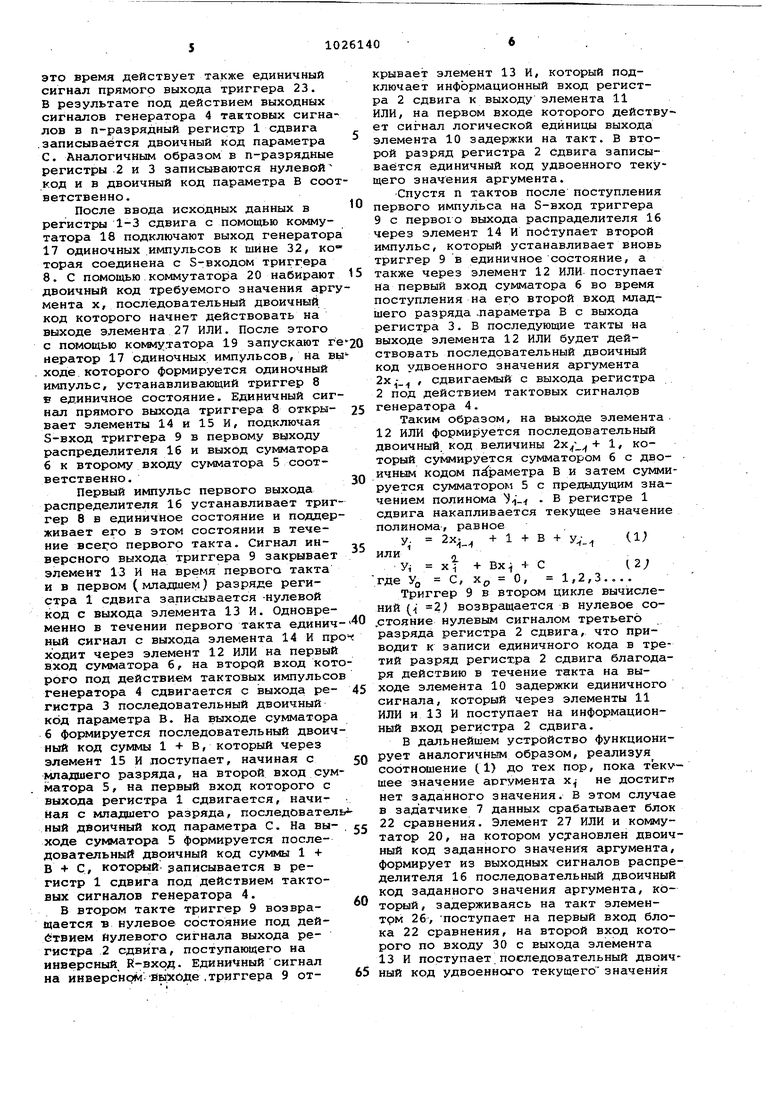

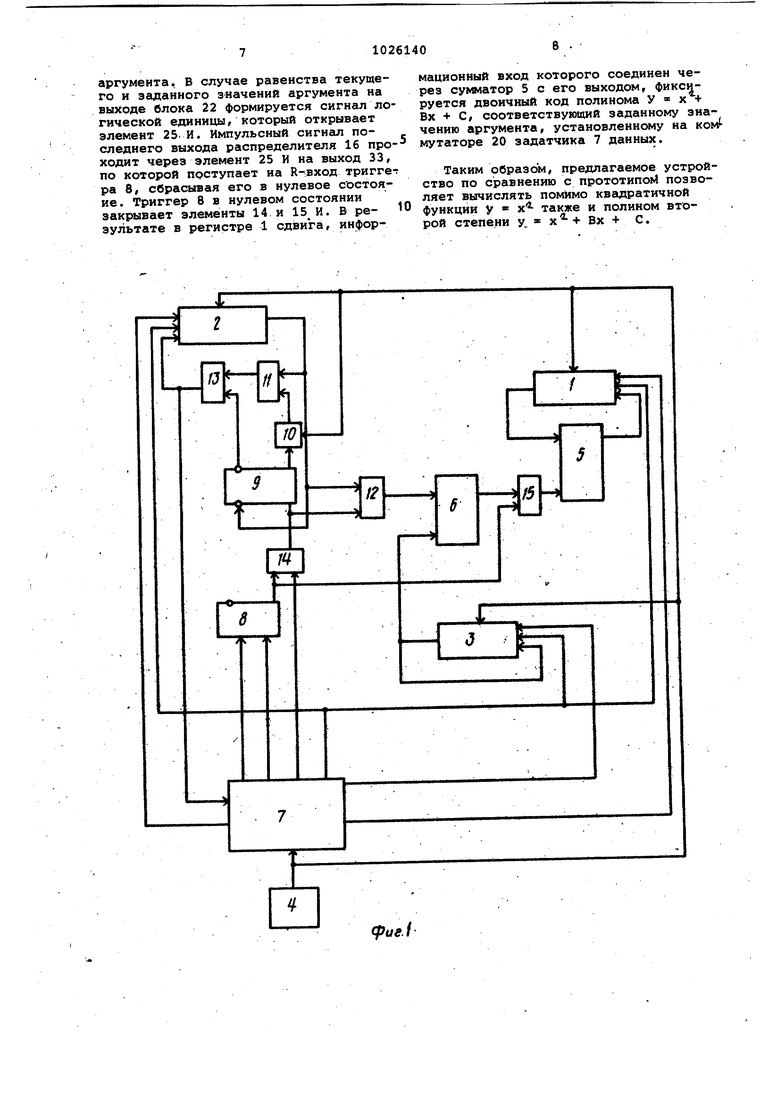

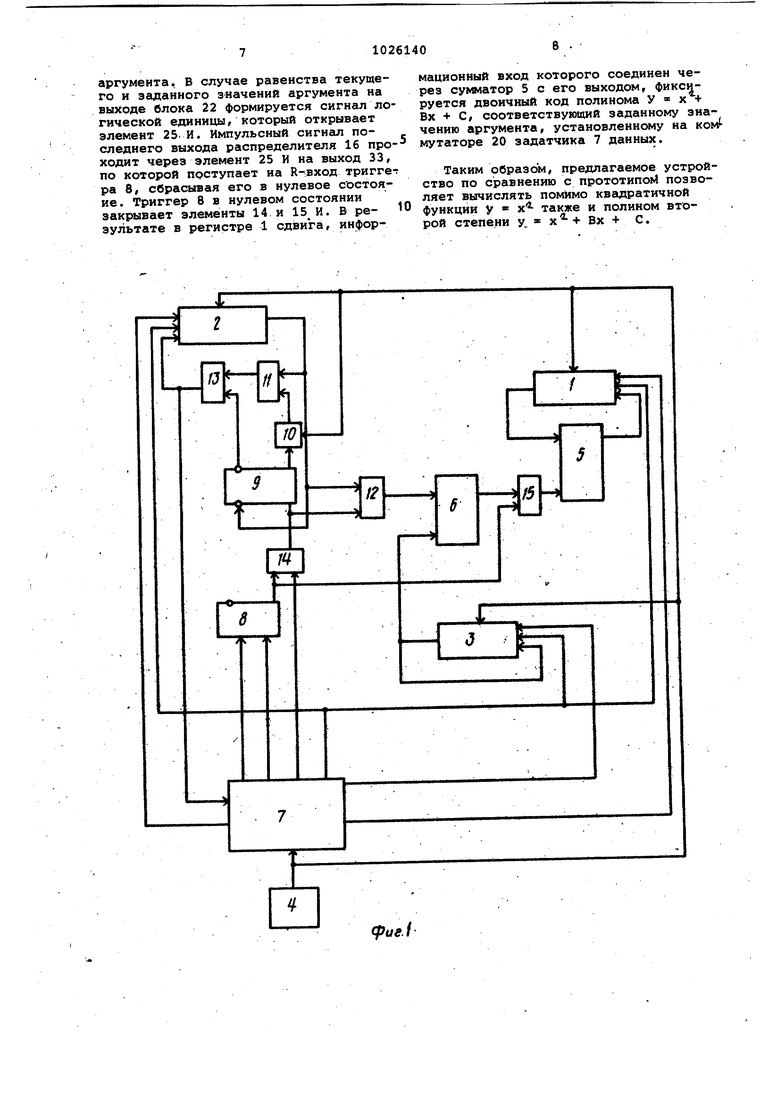

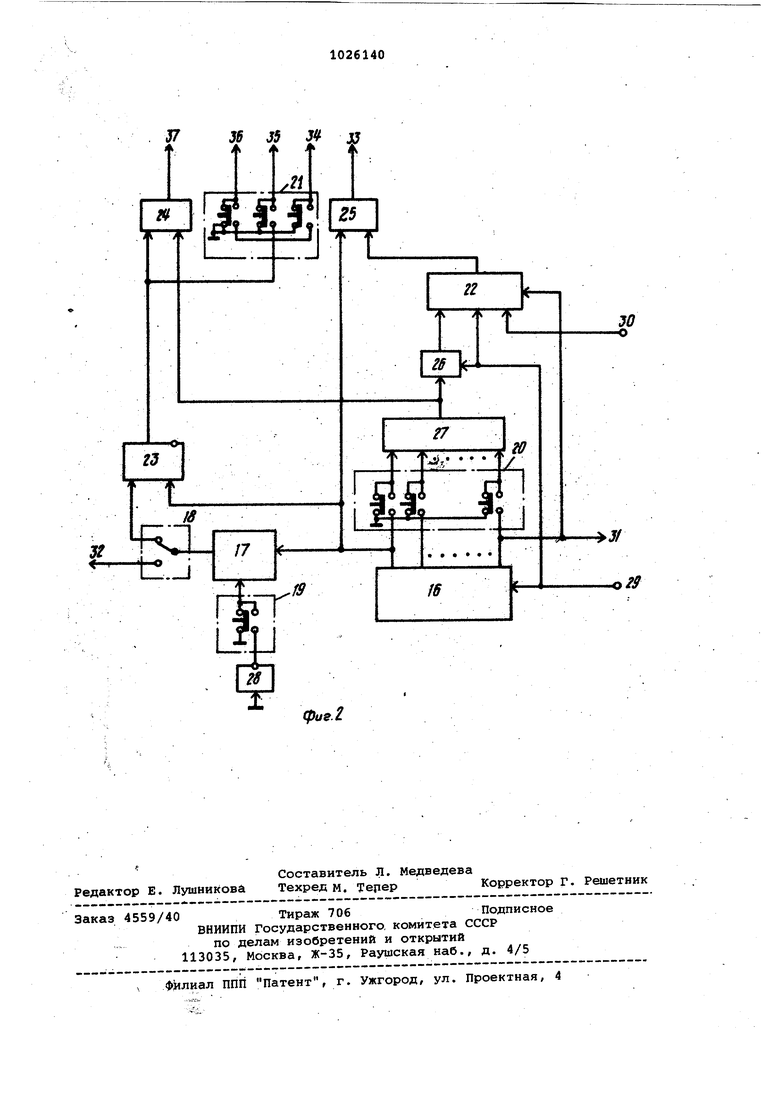

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - структурная схема задатчика данных.

Устройство содержит регист1кл 1-3 сдвига, генератор 4 тактовых сигналов , сумматоры 5 и б, задатчик 7 данных, RS-триггер 8, 5- трИ1гер 9, элемент 10 задержки, элементы 11 и 12 ИЛИ, элементы 13-15 И.

Задатчик 7 данных (фиг. 2) содержит распределитель 16 импульсов, генратор 17 одиночных импульсов, коммутаторы 18-21, блок 22 сравнения, DF-триггер 23, элементы 24 и 25 И, элемент 26 задержки, элемент 27 ИЛИ, элемент 28 НЕ, входы 29 и 30 и семь выходов 31-37.

В устройстве количество п регистров 1-3 сдвига выбирается из условия 2, где m определяет максимально допустимое значение 2 аргумента и параметров В и С.

Устройство вычисляет полином второй степени у Вх + с и работает следующим образом.

В исходном состоянии в регистр 1 сдвига записывается двоичный код параметра С, регистр 2 сдвига находится в нулевом состоянии, а в регистр 3 сдвига записывается параметр В. Триггеры 8 и 9 находятся в нулевом состоянии.

Запись информации в регистрь 1-3 сдвига выполняется с помощью задатчи ка 7 данных следующим образен,

В режиме ввода исходных данных коммутатором 18 подключают выход генратора 17 одиночных импульсов к D-BXOду триггера 23. Коммутатором 21 выбирают один КЗ.регистров 1-3 сдвига. Например, выбор регист ра 1 сдвига обеспечивается подключением через коммутатор 21 и выход 34 прямого выхода триггера 23 к входу записи регистра 1 сдвига. Из сигналов генератора 4 т-ктовых сигналов распределитель 16 формирует на п выходах п последовательностей импульсов длител ностью t , периодом Т п-1Х и сдвинутых друг относительно друга на время где f - частота тактовых сигналов. С помощью коммутатора 20 набирают требуекалй двоичный код, например, параметра С. Коммутатор 20 подключает в единичных разрядах соответствующий выход распределителя 16 к входу элемента 27 ИЛИ, на выходе которого формируется последовательный двоичный код. Затем коммутаторы 19 подают с выхода элемента 28 НЕ сигнал логической единицы, не запускающий вход генератора 17, который пропускает на выход один импульс выхода распределителя 16. Выходной импульс генератора 17 через коммутатор 18 устанавливает триггер 23 в единичное состояние, в котором он находится п тактов и сбрасывается в нулевое состояние после окочания следующего импульса на п-м выходе распределителя 16. Единичный сигнал прямого выхода триггера 23 открывает элемент 24 И,через который последовательный п-разрядный двоичны :код параметра С поступает по выходу 37 на вход ввода данных регистра 1 сдвига, на входе записи которого в это время действует также единичный сигнал прямого выхода триггера 23. В результате под действием выходных сигналов генератора 4 тактовых сигна лов в п-разрядный регистр 1 сдвига .записывается двоичный код параметра С. Аналогичным образом в п-разрядные регистры 2 и 3 записываются нулевой код и в двоичный код параметра В соо ветственно. После ввода исходных данных в регистры 1-3 сдвига с помощью коммутатора 18 подключают выход генератор 17 одиночных .импульсов к шине 32, ко торая соединена с S-входом триггера 8. С помощью коммутатора 20 набирают двоичный код требуемого значения арг мента X, последовательный двоичный код которого начнет действовать на выходе элемента 27 ИЛИ, После этого с помощью коидалутатора 19 запускают г нератор 17 одиночных импульсов, на в ходе которого формируется одиночный импульс, устанавливающий триггер 8 в единичное состояние. Единичный сиг нал прямого выхода триггера 8 открывает элементы 14 и 15 И, подключая S-вход триггера 9 в первому выходу распределителя 16 и выход сумматора 6 к второму входу сумматора 5 соответственно. Первый импульс первого выхода распределителя 16 устанавливает триг гер 8 в единичное состояние и поддер живает его в этом состоянии в течение BceijO первого такта. Сигнгш инверсного выхода триггера 9 закрывает элемент 13 И на время первого такта и в первом (младшем) разряде регистра 1 сдвига записывается -нулевой код с выхода элемента 13 И. Одновременно в течении первого такта единич ный сигнал с выхода элемента 14 И пр ходит через элемент 12 ИЛИ на первый вход сумматора 6, на второй вход кот рого под действием тактовых импульсо генератора 4 сдвигается с выхода регистра 3 последовательный двоичный код параметра В. На выходе сумматора б формируется последовательный двоич ный код суммы 1 + В, который через элемент 15 И поступает, начиная с младшего разряда, на второй вход сум матора 5, на первый вход которого с выхода регистра 1 сдвигается, начиная с младшего разряда, последовател ный двоичный код параметра С. На выходе cyNwaTopa 5 формируется последовательный двоичный код суммы 1 + В С, который записывается в регистр 1 сдвига под действием тактовых сигналов генератора 4. В втором такте триггер 9 возвращается в нулевое состояние под дейбтвием Нулевого сигнала выхода регистра 2 сдвига, поступающего на инверсный К-вход. Единичный сигнал на инверснр Выходе .триггера 9 открывает элемент 13 И, который подключает информационный вход регистра 2 сдвига к выходу элемента 11 ИЛИ, на первом входе которого действует сигнал логической единицы выхода элемента 10 задержки на такт. В второй разряд регистра 2 Сдвига записывается единичный код удвоенного текущего значения аргумента. Спустя п тактов после поступления первого импульса на S-вход триггера 9 с первою выхода распраделителя 16 через элемент 14 И поступает второй импульс, который устанавливает вновь триггер 9 в единичное состояние, а также через элемент 12 ИЛИ поступает на первый вход сумматора 6 во время поступления на его второй вход младшего разряда .параметра В с выхода регистра 3. В последующие такты на выходе элемента 12 ИЛИ будет действовать последовательный двоичный код удвоенного значения аргумента , сдвигаемый с выхода регистра 2 под действием тактовых сигналов генератора 4. Таким образом, на выходе элемента 12 ИЛИ формируется последовательный двоичный, код величины + 1, который суммируется сумматором 6 с двоичным кодом параметра В и затем суммируется сумматором 5 с предыдущим значением полинома V-)- . В регистре 1 сдвига накапливается текущее значение полинома, равное 2х, + 1 + В + у Vi X t + Вх + с {2} где УО С, Хр О, 1,2,3 Триггер 9 в втором цикле вычислений (-1 2) возвращается в нулевое со.стояние нулевым сигналом третьего разряда регистра 2 сдвига, что приводит к записи единичного кода в третий разряд регистра 2 сдвига благодаря действию в течение такта на выходе элемента 10 задержки единичного сигнала, который через элементы 11 ИЛИ и 13 И поступает на информационный вход регистра 2 сдвига. В дальнейшем устройство функционирует аналогичным образом, реализуя соотношение (1) до тех пор, пока текущее значение аргумента х не достигя нет заданного значения. В этом случае в задатчике 7 данных срабатывает блок 22 сравнения. Элемент 27 ИЛИ и коммутатор 20, на котором усз ановлен двоичный код заданного значения аргумента, формирует из выходных сигналов распределителя 16 последовательный двоичный код заданного значения аргумента, который, задерживаясь на такт элементрм 26, поступает на первый вход блока 22 сравнения, на второй вход которого по входу ЗО с выхода элемента 13 И поступает последовательный двоичный код удвоенного текущегозначения

аргумента. В случае равенства текущего и заданного значеннй аргумента на выходе блока 22 формируется сигнал логической единнцы, который открывает элемент 25. И. Импульсный снгнал последнего выхода распределителя 16 проходит через элемент 25 И на выход 33, по которой поступает на К-даход триггера 8| сбрасывая его в нулевое сюстояие. Триггер 8 в нулевом состоянии закрывает элементы 14 и . В результате в регистре 1 сдвига, инфор0

ю

мационный вход которого соединен через сумматор 5 с его выходом, фиксируется двоичный код полинома У х + Вх С, соответствую1ций заданному значению аргумента, установленному на KoWмутаторе 20 задатчика 7 данных.

Таким образом, предлагаемое устройство по сравнению с прототипом позволяет вычислять помимо квадратичной функции у также и полином второй степени у х + Вх + С.

/5

Wfpue.l

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для возведения в квадрат | 1976 |

|

SU615475A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Квадратор | 1979 |

|

SU826345A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-30—Публикация

1982-03-24—Подача