I12

Изобретение относится к цифровой вычислительной технике и может быть исподьзовано для проверки исправности цифровьсх устройств.

Цель изобретения - повышение на- дежности за счет обеспечения бесконтактной перестройки устройства для контроля произвольных логических элементов,

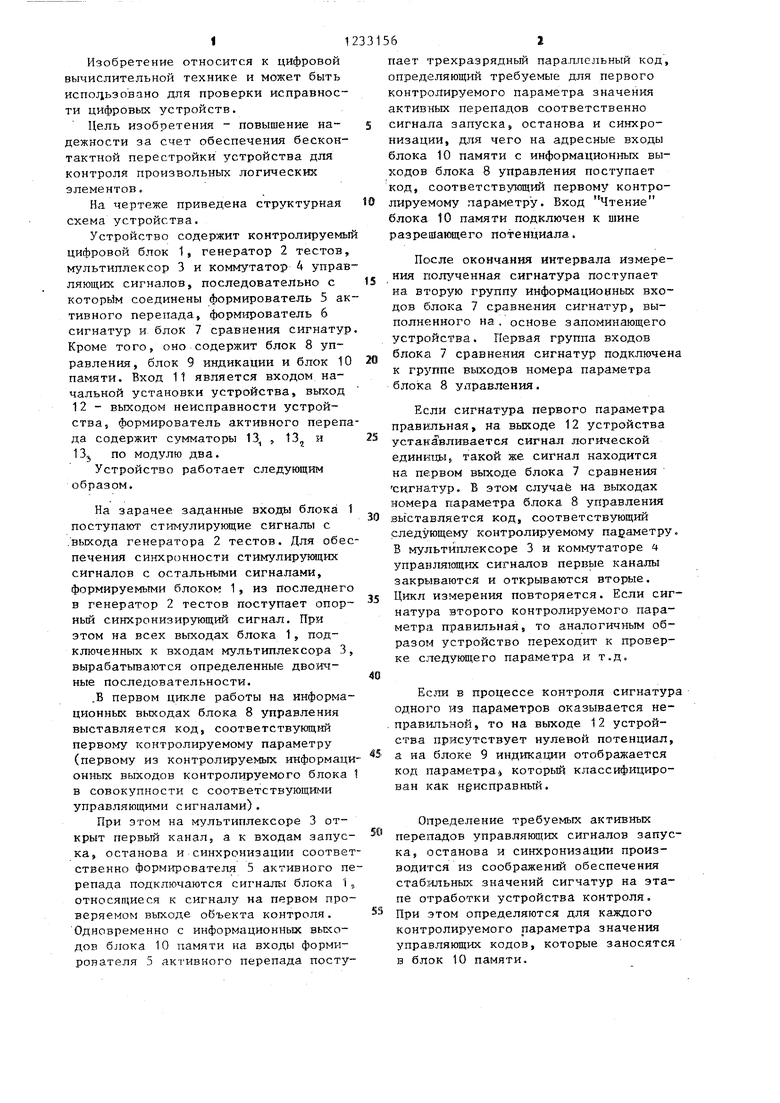

На чертеже приведена структурная схема устройства.

Устройство содержит контролируемый цифровой блок 1, генератор 2 тестов, мультиплексор 3 и коммутатор А управляющих сигналов, последовательно с KOTopblM соединены формирователь 5 активного перепада, форм:нрователь 6 сигнатур и блок 7 сравнения сигнатур. Кроме того, оно содержит блок 8 уп равления, блок 9 индикации и блок 10 памяти. Вход 11 является входом начальной установки устройства, выход 12 - выходом неисправности устройства, формирователь активного перепада содержит сумматоры 13, , 13 и 13,, по модулю два.

Устройство работает следующим образам.

На заранее заданные входы блока 1 поступают стимулирующие сигналы с . выхода генератора 2 тестов. Для обеспечения синхронности стимулирующих сигналов с остальными сигналами, формируемыми блоком 1, из последнего в генератор 2 тестов поступает опор- ньй синхронизирующий сигнал. При этом на всех выходах блока 1, подключенных к входам мультиплексора 3, вырабатьшаются определенные дво:ич- ные последовательности.

.В первом цикле работы на информационных выходах блока 8 управления выставляется код, соответствующий первому контролируемому параметру (первому из контролируемых информационных выходов контролируемого блока 1 в совокупности с соответствующими управляющими сигналами).

При этом на мультиплексоре 3 открыт первьй канал, а к входам запуска, останова и синхронизации соответственно формирователя 5 активного перепада подключаются сигналь. блока 1 относящиеся к сигналу на первом проверяемом выходе объекта контроля. Одновременно с информационных выходов блока 10 памяти на входы формирователя 5 активного перепада посту

5 0 5

0

5

0

5

3

562

пает трехразрядный параллельный код, определяющий требуемые для первого контролируемого параметра значения активных перепадов соответственно сигнала запуска, останова и синхронизации, для чего на адресные входы блока 10 памяти с информационных выходов блока 8 управления поступает код, соответствующий первому контролируемому параметру. Вход Чтение блока 10 памяти подключен к шине разрешающего потенциала.

После окончания интервала измерения полз ченная сигнатура поступает на вторз ю группу информационных входов блока 7 сравнения сигнатур, выполненного на . основе запоминающего устройства. Первая группа входов блока 7 сравнения сигнатур подключена к группе выходов номера параметра блока 8 управления.

Если сигнатура первого параметра правильная, на. вьпсоде 12 устройства устана вливается сигнал логической единицы, такой же сигнал находится на первом выходе блока 7 сравнения сигнатур. В этом случае на выходах номера параметра блока 8 управления выставляется код, соответствующий следующему контролируемому паеаметру. В мультиплексоре 3 и коммутаторе 4 управляющих сигналов первые каналы закрываются и открываются вторые. Цикл измерения повторяется. Если сигнатура второго контролируемого параметра правильная, то аналогичным образом устройство переходит к проверке следующ;его параметра и т.д.

Если в процессе контроля сигнатура одного из параметров оказывается не- . правильной, то на выходе 12 устройства присутствует нулевой потенциал, а на блоке 9 индикации отображается код параметра, который классифицирован как н@исправньтй.

Определение требуемых активных перепадов управляющих сигналов запуска, останова и синхронизации производится из соображений обеспечения стабильных значений сигнатур на этапе отработки устройства контроля, При этом определяются для каждого контролируемого параметра значения управляющих кодов, которые заносятся в блок 10 памяти.

3.1

Формула изобретения

1. Устройство для контроля цифровых блоков, содержащее генератор тестов, мультиплексор, формирователь сиг- натур, коммутатор управлянвдих. сигналов блок сравнения сигнатур, блок управления и блок индикации, причем группа выходов номера параметра блока управления соединена с группами управлякяцих входов мультиплексора и коммутатора управляющих сигналов, группой входов блока индикации и первой группой информационных входов блока сравнения сигнатур, вход начальной установки устройства соединен с установочными входами формирователя сигнатур,блока сравнения сигнатур и блока управления , группа информационных выходов и синхровход генератора тестов соеди- нены соответственно с группой информационных входов и синхровходом контролируемого цифрового блока, группа информационных выходов которого соединена с группой информационных входов мультиплексора, выход которого соединен с информационным входом формирователя сигнатур, выходы Пуск,

Стоп и Синхро контролируемого цифрового блока соединены с соответ- ствующими.информационными входами коммутатора управляющих сигналов, группа информационных выходов и выход стробирования формирователя сигнатур соединень соответственно с второй группой информационных входов и вхо1564

дом стробирования блока сравнения сигнатур, первьш информационный выход которого соединен со счетным входом блока управления, а второй информационный выход является выходом неисправности устройства, о т- личающееся тем, что, с

целью повышения надежности за счет обеспечения бесконтактной перестройки устройства для контроля произвольных логических элементов, оно содержит формирователь активного перепада и блок памяти, причем выходы Пуск, Стоп, и Синхро ко1Ф1утатора impas- лякщнх сигналов через формирователь активного перепада соединены с одноименными входами формирователя сигнатур, группа управляющих входов формирователя активного перепада соединена с группой информационных выходов блока памяти, группа адресных входов которого соединена с группой выходов номера параметра блока управления, а вход Чтение блока памяти соединен с шиной разрешакщего потенциала устройства.

2. Устройство по п. 1, отличающееся тем, что формирователь активного перепада содержит три сумматора по модулю два, причем первые и вторые йходы сумматоров по модулю два являются соответственно группами информационных и управляющих входов формирователя, а выход - группой выходов формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1264186A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Устройство для контроля радиоэлектронных блоков | 1987 |

|

SU1531100A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Сигнатурный анализатор | 1986 |

|

SU1383360A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для проверки исправности цифровых устройств с использованием принципов сигнатурного анализа. Целью изобретения является повышение надежности за счет обеспечения бесконтактной перестройки устройства для контроля произвольных логических элементов. Устройство содержит генератор тестов, мультиплексор,коммутатор управлякицих сигналов, формирователь активного перепада, формирователь сигнатур и блок сравнения сигнатур. Кроме того, устройство содержит блок управления, блок индикации и блок памяти. Отличительной особенностью устройства является наличие совокупности формирователя активного перепада и блока памяти, что позволяет осуществлять бесконтактную коммутацию определенным образом выбранных активных перепадов управляющих сигналов произвольных контролируемых блоков по сигналам из блока памяти. 1 з.п. ф-лы, 1 ил.

Редактор Н. Рбгулич

Составитель С, Старчия:ин

Техред О.Сопко ; Корректоре. Шекмар

Заказ 2772/51

Tnpaxfc 671

БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035 Москва, Ж-35, Раугаслсая наб., д. 4/5

Произволс.твенно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Подписное

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1984-07-25—Подача