Изобретение относится к вычислительной технике и может быть использовано при создании автоматических систем контроля цифровых и аналоговых сигналов сложных радиоэлектронных объектов.

Цель изобретения - расширение области применения и повышение достоверности контроля за счет обеспечения проверки амплитуд переменных, а также квантованных и не квантованных по времени импульсных сигналов (аналоговых напряхсений).

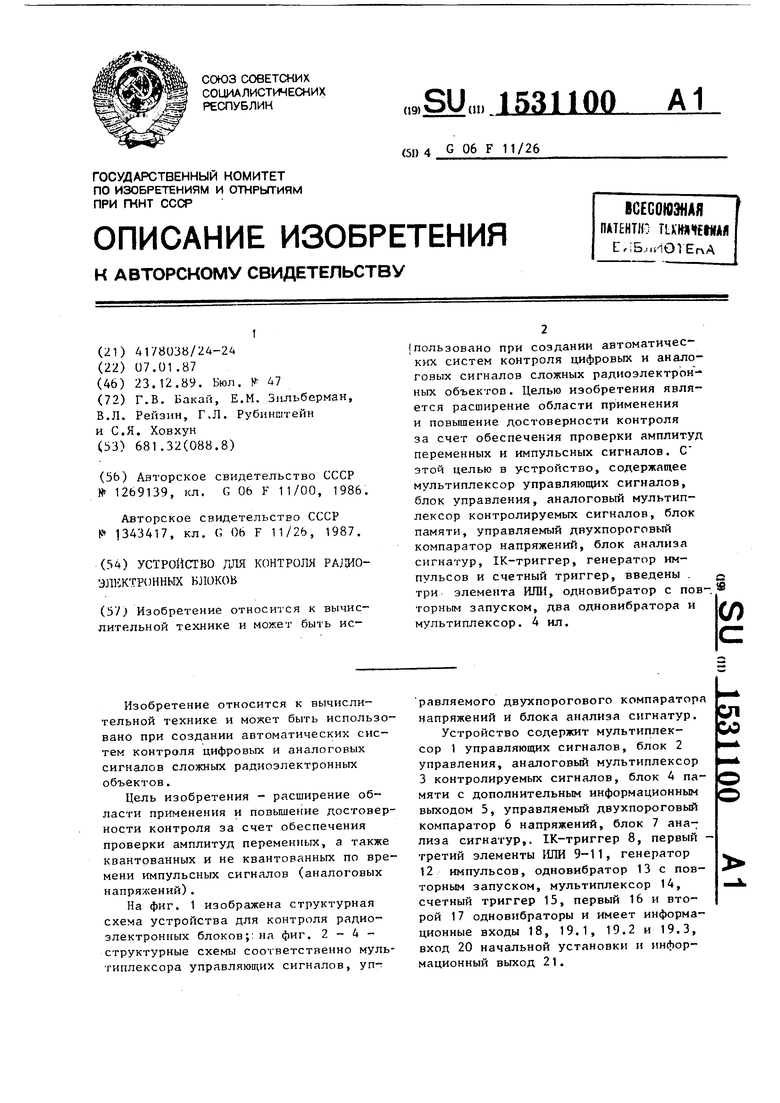

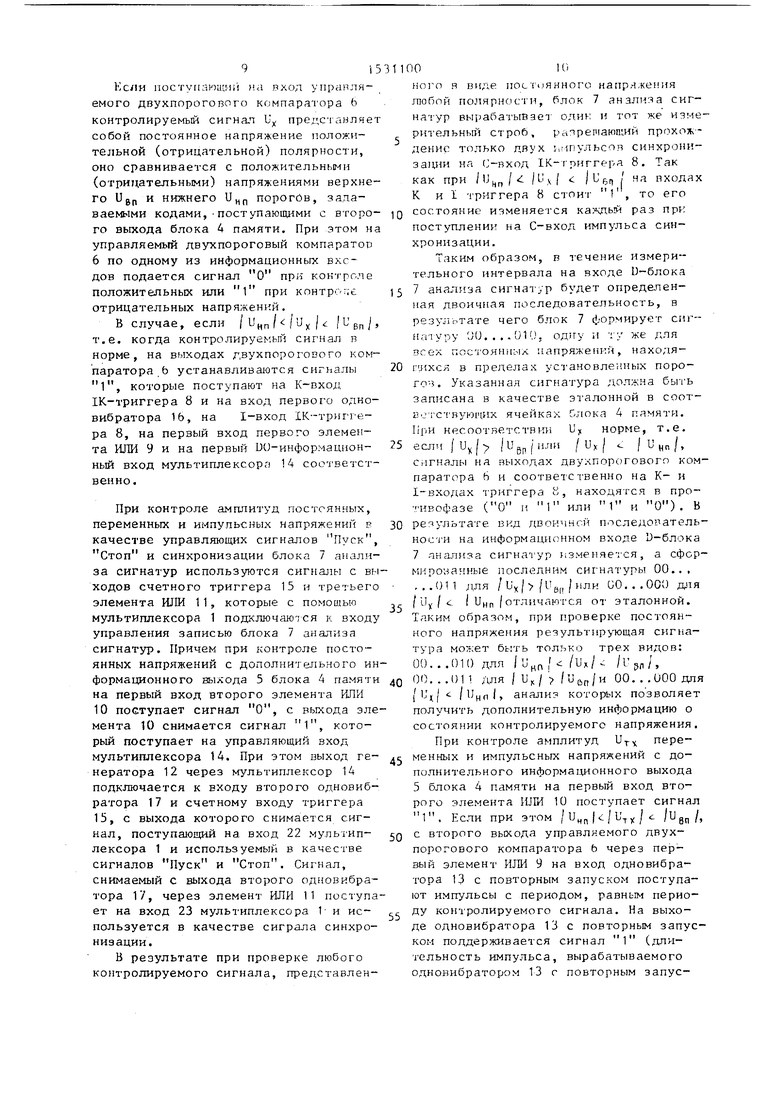

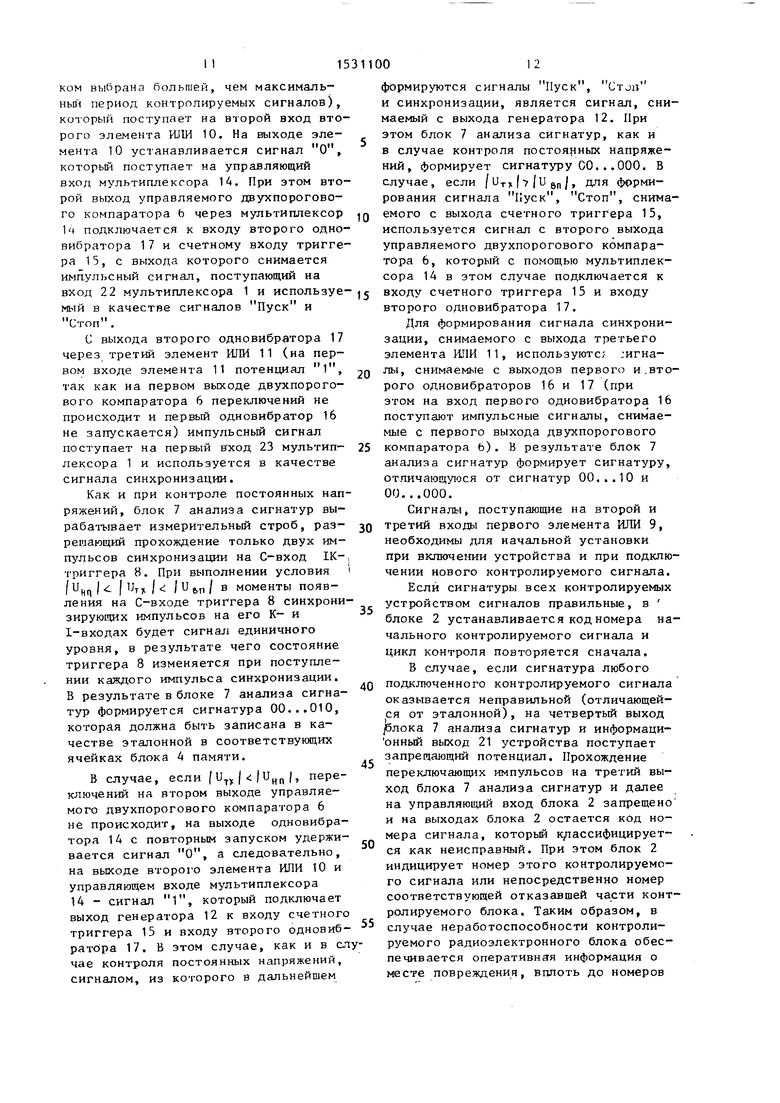

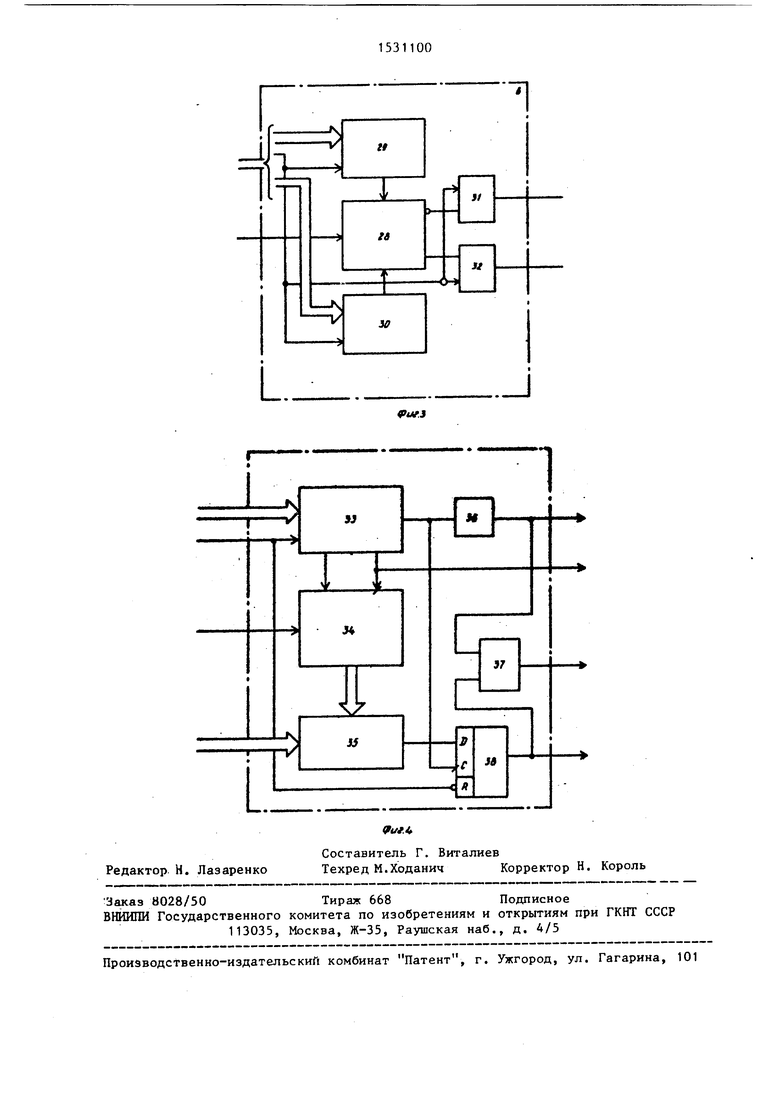

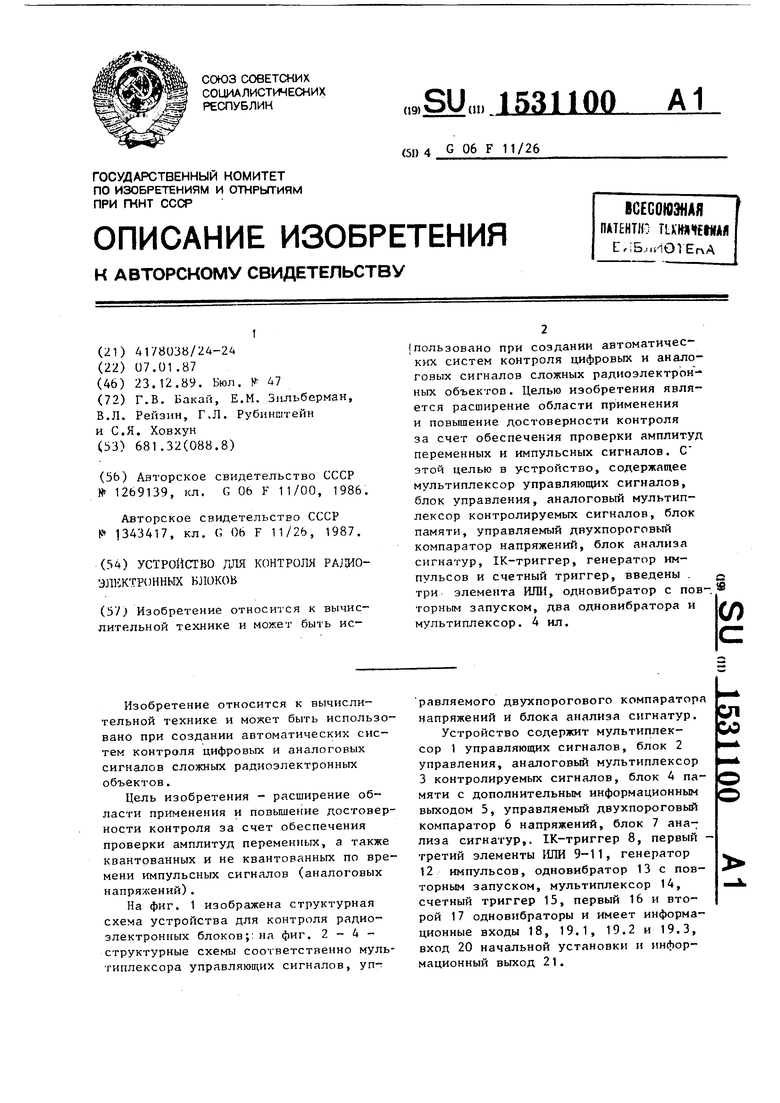

На фиг. 1 изображена структурная схема устройства для контроля радио- злектронных блоков;: на фиг. 2 - 4 - структурные схемы соответственно мультиплексора управляющих сигналов, уп-:

равляемого двухпорогового компаратора напряжений и блока анализа сигнатур.

Устройство содержит мультиплексор 1 управляюпщх сигналов, блок 2 управления, аналоговый мультиплексор 3 контролируемых сигналов, блок 4 памяти с дополнительным информационным выходом 5, управляемый двухпороговый компаратор 6 напряжений, блок 7 анализа сигнатур,. 1К-триггер 8, первый - третий элементы ИЛИ 9-11, генератор 12 импульсов, одновибратор 13 с повторным запуском, мультиплексор 14, счетный триггер 15, первый 16 и второй 17 одновибраторы и Имеет информационные входы 18, 19.1, 19.2 и 19.3, вход 20 начальной установки и информационный выход 21.

Информационные входы 18, 19.1-19.3 подключены соответ ственно к информационным входам п-канального аналогового мультиплексора 3 контролируемых сигналов и инфоргмационным входам мультиплексора 1 управлякицих сигналов. Выходы блока 2 подключены к управляющим входам аналогового мультиплексора 3 и адресному входу блока 4 - памяти, первый - третий информационные выходы которого соединены с адрес ным входом мультиплексора 1, информационным входом управляемого двухпоро- гового компаратора 6 напряжений и пер вым информационным входом блока 7 анализа сигнатур. Выход мультиплексора 1 соединен с входом управления записью блока 7 анализа сигнатур, первый - четвертый информационные выхог ды которого подключены соответственно к С-входу 1К-триггера 8, второму R-входу 1К-триггера 8, второму входу первого элемента ИЛИ 9, управляющему входу блока 2 и информационному выходу 21 устройства. Выход аналогового мультиплексора 3 подключен к входу компаратора 6 напряжений, первый выход которого соединен с К-вхо- дом 1К-триггера В и входом первого одновибратора 16, второй выход - с 1-входом 1К-триггера 8, первым (DO) информационным входом мультиплексора 1А и первьм входом первого элемента ИЛИ 9. Выход 1К-триггера 8 соединен с входом D блока 7 анализа сигнатур. Дополнительный информационный выход 5 блока 4 памяти подключен к первому входу второго элемента ИЛИ 10, выход которого соединен с управляющим вхогг дом мультиплексора 14. Выход первого элемента ИЛИ 9 подключен к входу одновибратора 13 с повторным запуском, выход которого соединен с вторым входом второго элемента ИЛИ 10. Выход .генератора 12 соединен с вторым (DI) информационным входом мультиплексора- 14, выход которого подключен к входу счетного триггера 15 и входу второго одновибратора 17. Выход счетного тригера 15 подключен к первому управляющему входу 22 мультиплексора 1. Выг ходы первого 16 и второго 17 одновиб раторов подключены соответственно к первому и второму входам третьего элемента ИЛИ 11, выход которого соединен с вторым управляющим входом 23 мультиплексора 1. Вход 20 начальной установки устройства соединен с одноименными входами блока 2 и блока 7 анализа сигнатур, третьим входом первого элемента ИЛИ 9 и первым R-входом

5 1К-триггера 8.

На фиг. 1 изображен также генератор 24 тестов, стимул-выходы и син- хровход которого соединены соответственно со стимул-входами и синхровыхо10 дом контролируемого блока, информационные зыходы кэторого подключены к информационным входам 18, 19.1, 19.2 и 19.3 устройства, которые соединены соответственно с информационными вхо- J5 дами аналогового мультиплексора 3 и информационными входами мультиплексора 1.

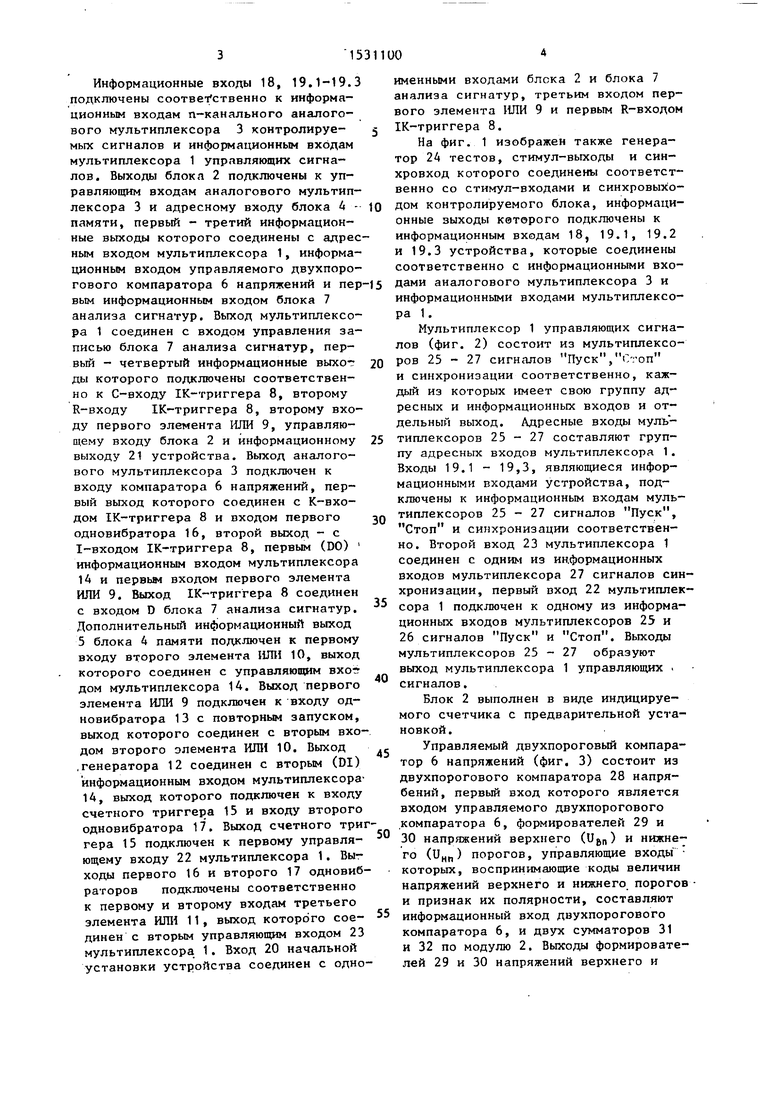

Мультиплексор 1 управляющих сигналов (фиг. 2) состоит из мультиплексо20 ров 25 - 27 сигналов Пуск,Стоп и синхронизации соответственно, каждый из которых имеет свою группу адресных и информационных входов и отдельный выход. Адресные входы муль25 типлексоров 25 - 27 составляют группу адресных входов мультиплексора 1. Входы 19.1 - 19,3, являющиеся информационными входами устройства, подключены к информационным входам мультиплексоров 25 - 27 сигналов Пуск, Стоп и синхронизации соответственно. Второй вход 23 мультиплексора 1 соединен с одним из информационных входов мультиплексора 27 сигналов синхронизации, первый вход 22 мультиплексора 1 подключен к одному из информационных входов мультиплексоров 25 и 26 сигналов Пуск и Стоп. Выходы мультиплексоров 25 - 27 образуют выход мультиплексора 1 управляющих . сигналов.

Блок 2 выполнен в виде индицируемого счетчика с предварительной установкой.

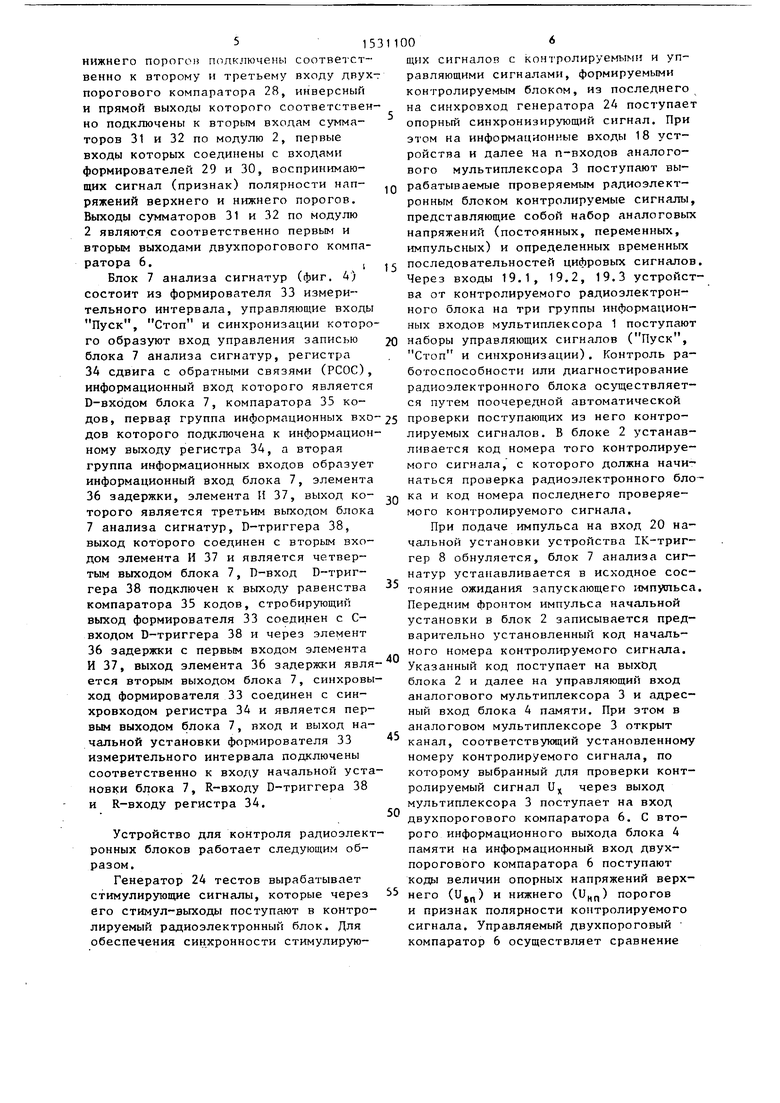

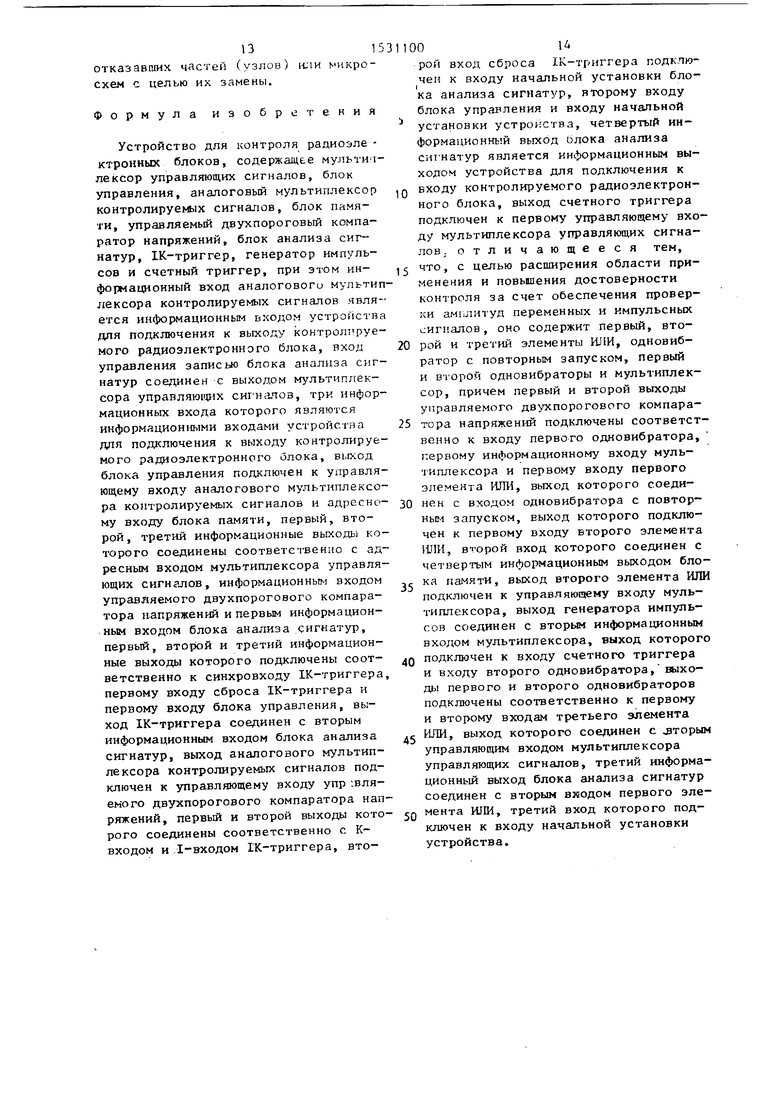

Управляемый двухпороговый компаратор 6 напряжений (фиг. 3) состоит из двухпорогового компаратора 28 напря- бений, первый вход которого является входом управляемого двухпорогового компаратора 6, формирователей 29 и 30 напряжений верхнего () и нижнего (и„п) порогов, управляющие входы которых, воспринимающие коды величин напряжений верхнего и нижнего порогов и признак их полярности, составляют

55 информационный вход двухпорогового компаратора 6, и двух сумматоров 31 и 32 по модулю 2. Выходы формирователей 29 и 30 напряжений верхнего и

30

35

40

45

50

нижнего пороге подключены соответственно к второму н третьему входу двух порогового компаратора 28, инверсный и прямой выходы которого соответственно подключены к вторым входам сумматоров 31 и 32 по модулю 2, первые входы которых соединены с входами формирователей 29 и 30, воспринимающих сигнал (признак) полярности напряжений верхнего и нижнего порогов. Выходы сумматоров 31 и 32 по модулю 2 являются соответственно первым и вторым выходами двухпорогового компаратора 6.I

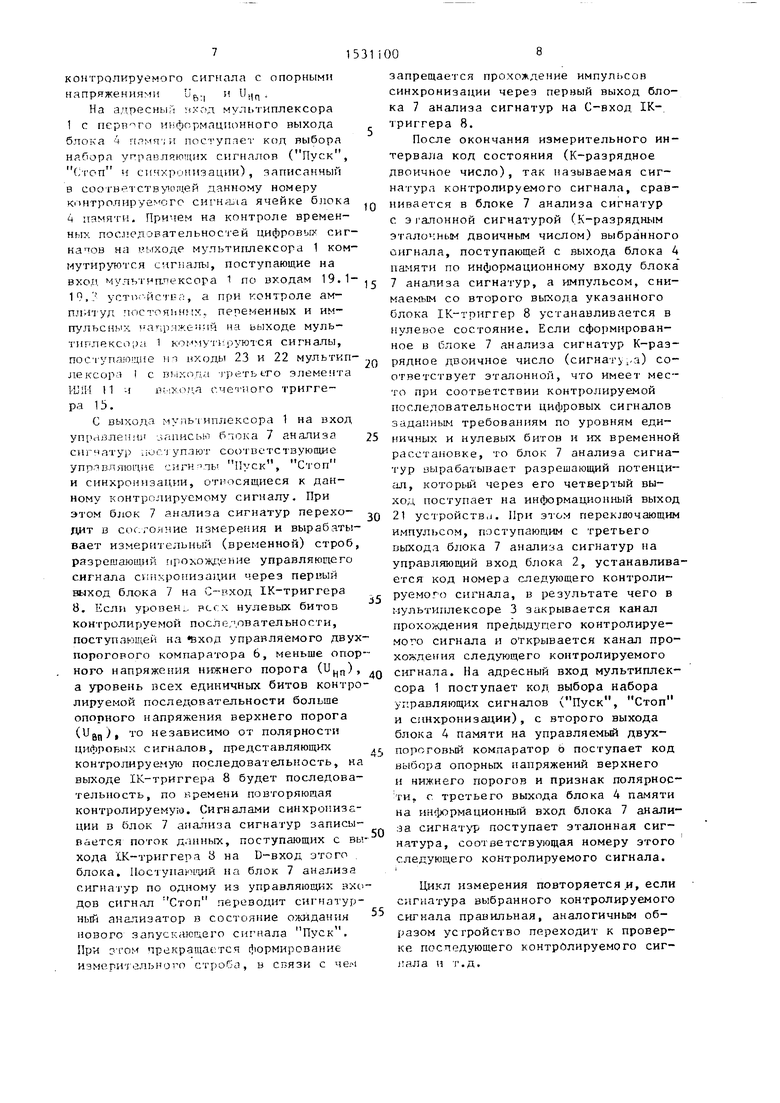

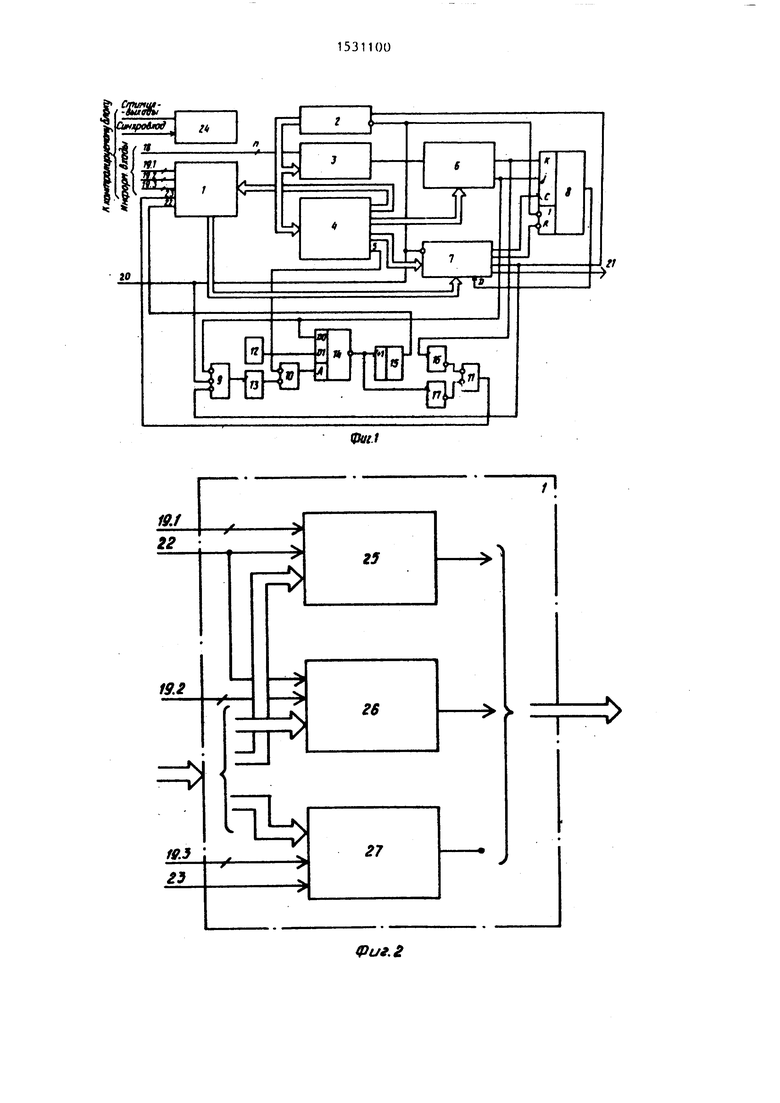

Блок 7 анализа сигнатур (фиг. А) состоит из формирователя 33 измерительного интервала, управляющие входы Пуск, Стоп и синхронизации которого образуют вход управления записью блока 7 анализа сигнатур, регистра 34 сдвига с обратными связями (РСОС), информационный вход которого является D-ВХОДОМ блока 7, компаратора 35 ко

0

5

щих сигналов с контролируемыми и управляющими сигналами, формируемыми контролируемым блоком, из последнего на синхровход генератора 2 поступает опорный синхронизирующий сигнал. При этом на информационные входы 18 устройства и далее на п-входов аналогового мультиплексора 3 поступают вырабатываемые проверяемым радиоэлектронным блоком контролируемые сигналы, представляющие собой набор аналоговых напряжениУ (постоянных, переменных, импульсных) и определенных временных последовательностей цифровых сигналов. Через входы 19.1, 19.2, 19.3 устройства от контролируемого радиоэлектронного блока на три группы информационных входов мультиплексора 1 поступают наборы управляющих сигналов (Пуск, Стоп и синхронизации). Контроль работоспособности или диагностирование радиоэлектронного блока осуществляется путем поочередной автоматической

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Сигнатурный анализатор | 1987 |

|

SU1429118A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1264186A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании автоматических систем контроля цифровых и аналоговых сигналов сложных радиоэлектронных объектов. Целью изобретения является расширение области применения и повышение достоверности контроля за счет обеспечения проверки амплитуд переменных и импульсных сигналов. С этой целью в устройство, содержащее мультиплексор управляющих сигналов, блок управления, аналоговый мультиплексор контролируемых сигналов, блок памяти, управляемый двухпороговый компаратор напряжений, блок анализа сигнатур, IK - триггер, генератор импульсов и счетный триггер, введены три элемента ИЛИ, одновибратор с повторным запуском, два одновибратора и мультиплексор. 4 ил.

30

дов, первая группа информационных вхо-25 проверки поступающих из него контро- дов которого подключена к информацион- лируемых сигналов. В блоке 2 устанав- ному выходу регистра 34, а вторая группа информационных входов образует информационный вход блока 7, элемента 36 задержки, элемента И 37, выход которого является третьим выходом блока 7 анализа сигнатур, D-триггера 38, выход которого соединен с вторым входом элемента И 37 и является четвертым выходом блока 7, П-вход D-триггера 38 подключен к выходу равенства компаратора 35 кодов, стробирующий выход формирователя 33 соединен с С- входом D-триггера 38 и через элемент

35

ливается код номера того контролируемого сигнала, с которого должна начинаться проверка радиоэлектронного блока и код номера последнего проверяемого контролируемого сигнала.

При подаче импульса на вход 20 начальной установки устройства 1К-триг- гер 8 обнуляется, блок 7 анализа сигнатур устанавливается в исходное состояние ожидания запускающего импуэтьса Передним фронтом импульса начальной установки в блок 2 записывается предварительно установленный код началь36 задержки с первым входом элемента .„ ,..,.., „....

И 37, выход элемента 36 задержки явля- Указанный код поступает на выхЬд

ется вторым выходом блока 7, синхровы-блока 2 и далее на управляющий вход

ход формирователя 33 соединен с син-аналогового мультиплексора 3 и адресхровходом регистра 34 и является пер-ный вход блока 4 памяти. При этом в вым выходом блока 7, вход и выход начальной установки формирователя 33 измерительного интервала подключены

45

ного номера контрол1груемого сигнала.

аналоговом мультиплексоре 3 открыт

соответственно к входу начальной установки блока 7, R-входу D-триггера 38 и R-входу регистра 34.

канал, соответствующий установленному номеру контролируемого сигнала, по которому выбранный для проверки контролируемый сигнал и через выход мультиплексора 3 поступает на вход двухпорогового компаратора 6. С вто- Устройство для контроля радиоэлект- рого информационного выхода блока 4

памяти на информационный вход двухпорогового компаратора 6 поступают коды величин опорных напряжений верх50

ронных блоков работает следующим образом.

Генератор 24 тестов вырабатывает стимулирующие сигналы, которые через его стимул-выходы поступают в контролируемый радиоэлектронный блок. Для обеспечения синхронности стимулирую 5 него (и,..) и нижнего (Uun) порогов

и признак полярности контролируемого сигнала. Управляемый двухпороговый компаратор 6 осуществляет сравнение

30

25 проверки поступающих из него контро- лируемых сигналов. В блоке 2 устанав-

35

ливается код номера того контролируемого сигнала, с которого должна начинаться проверка радиоэлектронного блока и код номера последнего проверяемого контролируемого сигнала.

При подаче импульса на вход 20 начальной установки устройства 1К-триг- гер 8 обнуляется, блок 7 анализа сигнатур устанавливается в исходное состояние ожидания запускающего импуэтьса Передним фронтом импульса начальной установки в блок 2 записывается предварительно установленный код началь .„ ,..,.., „....

Указанный код поступает на выхЬд

ного номера контрол1груемого сигнала.

ный вход блока 4 памяти. При этом в

5

аналоговом мультиплексоре 3 открыт

канал, соответствующий установленно номеру контролируемого сигнала, по которому выбранный для проверки кон ролируемый сигнал и через выход мультиплексора 3 поступает на вход двухпорогового компаратора 6. С вто рого информационного выхода блока 4

5 него (и,..) и нижнего (Uun) порогов

и признак полярности контролируемого сигнала. Управляемый двухпороговый компаратор 6 осуществляет сравнение

контролируемого сигнала с опорными напряжениями 1 }. и 1),, ,

На адресный мультиплексора 1 с перв- го информационного выхода блока 4 прмя ;и поступлет код выбора набора угравляютцих сигналов (Пуск, (j i on и синхронизации), записанный в соответствующей данному номеру контролируемого сигншча ячейке 6j:oKa А памяти. Причем на контроле временных последовательностей цифровых сиг- на выходе мультиплексора 1 коммутируются сигналы, поступающие на вход мультип-пексора 1 по входам 19.1- 19. ; устт я йстиа, а при контроле амплитуд постояьнях., переменных и им- пульснь х ь а - .ряжеиий на ьыходе муль- типлексо;и1, 1 ког мутируются сигналы, пос 1 упа;0 дие пп иходы 23 и 22 мультиплексора I с Bbixonii j peTbfro элемента l-L lH И ч .(М,а счетного триггера 15.

С выхода мультиплексора 1 на вход управление записью блока 7 анализа сигнатур iioc/i упзют со1) 1 ветствующие управляющие сигн- ты Пуск, Стоп и синхронизации, от1 осящиеся к данному контро.аируемому сигналу. При этом блок 7 анализа сигнатур переходит в сос-гоиние измерения и вырабатывает измерительный (временной) строб, разрешающий прохождение управляющего сигнала сиихропизагщи через первый выход блока 7 на С-вход 1К-триггера 8. Если уровен. всех нулевых битов контролируемой посотсловательности, поступающей на «вход управляемого двух порогового компаратора 6, меньше опор кого напряжения нижнего порога (U,), а уровень всех единичных битов контро лируемой последовательности больше опорного напряжения верхнего порога (Ugj,), то независимо от полярности цифровых сигналов, представляющих контролируемую последовательность, на выходе 1К-триггера 8 будет последовательность, по времени повторяющая контролируемую. Сигналами синхронизации в блок 7 ама.пиза сигнатур записывается поток данных, поступающих с вы хода Ж-триггера 8 на D-вход этого , блока, Иоступа идай на блок 7 анализа сигна-j yp по одному из управляющих зхо дон сигнал Стоп переводит сигнатурный анализатор в состояние ояшданин нового запускающего сигнала Пуск. При этом прекращается формирование измерительного строба, в спязи с чем

0

5

0

5

0

35

40

45

50

55

запрещается прохождение импульсов синхронизации через первый выход блока 7 анализа сигнатур на С-вход IK- триггера 8.

После окончания измерительного интервала код состояния (К-разрядное двоичное число), так называемая сигнатура контролируемого сигнала, сравнивается в блоке 7 анализа сигнатур с Э1 апонной сигнатурой (К-разрядным эталонным двоичным числом) выбранного сигнала, поступающей с выхода блока А памяти по информационному входу блока 7 анализа сигнатур, а импульсом, снимаемым со второго выхода указанного блока 1К-триггер 8 устанавливается в нулевое состояние. Если сформированное в блоке 7 анализа сигнатур К-разрядное двоичное число (сигнату;-а) соответствует эталонной, что имеет место при соответствии контролируемой последовательности цифровых сигналов заданным требованиям по уровням единичных и нулевых битов и irx временной расстановке, т-о блок 7 анализа сигнатур вырабатывает разрешающий потенци- Ш, которьй через его четвертый выход поступает на информационный выход 21 устройства. При этом переключающим импульсом, поступающим с третьего выхода блока 7 анализа сигнатур на управляющий вход блока 2, устанавливается код номера следующего контролируемого сигнала, в результате чего в мультиплексоре 3 закрывается канал прохождения предыдущего контролируемого сигнала и открывается канал прохождения следующего контролируемого сигнала. На адресный вход мультиплексора 1 поступает код выбора набора управляющих сигналов (Пуск, Стоп и синхронизации), с второго выхода блока 4 памяти на управляемый двух- пороговый компаратор 6 поступает код выбора опорных напряжений верхнего и нижнего порогов и признак полярнос- ти, с третьего выхода блока 4 памяти на информационный вход блока 7 анализа CHrHaT T; поступает эталонная сигнатура, соответствующая номеру этого следующего контролируемого сигнала.

Цикл измерения повторяется и, если сигнатура выбранного контролируемого сигнала правильная, аналогичным образом устройство переходит к проверке поспедующего контролируемого сигнала и т.д.

915

Ксля noCTyrianuu-iii на вход упраяля- емого двухпорогового компаратора b контролируемый сигнал U предсчанляет собой постоянное напряжение положи- тельной (отрицательной) полярности, оно сравнивается с положительными (отрицательными) напряжениями верхнего Ug,, и нижнего и„р порогов, задаваемыми кодами,поступающими с второ- го выхода блока 4 памяти. При этом на управляемый двухпороговый компаратор 6 по одному из информационных вхс- дов подается сигнал О при контроле положительных или l при контроле отрицательных напряжений.

В случае, если /U,,n/ / JxN т.е. когда контролируемый сигнал в норме, на выходах двухпорогового компаратора b устанавливаются сигналы 1, которые поступают на 1К-триггера 8 и на вход первого одно- вибратора 16, на 1-вход 1К-трнгге- ра 8, на первый вход первого элемента ИЛИ 9 и на первый DO-информацион- ный вход мультиплексора 14 соответственно.

При контроле амплитуд постоянных, переменных и импупь-сных напряжений в качестве управляющих сигналов Пуск, Стоп и синхронизации блока 7 анализа сигнатур используются сигналы с BF-I- ходов счетного триггера 15 и третьего элемента ШШ 11, которые с помощью мультиплексора 1 подключаются к входу управления записью блока 7 анализа сигнатур. Причем при контроле постоянных напряжений с дополнительного информационного выхода 5 блока 4 памяти на первый вход второго элемента ИЛИ 10 поступает сигнал О, с выхода эле

мента 10 снимается сигнал 1, который поступает на управляющий вход мультиплексора 14. При этом выход ге- нератора 12 через мультиплексор 14 подключается к входу второго одновиб- ратора 17 и счетному входу триггера 15, с выхода которого снимается сигнал, поступающий на вход 22 мультип- лексора 1 и используемый в качестве сигналов Пуск и Стоп. Сигнал, снимаемый с выхода второго одновибра- тора 17, через элемент ИЛИ 11 поступает на вход 23 мультиплексора Г и используется в качестве сиграла синхронизации.

В результате при проверке любого контролируемого сигнала, представлен

001 (-1

Hoi o н виде поссиянного напряжения любой по:5ярности, блок 7 анализа сигнатур вырабатывае один и тот же измерительный строб, рапрегчающий прохождение только дяух ,1пульсон синхрони- за1у1и на (j-вход 1К-григгера 8. Так как при « ,ц I мя входах К и I триггера 8 стоит Г , то его состояние изменяется каз сдьм раз при поступлении на С-вход импульса синхронизации.

Таким образом, в течение измерительного интервала на входе U-блока 7 анализа сигнатур будет определенная двоичная последовательность, в результате чего блок 7 формирует сиг- fia iypy Ои. . . . 01 f.), одку и ту же для всех постоянимх напряжений, находя- г лхся в пределах установленных поро- го . Указанная сигнатура должна быть записана в качестве эталонной в соот- ве ствую1 1ях ячейках 4 памяти. При HecooTHBTCTBHii U норме, т.е. если(и /Ux| : , сигналы на выходах двухпороговогп компаратора 6 и соответственно на К- и 1-входах триггера , находятся в про- тивофазе (О и 1 или 1 и О). В

О 0

5

,c д

5

результате вид двоичнсй последователь- нос 1 и на информационном входе U-блока 7 ана,пиза сигнатур изменяется, а сформированные последним сигнатуры 00.., ,,.()П для /UBJ, |или GO... 000 для / Uy / i I UHO /отличаются от эталонной. Таким образом, при проверке постоянного напряжения результир Ю1цая сигнатура может быть только трех видов: 00. ..010 для (, N /Ь л/ /1 зл/. 00. ..011 для I fUen/M 00- дпя j ljjl i , анализ которых позволяет получить дополнительную информацию о состоянии контролируемого напряжения. При контроле амплитуд U переменных и импульсных напряжений с дополнительного информационного выхода 5 блока 4 памяти на первый вход второго элемента ШШ 10 поступает сигнал 1. Если при этом /и,„К|ЬЧх/ /Uen/. с второго выхода управляемого двухпорогового компаратора b через первый элемент ИЛИ 9 на вход одновибра- тора 13 с повторным запуском поступают импульсы с периодом, равным периоду кон-1 ролируемого сигнала. На выходе одновибратора 13 с повторным запуском поддерживается сигнал 1 (длительность импульса, вырабатываемого одновибратором 13 с повторным запус-

ком выбрана большей, чем максималь- НЫ11 период контролируемых сигналов), который поступает на второй вход второго элемента Ш1И 10. На выходе элемента 10 устанавливается сигнал О, который поступает на управляющий вход мультиплексора 14. При этом второй выход управляемого двухпорогово- го компаратора 6 через мультиплексор 1 подключается к входу второго одно вибратора 17 и счетному входу триггера 15, с выхода которого снимается имгтульсный сигнал, поступающий на вход 22 мультиплексора 1 и используемый в качестве сигналов Пуск и Стоп.

С выхода второго одновибратора 17 через третий элемент ИЛИ 11 (на первом входе элемента 11 потенциал 1, так как на первом выходе двухпорого- вого компаратора 6 переключений не происходит и первый одновибратор 16 не запускается) импульсный сигнал поступает на первый Вход 23 мультиплексора 1 и используется в качестве сигнала синхронизации.

Как и при контроле постоянных напряжений, блок 7 анализа сигнатур вырабатывает измерительный строб, разрешающий прохождение только двух импульсов синхронизации на С-вход IKтриггера 8. При выполнении условия f нп М- тц I i I и е,п / в моменты появления на С-входе триггера 8 синхронизирующих импульсов на его К- и 1-входах будет сигнал единичного уровня, в результате чего состояние триггера 8 изменяется при поступлении каждого импульса синхронизации. В результате в блоке 7 анализа сигнатур формируется сигнатура 00...010, которая должна быть записана в качестве эталонной в соответствующих ячейках блока А памяти.

В случае, если f U ( f U,, |, переключений на втором выходе управляемого двухпорогового компаратора 6 не происходит, на выходе одновибратора 14 с повторным запуском удерживается сигнал О, а следовательно, на выходе BTOpoi o элемента ИЛИ 10 и управляющем входе мультиплексора 14 - сигнал 1, который подключает выход генератора 12 к входу счетного триггера 15 и входу второго одновиб- ратбра 17. В этом случае, как и в слчае контроля постоянных напряжений, сигналом, из которого в дальнейшем

0

5

0

5

0

5

0

5

формируются сигналы Пуск, Стлт и синхронизации, является сигнал, снимаемый с выхода генератора 12. При этом блок 7 анализа сигнатур, как и в случае контроля постоянных напряжений, формирует сигнатуру СО...000. В случае, если /UTX(JU gp /, для формирования сигнала Пуск, Стоп, снимаемого с выхода счетного триггера 15, используется сигнал с второго выхода управляемого двухпорогового компаратора 6, который с помощью мультиплексора 14 в этом случае подключается к входу счетного триггера 15 и входу второго одновибратора 17.

Для формирования сигнала синхронизации, снимаемого с выхода третьего элемента ИЛИ 11, используются :игна- лы, снимаемые с выходов первого и .второго одновибраторов 16 и 17 (при зтом на вход первого одновибратора 16 поступают импульсные сигналы, снимаемые с первого выхода двухпорогового компаратора 6). В результате блок 7 анализа сигнатур формирует сигнатуру, отличающуюся от сигнатур 00...10 и 00...000.

Сигналы, поступающие на второй и третий входы первого элемента ИЖ 9, необходимы для начальной установки при включении устройства и при подключении нового контролируемого сигнала.

Если сигнатуры всех контролируемых устройством сигналов правильные, в блоке 2 устанавливается код номера начального контролируемого сигнала и цикл контроля повторяется сначала.

В случае, если сигнатура любого подключенного контролируемого сигнала оказывается неправильной (отличающейся от эталонной), на четвертый выход рлока 7 анализа сигнатур и информаци- онный выход 21 устройства поступает запрещающий потенциал. Прохождение переключающих импульсов на третий выход блока 7 анализа сигнатур и далее на управляющий вход блока 2 запрещено и на выходах блока 2 остается код номера сигнала, который к/1ассифицирует- ся как неисправный. При этом блок 2 индицирует номер этого контролируемого сигнала или непосредственно номер соответствующей отказавшей части контролируемого блока. Таким образом, в случае неработоспособности контролируемого радиоэлектронного блока обеспечивается оперативная информация о месте повреждения, вплоть до номеров

131

отказавших частей (узлов) I-UIH микросхем с целью их замены.

Формула изобретения

Устройство для контроля радиоэлектронных блоков, содержащее мультиплексор управляющих сигналов, блок управления, аналоговый мультиплексор контролируемых сигналов, блок памяти, управляемый двухпороговый компаратор напряжений, блок анализа сигнатур, 1К-триггер, генератор импульсов и счетный триггер, при этом информационный вход аналогового мультиплексора контролируемых сигналов является информационны1-1 входом устройства для подключения к выходу контролируемого радиоэлектронного блока, вход управления записью блока анализа сигнатур соединен с выходом мультиплексора управЛЯЮВД1Х сигнапоз, три информационных входа которого являются информационными входами устройства для подключения к выходу контролируемого радиоэлектронного блока, выход блока управления подключен к управляющему входу аналогового мультиплексора контролируемых сигналов и адресному входу блока памяти, первый, второй, третий информационные выходы которого соединены соответственно с адресным входом мультиплексора управляющих сигналов, информационным входом управляемого двухпорогового компаратора напряжений и первым информацион- Hbw входом блока анализа сигнатур, первый, вторюй и третий информационные выходы которого подключены соответственно к синхровходу 1К-триггера, первому входу сброса 1К-триггера и первому входу блика управления, выход 1К-триггера соединен с вторым информационным входом блока анализа сигнатур, выход аналогового мультиплексора контролируемых сигналов под- 1спючен к управляющему входу упр :вля- емого двухпорогового компаратора напряжений, первый и второй выходы которого соединены соответственно с К- входом и .1-входом 1К-триггера, вто110014

рой вход сброса 1К-триггера подключен к входу начальной установки блока анализа сигнатур, второму входу блока управления и входу начальной установки устройства, четвертый информационный выход блока анализа сигнатур является информационным выходом устройства для подключения к

Q входу контролируемого радиоэлектронного блока, выход счетного триггера подключен к первому управляющему входу мультиплексора управляющих сигналов,, отличающееся тем,

5 что, с целью расширения области применения и повышения достоверности контроля за счет обеспечения проверки амгшитуд переменных и импульсных сигналов, оно содержит первый, вто20 рой и третий элементы ИЛИ, одновиб- ратор с повторным запуском, первый и второй одновибраторы и мультиплексор, причем первый и второй выходы управляемого двухпорогового компара5 тора напряжений подключены соответственно к входу первого одновибратора, первому информационному входу мультиплексора и первому входу первого элемента ИЛИ, выход которого соеди0 нен с входом одновибратора с повторным запуском, выход которого подключен к первому входу второго элемента ШШ, второй вход которого соединен с четвертым информационным выходом блоэс ка памяти, выход второго элемента ИЛИ подключен к управляюгаему входу мультиплексора, выход генератора импульсов соединен с вторым информационным входом мультиплексора, выход которого

Q подключен к входу счетного триггера и входу второго одновибратора, выхо- первого и второго одновибраторов подключены соответственно к первому и второму входам третьего элемента

с ИЛИ, выход которого соединен с вторым управляющим входом мультиплексора управляющих сигналов, третий информационный выход блока анализа сигнатур соединен с вторым входом первого элеQ мента ИЛИ, третий вход которого подключен к входу начальной установки устройства.

Фиг, 2

..

Авторы

Даты

1989-12-23—Публикация

1987-01-07—Подача