Изобретение, относится к вычислительной технике и предназначено для использования в цифровых вычислительных машинах различного назначения.

Цель изобретения - с окрап;ение оборудования .

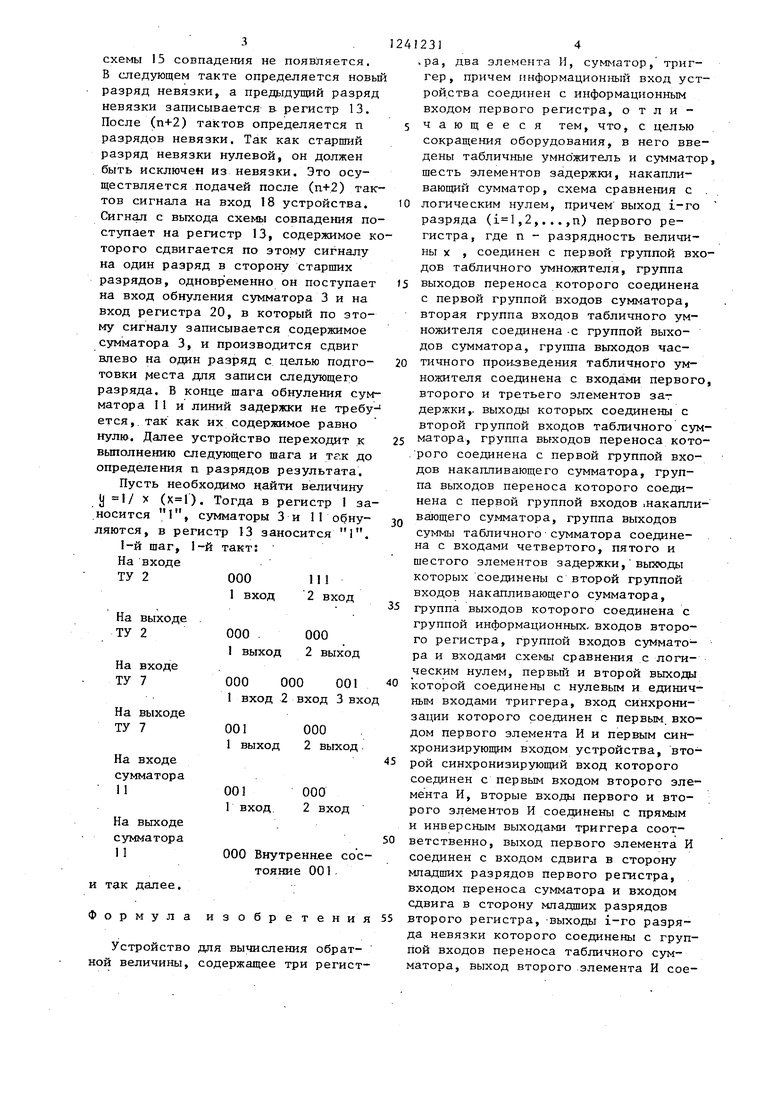

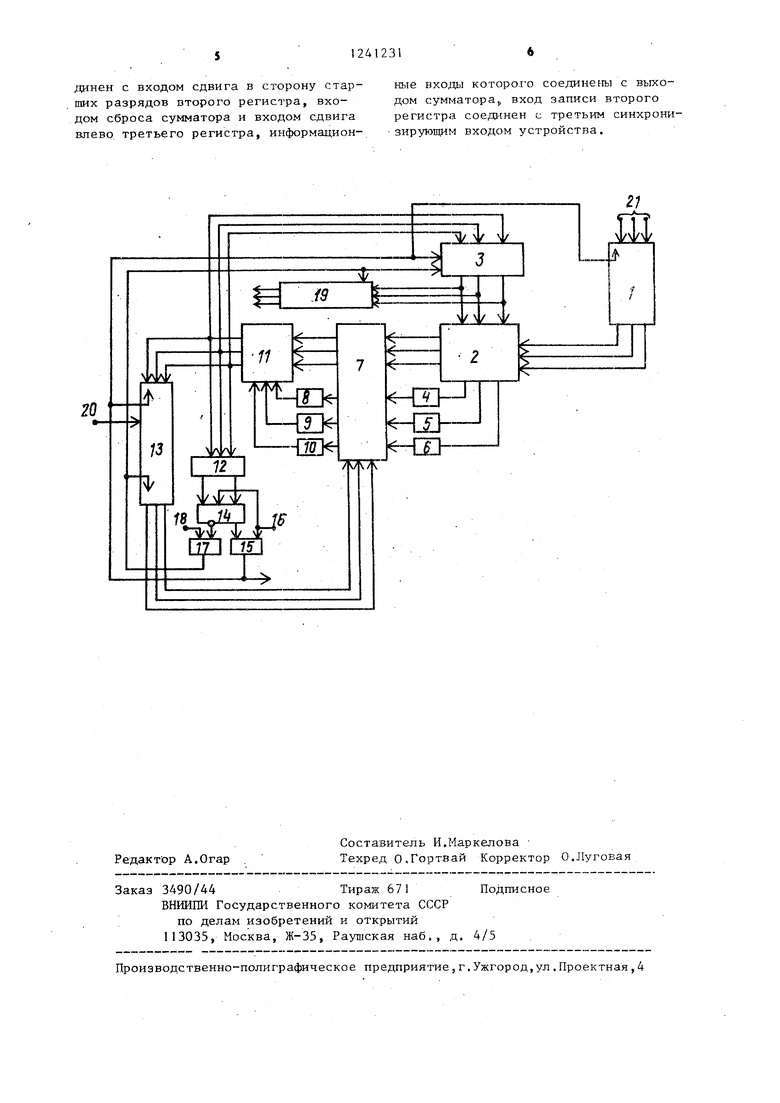

На чертеже приведена схема устройства.

На схеме обозначены первый регистр 1, табличный умножитель (ТУ) 2, сумматор 3, элементы 4-6 задержки, табличный сумматор (ТС) 7, элементы 8-10 задержки, разряд четверичного сумматора 11, схема 12 сравнения с логическим нулем, второй регистр 13, триггер 14, первый элемент И 15, первый синхронизирующий вход 16, второй элемент И ,17, второй синхронизирующий Вход 18 устройства,третий регистр 19, третий синхронизирующий вход 20 устройства и информационный вход 21 устройства.

Устройство работает в соответствии с алгоритмом

, РО е - У;);

(1)

. vyu, vyj + V у,ч, , где (z) - функция вьщеления первого разряда из числа и (под числом Z понимается результат операции z 6; - x.vy; ).

Для того, чтобы исключить вычитание, переменная X заносится в регистр 1 со знаком |(Мнус. Все операции производятся в избыточном четверичном коде. Ддя представления цифр используются три двоичных бита ((0)4 (0.00)4.,; (1)4 (0.01 )4/,; (2)4

(о.1о)4д; (3)4 (0,11)4/2;(-1)4

(1.11)4).

Перед началом операции, помимо того, что .в регистр 1 за носится аргумент (-х), в регистр 13 записывается начальное значение, равное 1, Запись производится подачей сигнала на вход 20, Сумматор 3 и разряд четверичного; сумматора 11 обнуляются. Входы обнуления не показаны. Аргумент л соответствующими (Сдвигами перед началом операции приводится к интервалу 5 1. В этом случае результат по модулю всегда равен или меньше единицы. Схема работает по шаЕсли старщий разряд не равен нулю, триггер 14 по сигналу с входа 16 переходит в единичное состояние и сигнал появляется на выходе схемы 15 совпаде1шя. По этому сигналу содержимое регистров 1 и 13 сдвигается на два разряда в сторону младших разрядов, т.-е, восстанавливается состояние «а начало шага. Одновременно величина с выхода сумматора 11 складывается с содержимым сумматора 3 и ; сумматор 11, а также элементы задержки обнуляются (шина сброса в нуль не показана). Далее первые такты шага повторяются. И так до тех пор, пока старший, разряд не станет равным нулю. Это свидетельствует о том, что текугам. Каждый шаг включает п+2 тактов, 5S разряд результата найден правиль- где п - разрядность величины Х, но. Соответственно триггер 14 по сигВ первом шаге в первом такте на входы ТУ 2 поступают первый старший

налу с входа 16 устанавливается в нулевое состояние и сигнал на выходе

0

разряд числа (-Jf) и разряд V у, с выхода сумматора 3, В ТУ 2 записана таблица перемножения цифр в четверичном коде. .Реззшьтат должен быть представлен разрядами: старшим и младшим. Оба эти разряда поступают на первый и второй входы ТС 7. Чтобы веса этих разрядов совпадали, младший разряд произведения задерживается на такт в элементах 4-6 задержки. На третий вход ТС 7 приходит разряд текущей невязки ;. В ТС 7 записана таблица сложения цифр, поступающих на его входы. Цифры, поступаюш:ие на

5 первый, второй и третий входь, имеют один вес, поэтому они образуют сумму и перенос. При этом образуется двухразрядное число. Первый разряд, пред- - ставляющий собой перенос, поступает

0 на первый выход, а второй разряд, представляющий собой сумму - на второй выход ТС 7. Старший разряд непос- редственно, а мпащиий через элементы 8-10 задержки, поступают на первый

5 и второй входы сумматора 11. Полученный перенос при сложении поступивших цифр используется для корректировки предыдуш,его разряда. Скорректированный разряд поступает на выход сумматора, а текущий разряд запоминается для последующей корректировки. Если выдаваемый разряд есть первый старший разряд невязки, после анализа на схеме 12 сравнения с логическим нулем пода.ется сигнал на вход 16 устройства. Здесь возможны два случая: старший разряд не равен нулю; стар- разряд равен нулю.

Если старщий разряд не равен нулю, триггер 14 по сигналу с входа 16 переходит в единичное состояние и сигнал появляется на выходе схемы 15 совпаде1шя. По этому сигналу содержимое регистров 1 и 13 сдвигается на два разряда в сторону младших разрядов, т.-е, восстанавливается состояние «а начало шага. Одновременно величина с выхода сумматора 11 складывается с содержимым сумматора 3 и ; сумматор 11, а также элементы задержки обнуляются (шина сброса в нуль не показана). Далее первые такты шага повторяются. И так до тех пор, пока старший, разряд не станет равным нулю. Это свидетельствует о том, что теку0

5

0

5

0

S разряд результата найден правиль- но. Соответственно триггер 14 по сигналу с входа 16 устанавливается в нулевое состояние и сигнал на выходе

схемы 15 совпадения не появляется. В следующем такте определяется новы разряд невязки, а предыдущий разряд невязки записывается в регистр 13. После (п+2) тактов определяется п разрядов невязки. Так как старший разряд невязки нулевой, он должен быть исключен из невязки. Это осуществляется подачей после (п,+2) тактов сигнала на вход 18 устройства. Сигнал с выхода схемы совпадения поступает на регистр 13, содержимое кторого сдвигается по этому сигналу на один разряд в сторону старших разрядов, одновр еменно он поступает на вход обнуления сумматора 3 и на вход регистра 20, в который по этому сигналу записывается содержимое сумматора 3, и производится сдвиг влево на один разряд с целью подготовки для записи следующего разряда. В конце шага обнуления сумматора I 1 и линий задержки не требуется,. так как их содержимое равно нyлк. Далее устройство переходит к выполнению следующего шага и тг.к до определения п разрядов результата.

Пусть необходимо найти величину jj 1/ X (). Тогда в регистр 1 заносится 1, сумматоры 3 и М обнуляются, в регистр 13 заносится 1.

1-й шаг, 1-й такт:

На входе

ТУ 2 000 111

1 вход 2 вход

На выходе ТУ 2

На входе ТУ 7

На выходе ТУ 7

На входе

сумматора

11

На выходе сумматора 1 1

так далее.

000. 000

1выход 2 выход

000000 001

1вход 2 вход 3 вход

001

000

1 выход 2 выход.

001 000 1 вход. 2 вход

000 Внутреннее сос- TOHiffle 001.

Формула изобретения 55

Устройство для вычисления обратной величины, содержащее три регист50

5

24J2314

vpa, два элемента И, сумматор, триггер , причем информационный вход устройства соединен с информационньм входом первого регистра, о т л и - 5 чающееся тем, что, с целью сокращения оборудования, в него введены табличные умно житель и сумматор, шесть элементов задержки, накапли- сумматор, схема сравнения с .

10 логическим нулем, причем выход i-ro разряда (,2,...,п) первого регистра, где п - разрядность величины X , соединен с первой группой входов табличного умножителя, группа

15 выходов переноса которого соединена с первой группой входов сумматора, вторая группа входов табличного умножителя соединена -с группой выходов сумматора, группа выходов час20 тичного произведения табличного умножителя соединена с входами первого, второго и третьего элементов зат держки,. выходы которых соединены с второй группой входов табличного сум25 матора, группа выходов переноса кото. рого соединена с первой группой входов накапливающего сумматора, группа выходов переноса которого соединена с первой группой входов .накапливающего су 1матора, группа выходов суммы табличного сумматора соединена с входами четвертого, пятого и шестого элементов задержки, выходы которых соединены с второй группой входов накапливающего сумматора, группа выходов которого соединена с группой информационных- входов второго регистра, группой входов суммато- ра и входами схемы сравнения с логическим нулем, первьй и второй выходы которой соединены с нулевым и единичным входами триггера, вход синхронизации которого соединен с первым, входом первого элемента И и первым синхронизирующим входом устройства, вто5 рой синхронизируюш 1Й вход которого соединен с первым входом второго элемента И, вторые входы первого и второго элементов И соединены с прямым и инверсным выходами триггера соот0 ветственно, выход первого элемента И соединен с входом сдвига в сторону младших разрядов первого регистра, входом переноса сумматора и входом сдвига в сторону младших разрядов второго регистра, -выходы i-ro разряда невязки которого соединены с группой входов переноса табличного сумматора, выход второго элемента И сое30

35

40

динен с входом сдвига в сторону старших разрядов второго регистра, входом сброса сумматора и входом сдвига влево третьего регистра, информационРедактор А.Огар

Составитель И.Маркелова

Техред О.Гортвай Корректор О.Луговая

Заказ 3490/44Тираж 671 Подписное

ВНИИПИ Государственного комитета CGCP

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

ные входа которого соединены с выходом сумматора,, вход записи второго регистра соединен с третьим синхронизирующим входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем алгебраических уравнений | 1986 |

|

SU1324036A1 |

| Вычислительное устройство | 1985 |

|

SU1260946A1 |

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

| Матричное устройство для решения уравнений в частных производных | 1985 |

|

SU1302276A1 |

| Устройство для умножения в избыточной системе счисления | 1984 |

|

SU1229755A1 |

| Устройство для деления в избыточном коде | 1984 |

|

SU1280612A1 |

| Устройство для умножения в избыточном последовательном коде | 1983 |

|

SU1173410A1 |

| Устройство для обработки чисел в избыточном последовательном коде | 1985 |

|

SU1330629A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2011 |

|

RU2475812C1 |

Изобретение относится к области вычислительной техники и предназначено для использования в цифровых вычислительных машинах.различного назначения. С целью сокращения оборудования и повышения быстродействия в устройство, содержащее три регистра, сумматор, триггер, две схемы совпадения, введены два блока памяти, шесть линий задержки, разряд четвертичного избыточного сумматора и схема сравнения. Перед началом операции в первый регистр заносится аргумент (-х). В первом такте на входы первого блока памяти поступает первый старший разряд числа (-Х) и разряд ТУ(, с выхода сумматора. В первом блоке памяти записана таблица перемножения цифр в четверичном коде. Во втором блоке памяти записана таблица сложения цифр, поступающих на его входы. Устройство работает в соответствии с алгоритмом у,+.( РО Г. x-vy;); vvvi y; , с 2 сл

| 1972 |

|

SU417790A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ВСЕСОЮЗНАЯ I | 0 |

|

SU362296A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления обратной величины | 1981 |

|

SU1035603A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1986-06-30—Публикация

1984-04-06—Подача