Изобретение относится к вычислительной технике и может быть использовано в системах аппаратного контроля средств вычислительной техники, в ассоциативных запоминающих устройствах, в устройствах сопряжения цифровых вычислительных машин с магнитными запоминающими устройствами ленточного типа, работающими как в режиме прямого, так и обратного воспроизведения.

Целью изобретения является расширение функциональных возможностей за счет обеспечения последовательного выделения единиц из двоичного кода как в прямом, так и в реверсивном направлениях.

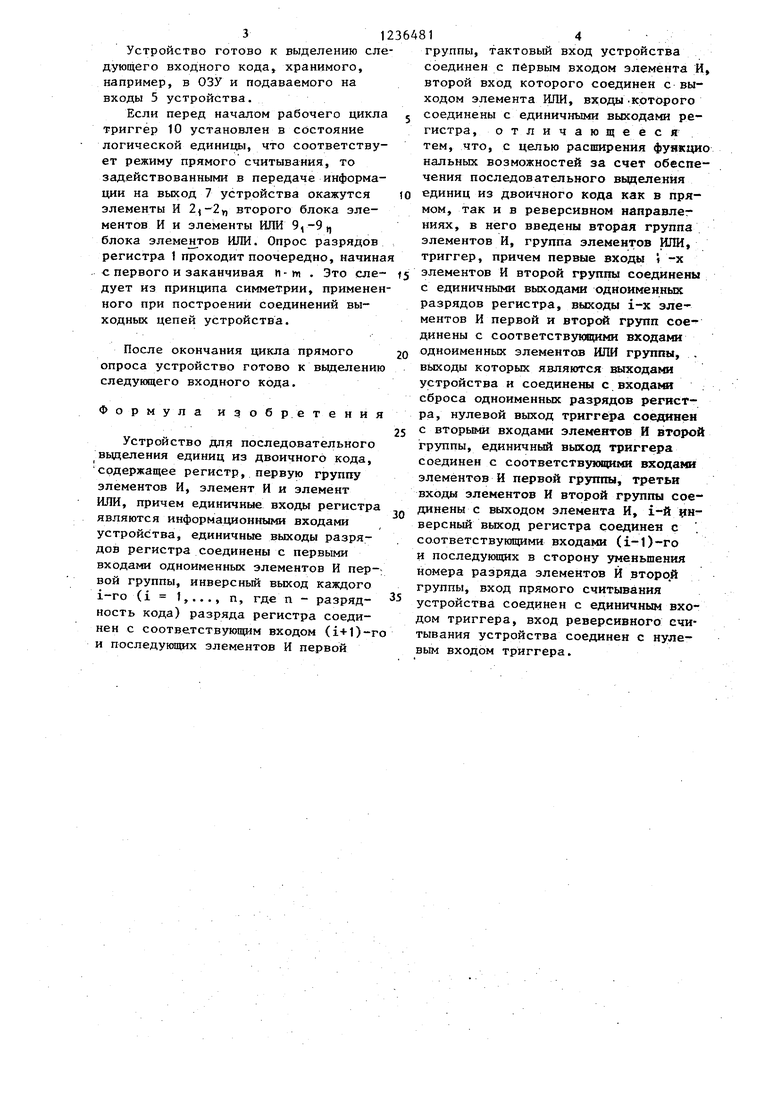

На чертеже представлена функциональная схема устройства.

Устройство содержит регистр 1, первую группу элементов И 2}-2 элемент И 3, элемент ИЖ 4, информационные входы 5 устройства, тактовый рход 6 устройства, информационные выходы 7 устройства, вторую группу элементов И 8,-8, группу элементов ИЛИ 9,-9,, триггер 10, вход 11 прямого, вход 12 реверсивного считывания.

Устройство работает следующим образом.

В исходном состоянии триггеры входного регистра 1 находятся в нулевом состоянии, в результате чего на выходе элемента ИЛИ 4 имеется сигнал логического куля. Сигнал,, поступая на вход элемента И 3, запрещает прохождение через него импульсов с входа 6 для опроса состояния регистра 1. Триггер 10 находитс в произвольном состоянии.

Заблаговременно, до момента окончания установки в состояние логической единицы любого из разрядов регистра 1, триггер 10 должен быть установлен в необходимое состояние прямого или реверсивного считывания .кратковременной подачей на один из соответствующих входов 11 или 12 устройства сигнала логической единицы.

При записи во входной регистр 1 двоичного кода, содержащего хотя бы одну логическую одиницу, на выходе элемента ИЛИ 4 появляется сигнал разрешающий прохождение тактовых импульсов с входа 6. Предположим, что триггер 10 логической единицей на управлякядем входе 12 устройства

5

0

5

0

5

O

S

0

5

установлен в состояние логического

нуля, что соответствует режиму реверсивного считывания, а во входной регистр 1 записан код 10 10. Так как триггер 10 находится в состоянии логического нуля, разрешающий сигнал подается на входы всех элементов группы И 8,-8у, соединенные с триггером 10, а на входы всех элементов группы И 2,-2„, соединенные с триггером 10, подается запрещающий сигнал. Поэтому независимо от состояний разрядов регистра и прочих элементов участвуют в передаче информации только, элементы группы И 8(-8),. Так как п-й разряд регистра 1 находится в состоянии логического нуля, сигнал логического нуля с его единичного выхода является запрещающим для элемента И 8, сигнал логической единицы с его инверсного выхода является разрешающим для всех элементов группы И 8, начиная с И 8.. Разряд 3 регистра 1 находится в состоянии логической единицы. Сигнал логической единицы с единичного выхода разряда 3 регистра 1 является разрешающим для элемента и 8, а сигнал логического нуля с его инверсного выхода является запрещаюпщм для элементов И 82, 8, поэтому первый тактовый импульс производит вьщеле- ние (опрос) только третьего разряда регистра 1, находящегося в единичном состоянии. Выделенный тактовьм импульс третьего разряда с выхода элемента И 8 второго блока элементов И поступает на вход элемента ИЛИ 9А блока элементов ИЛИ, затем на выход 7 устройства и одновременно обнуляет третий разряд- регистра. Обнуление данного разряда регистра позволяет подготовить последующие второй и первый разряды регистра для их опроса и выдачи с соответству- Ггощего элемента ИЛИ блока на выход 7 устройства. Второй тактовый импульс проводит опрос и выделение импульса с элемента И 8, второго блока элементов И и через элемент ШШ 9, блока элементов ИЛИ выдает информацию на выход 7, одновременно происходит обнуление первого разряда регистра 1. После обнуления регистра 1 на выходе элемента ИЛИ 4 появляются сигнал логического нуля, который запрещает прохождение тактовьк импульсов с входа 6 через элемент И 3 для опроса и выд,еления единиц входного кода.

Устройство готово к выделению следующего входного кода, хранимого, например, в ОЗУ и подаваемого на входы 5 устройства.

Если перед началом рабочего цикла триггер 10 установлен в состояние логической единицы, что соответствует режиму прямого считывания, то задействованными в передаче информации на выход 7 устройства окажутся элементы И , второго блока элементов И и элементы ИЛИ 9 ,-9, блока элеме уов ИЛИ. Опрос разрядов регистра 1 проходит поочередно, начина с первого и заканчивая n-m . Это еле- дует из принципа симметрии, примененного при построении соединений выходных цепей устройства.

После окончания цикла прямого опроса устройство готово к вьщелению следующего входного кода.

Формула изобретения

Устройство для последовательного вьщеления единиц из двоичного кода, содержащее регистр, первую группу элементов И, элемент И и элемент ИЛИ, причем единичные входы регистра являются информационными входами устройства, единичные выходы разрядов регистра соединены с первыми входами одноименных элементов И первой группы, инверсный выход каждого i-ro (i 1,..., п, где п - разряд- ность кода) разряда регистра соединен с соответствующим входом (i+1)-r и последующих элементов И первой

10 5

0

5

0

5

группы, тактовый вход устройства соединен с первым входом элемента И, второй вход которого соединен с выходом элемента ИЛИ, входы .которого соединены с единичными выходами регистра, отличающееся тем, что, с целью расширения фуякцио нальных возможностей за счет обеспечения последовательного вьщеления единиц из двоичного кода как в прямом, так и в реверсивном направлег ниях, в него введены вторая группа элементов И, группа элементов ИЛИ, триггер, причем первые входы « -х элементов И второй группы соединены с единичными выходами одноименных разрядов регистра, выходы i-x элементов И первой и второй групп сое- динены с соответствуницимн входами одноименных элементов ИДИ группы, . выходы которых являются выходами устройства и соединены с входаьга сброса одноименных разрядов регистра, нулевой выход триггера соеда1яем с вторыми входами элементов И второй группы, единичный выход триггера соединен с соответствукя(ими входами элементов И первой грутпл, третьи входы элементов И второй группы соединены с выходом элемента И, i-й н- версный выход регистра соединен с соответствующими вxoдa ш (i-l)-ro И последующих в сторону уменьшения номера разряда элементов И второй группы, вход прямого считывания устройства соединен с единичным входом триггера, вход реверсивного считывания устройства соединен с нулевым входом триггера.

5

7/ о-

12

Составитель Г.Пономарева Редактор Г.Волкова Техред М.Ходанич Корректор В.Бутяга

Заказ 3092/52

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для последовательного выделения единиц из двоичного кода | 1984 |

|

SU1252779A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Устройство для передачи телеизмерений с адаптивной коммутацией | 1984 |

|

SU1267459A1 |

| Устройство для определения количества единиц в двоичном числе | 1988 |

|

SU1547072A2 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1368887A1 |

| Устройство для обслуживания запросов | 1985 |

|

SU1264174A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| Устройство для последовательного выделения нулей из двоичного кода | 1985 |

|

SU1290323A1 |

| Многоканальное устройство для распределения задачи процессорам | 1987 |

|

SU1444769A1 |

Изобретение может быть использовано для считывания цифровой информации с магнитных запоминающих устройств ленточного типа, работающих как в режиме прямого, так и обратного воспроизведения. Целью изобретения является расширение функциональных возможностей устройства путем обеспечения реверсивного считывания информации с разрядов входного регистра. В устройстве регистр, первая группа злементов И, элемент И, элемент ИЛИ, в том числе и вновь введенные элементы И второй группы, которые подключены к разрядам симметрично элементам И первой группы, группа элементов ИЛИ и триггер управления, под воздействием управляющих команд прямого или реверсивного считывания и при наличии тактовых сигналов опроса обеспечивают после- довательное вьщеление единиц из двоичного кода как в прямом направлении (от первого разряда к последнему), так и в реверсивном (от последнего разряда к первому). 1 ил. (Л tc со О) 4 00

| Устройство для последовательного выделения единиц из двоичного кода | 1980 |

|

SU922745A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для последовательного выделения единиц из двоичного кода | 1983 |

|

SU1091164A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-07—Публикация

1984-11-20—Подача