Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах с ассоциативной выборкой.

Целью изобретения является упрощение устройства.

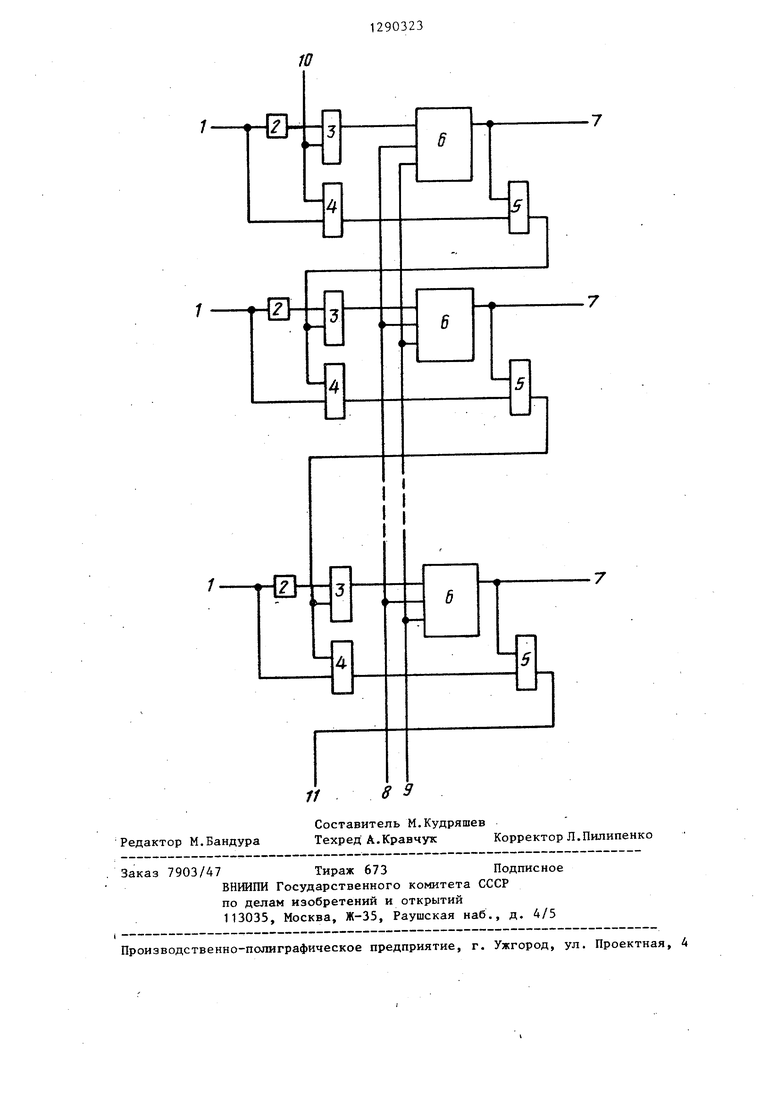

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содерзкит информационные входы 1 устройства, элементы НЕ 2 группы, элементы И 3 группы, элементы И 4 группы, элементы ИЛИ 5 группы, триггеры 6 группы, информационные выходы 7 устройства, тактовый

W

рёбрасывается в единичное состояние а триггер 6, бывший в единичном сос тоянии,- в нулевое. Таким образом, под действием так товых импульсов на выходах устройства последовательно поразрядно появляются импульсы В тех разрядах, на входах которых установлены коды нуля. Сигнал с выхода 11 инициирует конец процесса выделения.

Формула изобретени Устройство для последовательного

вход 8 устройства, вход сброса 9 уст- вьщеления нулей из двоичного кода.

ройства, вход 10 пуска устройства.

Устройство работает следующим образом.

Сигналом с входа 9 все триггеры 6 устанавливаются в нулевое состояние. На выходах 7 устанавливаются потенциалы логического О . Устройство гато- во к работе. На информационные входы 1 подается двоичный код. В начале работы на входе 10 устанавливается потенциал логической 1, который пройдя через элементы И 4 и ИЛИ 5, поступит через элемент И 3 на информационный вход триггера 6 того разряда, в котором первый раз встретится код нуля. При подаче первого тактового импульса по входу 8 единица запишется в триггер 6 и появится на выходе 7 разряда, на входе которого стоит код первого нуля. После первого тактового импульса единичньй потенциал пуска снимается с входа 10. Теперь потенциал логической 1 с установленного в единичное состояние триггера 6 через свой элемент ИЛИ 5 и элементы И 4 и ИЛИ 5, на входы которых поданы коды единицы,и через элемент И 3, на вход которого подан код следующего нуля, установит потенциал единицы на инфЬрмацион- ном входе соответствующего триггера 6. Под действием следующего такг- тового импульса по входу 8 триггер 6 у которого на информационном

входе потенциал логи ческой 1, пе- . I

рёбрасывается в единичное состояние, а триггер 6, бывший в единичном состоянии,- в нулевое.; Таким образом, под действием тактовых импульсов на выходах устройства последовательно поразрядно появляются импульсы В тех разрядах, на входах которых установлены коды нуля. Сигнал с выхода 11 инициирует конец процесса выделения.

Формула изобретения Устройство для последовательного

содержащее группу триггеров, группу элементов НЕ, первую группу элементов И и группу элементов ИЛИ, причем вход сброса устройства соединен с входами сброса триггеров группы, первый вход каждого элемента ИЛИ группы соединен с прямым выходом соответствующего триггера группы, первый вход каждого элемента И первой группы соединен с выходом соответствующего элемента НЕ группы, выход каждого элемента И первой группы соединен с информационным входом соответствующего триггера группы,

«г

отличающе еся тем,что, с целью упрощения, оно содержит вторую группу элементов И, причем каждый информационный вход устройства соединен с входом одноименного элемента НЕ группь1 и первым входом одноименного элемента И второй группы, выход каждого элемента И второй ; группы соединен с вторым входом одноименного элемента ИЛИ группы, выход i-ro (L-1,..n, n - разрядность двоичного кода) элемента ИЛИ группы соединен с вторыми входами (i+1)-x элементов И Стервой и второй групп, вторые входы первых элементов И первой и второй групп являются входом пуска устройства, тактовый вход устройства соединен с входом синхронизации триггеров группы, выходы которых являются информационными выходами

устройства.

11

Редактор М.Бандура

Составитель М.Кудряшев

Техред А.Кравчук Корректор Л.Пилипенко

Заказ 7903/47Тираж 673Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

8 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор тестовой псевдослучайной двоичной последовательности | 1987 |

|

SU1640699A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

| Устройство для формирования тестовых воздействий | 1987 |

|

SU1476473A1 |

| Устройство для распределения заданий процессорам | 1986 |

|

SU1319031A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1234841A1 |

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

| Устройство для последовательного выделения нулей из @ -разрядного двоичного кода | 1982 |

|

SU1037245A1 |

| Устройство для контроля цифровых объектов | 1982 |

|

SU1072048A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Устройство для сравнения чисел | 1979 |

|

SU822176A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах с асс циативной выборкой. Изобретение позволяет упростить устройство за счет сокращения количества связей и использования более простых элементов схемы. Устройство содержит группу триггеров, две группы элементов И, элементы ИЛИ и НЕ. Элементы И одной группы в каждом разряде по сигналам с входа разряда через инвертор и выхода предыдущего разряда образуют запись в триггер разряда регистра. Элементы И второй группы образуют цепь обхода триггеров разрядов по соответствующим сигналам входных кодов. Элементы ИЛИ образуют переходы между схемами разрядов. Под действием тактовых импульсов устройство последовательно выдает сигналы на выходах разрядов, на входах которых установлены коды нулей.1 ил. (Л 00 tN9 00

| Устройство для последовательного выделения нулей из п-разрядного двоичного кода | 1978 |

|

SU739528A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для последовательного выделения нулей из @ -разрядного двоичного кода | 1982 |

|

SU1037245A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-07-10—Подача