(54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО

1

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих специализированных вычислительных устройств, информационноизмерительных систем и систем преобразования координат.

Известно цифровое устройство для извлечения квадратного корня, основанное ira последовательной обработке значений аргумента заданных числом импульсов, содержащее счетчик результата, схемы сравнения кодов, триггеры и элементы И tl.

Недостатком известного устройства является его низкое быстродействие.

Из известных технических решений наиболее близким к предлагаемому изобретению является устройство для извлечения квадратного корня, содержащее входной и выходной регистры, генератор импульсов, делитель частоты, блок управления (2.

Этому устройству присуще недостаточно высокое быстродействие.

Цель изобретения - повышение быстродействия. КОРНЯ

Поставленная цель достигается тем, что в устройство для извлечения квадратного корня, содержащее входной регистр, выходной регистр, генератор импульсов, делитель частоты, блок управления, первый и второй выходы которого подключены к первым входам входного и выходного регистров соответственно, выход генератора импульсов соединен с входом делителя частоты, первый и второй выходы которого соединены с первым и вторым входами блока

«О управления соответственно, первый вход которого соединен также с вторым входом входного регистра, введены вычитающий счетчик, дешифратор, преобразователь параллельного входного кода в двоичный код и злемент И, первый вход

15 .которого соединен с выходом генератора импульсов, второй вход соединен с третьим выходом блока управления, а выход подключен к первому входу вычитающего счетчика и третьему входу входного регистра, выходы которого

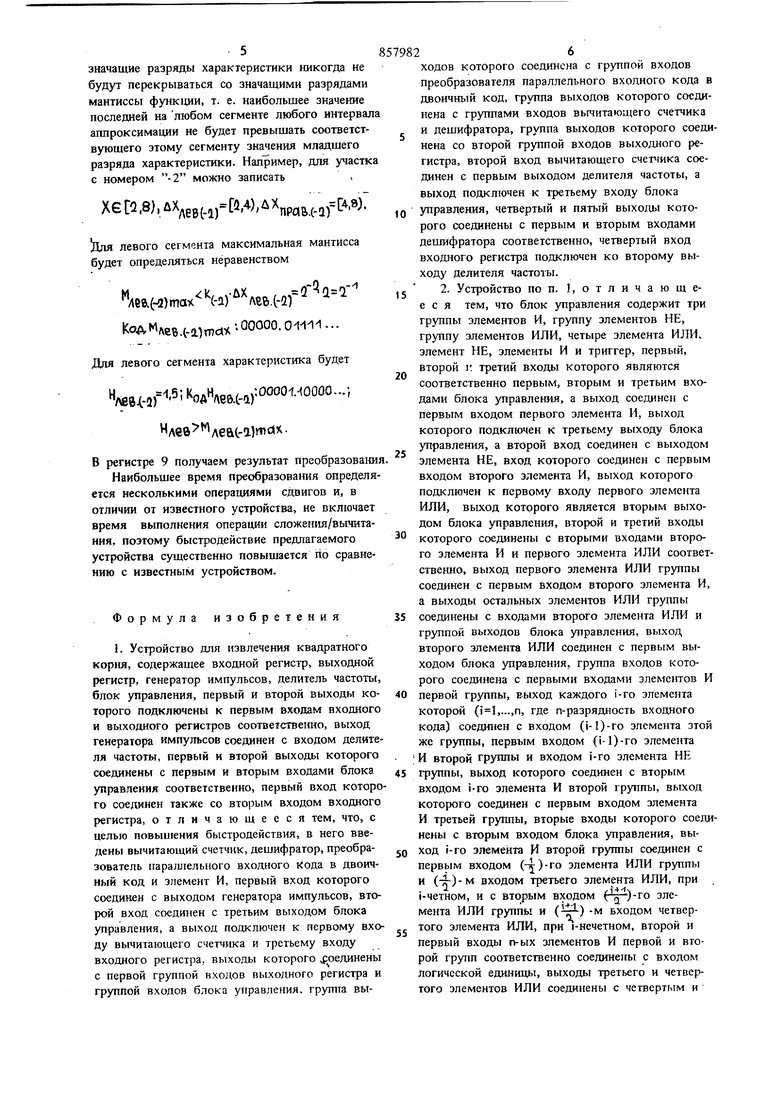

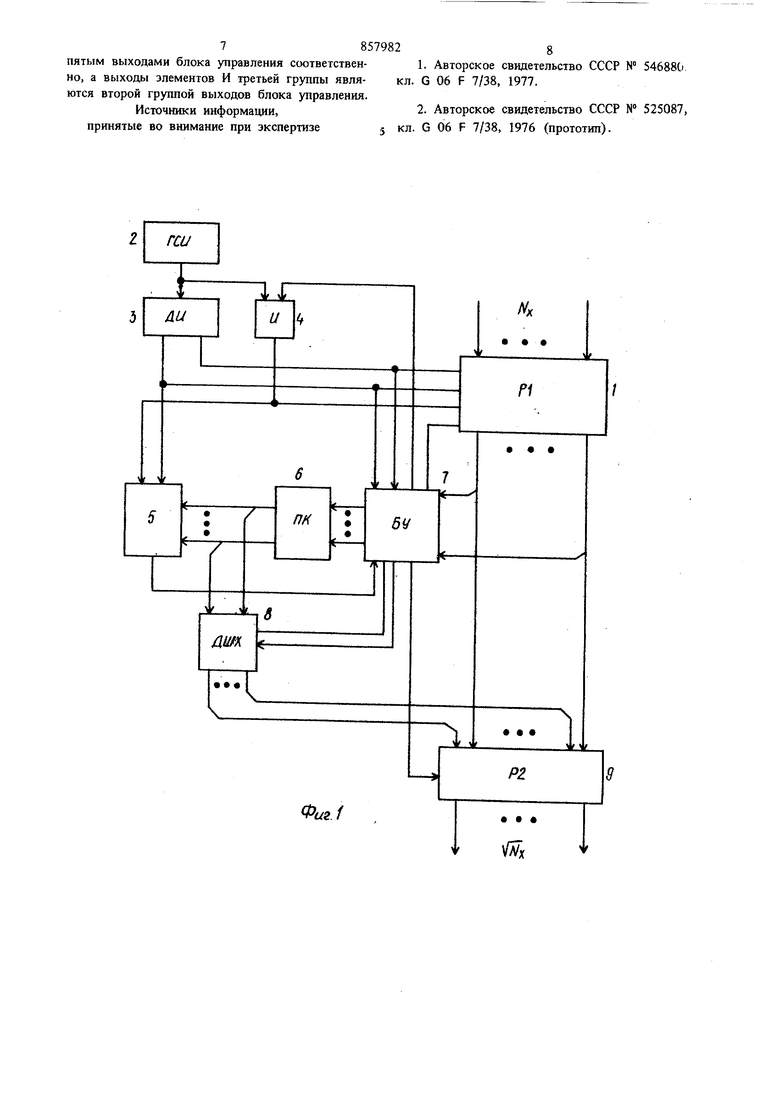

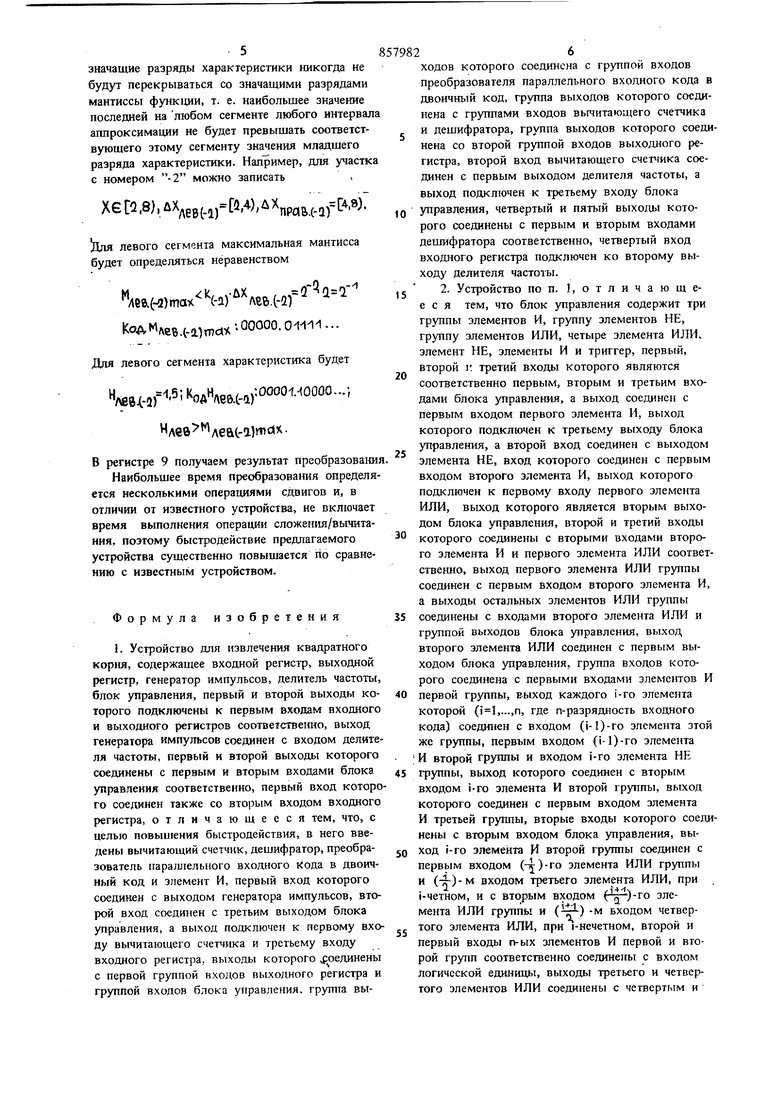

М соединены с первой группой входов выходного регистра и группой входов блока управления, группа выходов которого соединена с.группой входов преобразователя параллельного входного кода в двоичный код, группа выходов которого соединена с группами входов вычитающего счетчика и дешифратора, группа выходов которого соединена с второй группой входов выходлого регистра, второй вход вычитающего счетчика соединен с первым выходом делителя частоты, а выход подключен к третьему входу блока -управления, четвертый и пятый выходы которого соединены с первым и вторым входами деигафратора Соответственно, четвертый вход входаого регистра подключен к второму выходу делителя частоты. Блок управления содержит три группы элементов И, группу элементов НЕ, группу элемен тов ИЛИ, четыре элемента ИЛИ, элемент НЕ, элемешы И и триггер, первый, второй и третий входы которого являются соответственно первым, вторым и третьим входами блока управления, а выход соединен с первым вхоДом первого элемента И, выход которого подключен к третьему выходу блока управления, а второй вход соединен с выходом элемента НЕ, вход которого соединен с первым входом второго; элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход Kdторого является вторым выходом блока управления, второй и третий входы которого соединены с вторыми входами второго элемента И и первого элемента ИЛИ соответственно, выход первого элемента ИЛИ группы соединен с первым входом второго элемента И, а выходы остальных элементов ИЛИ группы соединены с входами второго элемента ИЛИ и группой выходов блока управления, выход второго элемента ИЛИ соединен с первым выходом блока управления, группа входов которого соединена слервыми входами элементов И первой группы выход каждого i-ro элемента которой (,... п,где п - разрядность входного кода) соединен с входом (i-l)-ro элемента этой же группы, первым входом (i-l)-ro элемента И второй гругшы и входом i-ro элемента НЕ группы, выход которого соединен с вторым входом i-ro элемента И второй группы, выход которого сое динен с первым входом элемента И третьей группы, вторые входы которого соединены с вторым входом блока управления, выход i-ro элеме1тта И второй группы соединен с первым и входом (-у)-го элемента ИЛИ группы и (-я-)-м входом третьего элемента ИЛИ, при i-четном, и с вторым входом (-)-го элемента ИЛИ -г-)-м ВХОДОМ четвертого элемента ИЛИ, при (-нечетном, второй и первый входы п-ых элементов И первой и второй групп соотBCTCTBeHiio соединены с входом логической единицы, выходы третьего и четвертого элементов ИЛИ соединены с четвертым и пятым выходами блока У11рав;(ения соответственно, а выходы 24 элементов И третьей группы являются второй группой выходов блока управления. На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 и 3 схема блока управления; на фиг. 4 - график исходной и аппроксимирующей функции. Устройство содержит входной регистр 1 (Р1), генератор 2 импульсов (ГСИ), делитель 3 частоты (ДЧ), элемент И 4, вычитающий счетчик 5 (СИ), преобразователь 6 параллельного входного кода в двоичный код (ПК), блок 7 управления (БУ), дешифратор 8 (ДШ), выходной регистр 9 (Р2), первую, вторую и третью группы элементов И 10, 11 и 12, группу элементов НЕ 13, группу элементов ИЛИ 14, первый, второй, третий и четвертый элементы ИЛИ 15, 16, 17 и 18, элемент НЕ 19, первый и второй элементы И 20 и 21 и триггер 22. Устройство работает следующим образом. Входная величина N в виде параллельного кода поступает на входной регистр I, который является сдвигоВ| 1м регистром. С его выхода код NX поступав в блок 7 управления, который анализирует, в какую пару попала старшая значащая единица Ny, т.е. определяет номер интервала, который затем в преобразователе .6 кодов преобразуется в двоичный код. Двоичный код номера интервала аппроксимации заносится в вычитающий счетчик 5 и поступает на дешифратор 8, на который также из блока 7 управления поступает информа1щя о том, какому сегменту интервала аппроксимации (левому или правому) соответствует старшая значащая единица кода Nf, В дешифраторе образуется соответствующая установленному интервалу аппроксимации характеристика функции. Чтобы получить значение приращения аргумента на данном интервале, необходимо из кода N вычесть значение JНо так как любое значение х является целой степенью числа 2, то операцию вычитания можно исключить. При этом в регистре 1 необходимо установить в ноль значение соответствующего X; двоичного разряда. Эту операцию осуществляет блок 7 управления, и в регистре 1 получаем приращение аргумента Дх. Если текущее значение входной величины N находится ся в нулевом интервале аппроксимации, где коэффициент наклона К - 1, значение ДХ j, равно мантиссе функции, и поэтому последующее масштабирование не требуется. Код, соответствующий Zix , заносится в регистр 9, куда также помещается характеристика. Занесение кода Лх в регистр 9 осуществляется так, что каждый разряд- кода, содержащий нуль, не изменяет состояния соответствующих разрядов регистра 9, а единичные разряды кода осуществляют установку разрядов регистра 9 в едини- нле состояние. При такой операции, очевидно. значащие разряды характеристики никогда не будут перекрываться со значащими разрядами мантиссы функвди, т. е. наибольшее значение последней на любом сегменте любого интервал аппроксимации не будет превышать соответствующего этому сегменту значения младшего разряда характеристики. Например, для участка с номером -2 можно записать Хе Г2.8), лХдез(.,р 5Л), Д , 1Цля левого сегмента максимальная мантисса будет определяться неравенством .ев.(ч.)).( Код Млей.(-а)шсЛ1 QO OO-0 Для левого сегмента характеристика будет Vnf Леб.(-аг °° -- 00 °Млев леас-а)тах. в регистре 9 получаем результат преобразовани Наибольшее время преобразования определя ется несколькими операциями сдвигов и, в отличии от известного устройства, не включает время выполнения операции сложения/вычитания, поэтому быстродействие предлагаемого устройства существенно повыииется по сравнению с известным устройством. Формула изобретения 1. Устройство для извлечения квадратного корня, содержащее входной регистр, выходной регистр, генератор импульсов, делитель частоты блок управления, первый и второй выходы которого подключены к первым входам входного и выходного регистров соответственно, выход генератора импульсов соединен с входом делите ля частоты, первый и второй выходы которого соединены с первым и вторым входами блока управления соответственно, первый вход которо го соединен также со вторым входом входного регистра, отличающееся тем, что, с целью повышения быстродействия, в него введены вычитающий счетчик, дешифратор, преобразователь 11ара;и1ельного входного кода в двоичный код и элемент И, первый вход которого соединен с выходом генератора импульсов, второй вход соединен с третьим выходом блока управления, а выход подключен к первому вхо ду вычитающего счетчика и третьему входу входного регистра, выходы которого ;оединены с первой группой входов выходного регистра и группой входов блока управления, группа вы26ходов которого соединена с группой входов Преобразователя параллельного входного кода в двоичный код, группа выходов которого соединена с группами входов вьиитающего счетчика и дешифратора, группа выходов которого соединена со второй группой входов выходного регистра, второй вход вычитающего счетчика соединен с первым выходом делителя частоты, а выход подключен к третьему входу блока управления, четвертый и пятый выходы которого соединены с первым и вторым входами дешифратора соответственно, четвертый вход входного регистра подключен ко второму выходу делителя частоты. 2. Устройство по п. , о т л и ч а ю щ ее с я тем, что блок управления содержит три группы элементов И, группу элементов НЕ, группу элементов ИЛИ, четыре элемента ИЛИ, элемент НЕ, элементы И и триггер, первый, второй у. третий входы которого являются соответственно первым, вторым и третьим входами блока управления, а выход соединен с первым входом первого элемента И, выход которого подключен к третьему выходу блока управления, а второй вход соединен с выходом элемента НЕ, вход которого соединен с первым входом второго элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход которого является вторым выходом блока управления, второй и третий входь которого соединены с вторыми входами второго элемента И и первого элемента ИЛИ соответствешсо, выход первого элемента ИЛИ группы соединен с первым входом второго элемента И, а выходы остальных элементов ИЛИ группы соединены с входами второго элемента ИЛИ и группой выходов блока управления, выход второго элемента ИЛИ соединен с первым выходом блока управления, группа входов которого соединена с первыми входами элементов И первой группы, Е.ЫХОД каждого i-ro элемента которой (,...,n, где п-разрядность входного кода) соединен с входом (i-l)-ro элемента этой же группы, первъ1м входом (i-l)-ro элемента И в-торой группы и входом i-ro элемента НЕ группы, выход которого соединен с вторым входом i-ro элемента И второй группы, выход которого соединен с первым входом элемента И третьей группы, вторые входы которого соединены с вторым входом блока управления, выход i-ro элемента И второй группы соединен с первь1м входом (-5-)-го элемента ИЛИ группы и (-1-) - м входом третьего элемента ИЛИ, при -четном, и с вторым входом fi)-ro элемента ИЛИ группы и () -м входом четвертого элемента ИЛИ, при i-нечетном, второй и первый входы п-ых элементов И первой и второй групп соответственно соединены с входом логической единицы, выходы третьего и четвертого элементов ИЛИ соединены с четвертым и

78579828

пятым выходами блока управления соответствен-1. Авторское свидетельство СССР № 546880

но, а выходы элементов И третьей группы явля- кл. G 06 F 7/38, 1977.

ются второй группой выходов блока управления. ..j С25087

Источники информации,2. Авторское свидетельство СССР N 525087,

принятые во внимание при экспертизеj кл. G 06 F 7/38, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Цифровой функциональный преобразователь | 1981 |

|

SU960837A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU1099317A1 |

| Устройство для извлечения квадратного корня | 1982 |

|

SU1136155A1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

5 I f

2Z

&

J

бми ynpatMMtf

Авторы

Даты

1981-08-23—Публикация

1979-11-16—Подача