J -:::|

«

imtaa

(Л

со

00

оо

со

со

sj

я 3

57 52

Пуж

гв

17

второй блок 2 памяти констант аппроксимации, блок 3 суммирования, блок 4 выходных регистров, первый 5, второй 6, третий 7, четвертый 8 регист ры блока 4 выходных регистров, выходы 9 результата, регистр 0 аргумента,.вход 11 аргумента, первую 12, вторую 13, третью 14, четвертую J5 Г1)уппы элементов ИЛИ, умножители 16-

18 старшего, среднего, младшего байта, регистр 19 константы, блок 20 управления, вход 21 запуска. Предложенное устройство использует квадратичную аппроксимацию, которая позволяет на заданном интервале изменения аргумента вычислить значение функции в 5-10 раз точнее, чем при линейной аппроксимации. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Устройство для вычисления корня третьей степени | 1985 |

|

SU1288695A1 |

| Устройство для вычисления функций в модулярной системе счисления | 1985 |

|

SU1322268A1 |

| Устройство для вычисления корня | 1985 |

|

SU1339556A1 |

| Цифровой генератор колоколообразных функций | 1978 |

|

SU737936A1 |

| Устройство для вычисления функции арктангенса | 1989 |

|

SU1661760A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1191908A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

Изобретение относится к вычис лительной технике и может быть использовано в виде автономного специализированного вычислителя или в качестве функционального расширителя в составе больших ЭВМ. Целью изобретения является повышение точности за счет применения квадратичной аппроксимации. Устройство содержит первый блок 1 памяти констант аппроксимации.

1

Изобретение относится к вычисли тельной технике и может быть использовано в качестве специализированного вычислителя.

Цель изобретения - повышение точ- ности.за счет применения квадратичной аппроксимации.

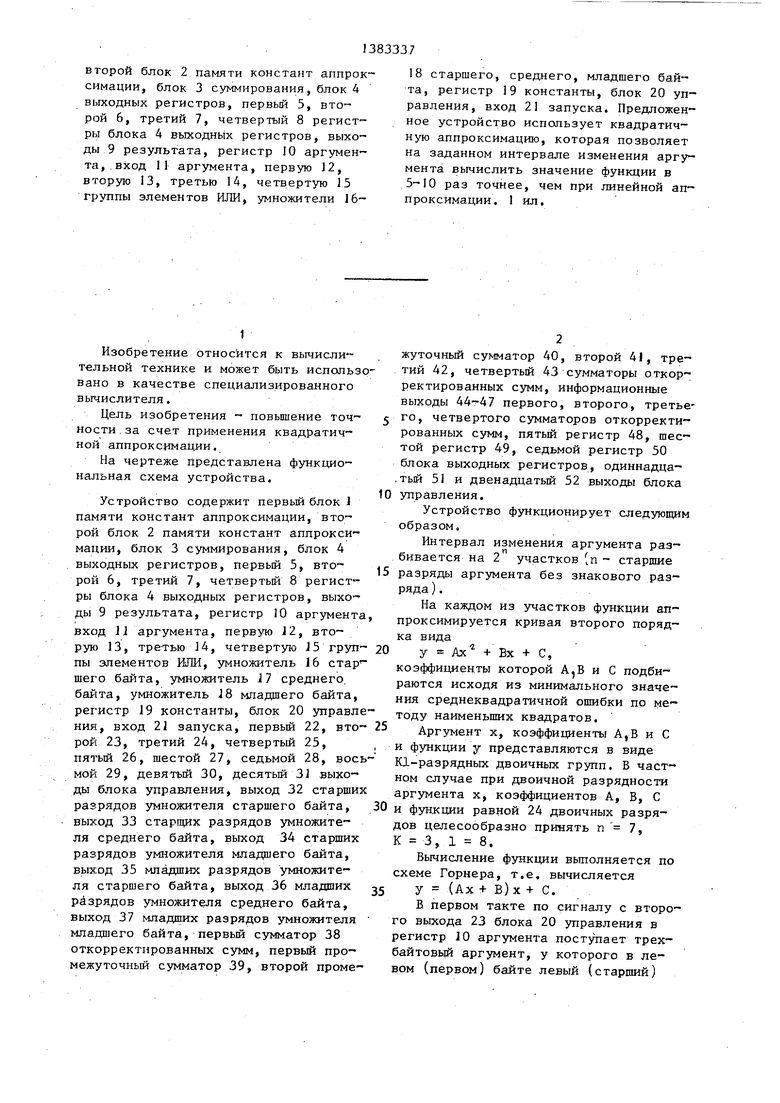

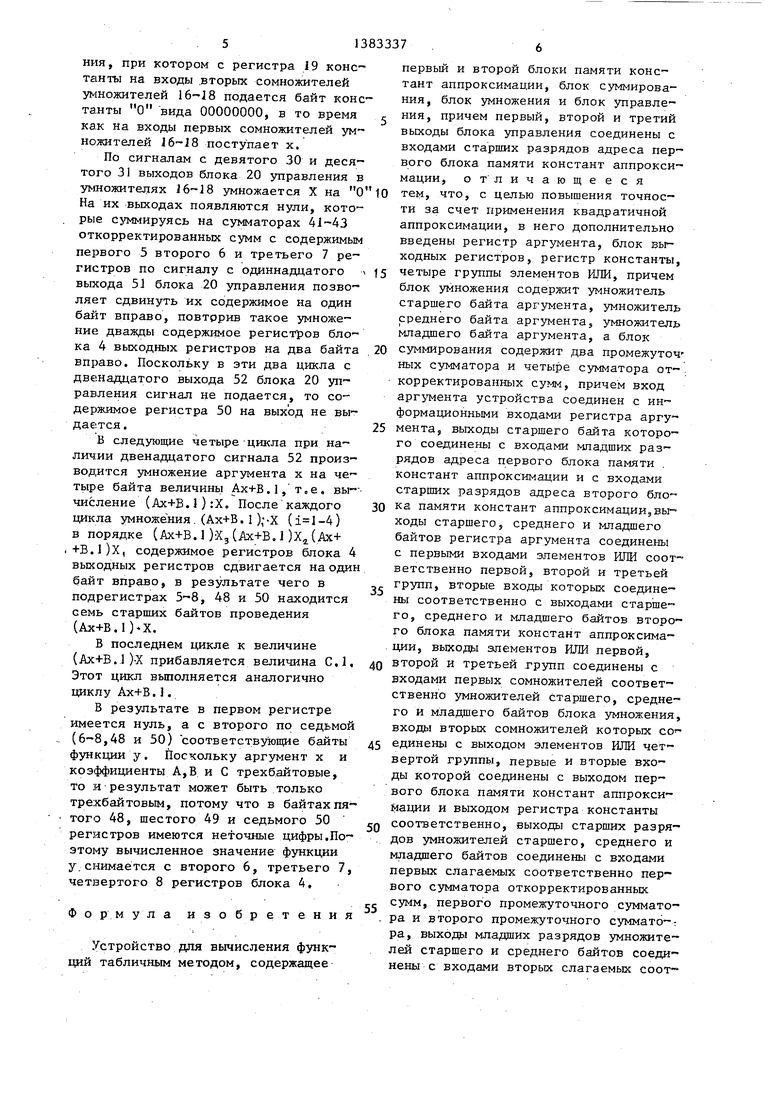

На чертеже представлена функциональная схема устройства.

1

Устройство содержит первый блок J

памяти констант аппроксимации, второй блок 2 памяти констант аппроксимации, блок 3 суммирования, блок 4 выходных регистров, первый 5, вто- рой 6, третий 7, четвертый 8 регистры блока 4 выходных регистров, выходы 9 результата, регистр 10 аргумента вход 11 аргумента, первую 12, вторую 13, третью J4, четвертую J5 груп- пы элементов ИЛИ, з множитель 16 стар шего байта, умножитель J7 среднего. 6afiTa, умножитель J8 младшего байта, регистр 19 константы, блок 20 управления, вход 21 запуска, первьй 22, вто- рой 23, третий 24, четвертый 25, пятый 26, шестой 27, седьмой 28, вось мой 29, девятый 30, десятьш 31 выходы блока управления, выход 32 старших разрядов умножителя старшего байта, выход 33 старщих разрядов умножителя среднего байта, выход 34 старших разрядов умножителя младшего байта, выход 35 младших разрядов умножителя старшего байта, выход 36 младших разрядов умножителя среднего байта, выход 37 младших разрядов умножителя младшего байта, первый сумматор 38 откорректированных сумм, первый промежуточный cj MMaTop 39, второй промежуточный сумматор 40, второй 41, третий 42, четвертьй 43 сумматоры откорректированных сумм, информационные выходы 44-47 первого, второго, третьего, четвертого сумматоров откорректированных сумм, пятый регистр 48, шестой регистр 49, седьмой регистр 50 блока выходных регистров, одиннадца- .тьй 51 и двенадцатьй 52 выходы блока управления.

Устройство функционирует следуюш 1М образом.

Интервал изменения аргумента разбивается на 2 участков (п - старшие разряды аргумента без знакового разряда ).

На каждом из участков функции аппроксимируется кривая второго порядка вида

у Ах +Бх+С,

коэффициенты которой А,В и С подбираются исходя из минимального значения среднеквадратичной ошибки по методу наименьших квадратов.

Аргумент X, коэффициенты А,В и С и функции у представляются в виде К1-разрядных двоичных групп. В частном случае при двоичной разрядности аргумента х, коэффициентов А, В, С и функции равной 24 двоичных разрядов целесообразно принять п 7, К 3, 1 8.

Вычисление функции вьшолняется по схеме Горнера, т.е. вычисляется

у (АХ + В)х + С.

Б первом такте по сигналу с второго выхода 23 блока 20 управления в регистр 10 аргумента поступает трех- байтовьй аргумент, у которого в левом (первом) байте левый (старший)

двоичный разряд знаковой, а по сигналу с одиннадцатого выхода 51 блока 20 управления обнуляются регистры с первого по седьмой 5-8,48-50 блока выходных регистров,

Во втором такте из первого блока памяти констант аппроксимации по адресу, задаваемому п старшими разря- .дами X, с помощью сигнала с первого выхода 22 блока 20 управления извлекается третий (младший) байт константы А (а) и через четвертую группу элементов ИЛИ поступает на входы вторых сомножителей умножителей J6-J8, на входы первых сомножителей которых по сигналу с третьего 24 выхода блока 20 управления с регистра JO аргумента на первую, вторую и третью группы элементов ИЛИ поступаю г бай- ты аргумента х: на умножитель 16 старшего байта (байт х ,), на умножи тель 17 среднего байта (байт х), на умножитель 18 младшего байта (байт х ,).

В третьем такте по сигналу с девятого 30 вьпсода блока 20 управления операнды а., и х вводятся в соответствующие умножители 16-18 старшего, среднего и младшего байта.

В четвертом такте по сигналу с десятого 31 выхода блока 20 управления результаты умножения х,а,, , и , с выхода умножителей 16-18 старшего, среднего и младшего байта поступают .на промежуточных сумматоров 39 и 40 и сумматоров 38, 41-43 промежуточных сумм, т.е. вьшолняется и начинается процесс вычисления величины х а.

по правилу ,- «-Э

-x-aS x,S -a-S + x-S-ajS + + x, (c ,.S- + als;) +

+(c;s % a/S- ).+ (C;S H- a .S- ),

Величины

и a, появляются на

выходах умножителя 16 старшего байта, величины с 2 и aj на выходах умно жителя 17 среднего байта, величины с и а , - на выходах умножителя J8 младшего байта.

В пятом такте по сигналу с один- н адцатого 51 выхода блока 20 управления содержимое сумматоров 38,41-43 заносится соответственно в регистры 5-8 блока 4 выходных регистров. На этом заканчивается цикл умножения аргумента х на младший байт а.коэ фициента А.

0

5

0

ко ЭФФИЦИ- L, КОЭФФИДалее производится умножение аргу мента X на средний байт а ента А и на старший байт а циента А. Это выполняется в тактах,на - чиная с второго,в котором из первого блока 1 памяти по адресу, задаваемому п старшими разрядами х с помощью сигналов с четвертого 25, а затем с пятого 26 выходов блока 20 управления, извлекается второй (а) и первый (Ъ,) байты константы А.

После того как закончились три цикла умножения аргумента х на А в

5 регистрах -6-8, 48-50 находятся шесть байтов этого произведения.

Далее по сигналу с шестого выхода 27 блока 20 управления по адресу, заданному старшими разрядами аргумента х, с второго блока 2 памяти констант через аппроксимации первую, вторую и третью грзтапы элементов ИЛИ на умножители 16-J8 поступают байты коэффициента В: на умножитель 16 старшего байта Ь,, на умножитель 17 среднего байта Ъ,, , на умножитель 18 младшего байта Ъ . Одновременно по сигналу восьмого выхода 29 блока 20 управления с регистра J9 константы

0 через четвертую группу элементов ИЛИ на входы вторых сомножителей умножителей 16-18 поступает байт константы 1 вида 00000001.

В пocлeдyюш ie два такта по сигна5 лам с девятого 30 и десятого 31 выходов блока 20 управления в умножителях 16-J8 вычисляется величина В.1. В результате работы блока 3 пуммато- ров величина Ах + В1 сформирована на выходах 45-47 блока 3 сумматоров, на выходе 44 блока 3 сумматора имеется нуль.

Далее по сигналу с одиннадцатого выхода 51 блока 20 управления содер5 жимое сумматоров 38, 41, 42 и 43 блока 3 суммирования заносится в регистры 5-8 регистра 4 функций, а содержимое регистров 48 и 49 смещается вправо на один байт. В результате на

0 , ., .,

н

,

Содержимое регистров 6-8 и 48 необходимо сместить на два байта вправо так, чтобы в регистре 50 находился четверый байт величины Ах+В, Такой сдвиг в устройстве выполняется двумя циклами умножения х на О. Это умножение выполняется по сигналу восьмого выхода 29 блока 20 управле-.

ния, при котором с регистра 19 конс- тгшты на входы .вторых сомножителей умножителей le- lS подается байт конс танты О вида 00000000, в то время как на входы первых сомножителей умножителей поступает х.

По сигналам с девятого 30 и десятого 31 выходов блока 20 управления в умножителях 16-18 умножается X на О На их выходах появляются нули, которые суммируясь на сумматорах 41-43 откорректированных сумм с содержимым первого 5 второго 6 и третьего 7 регистров по сигналу с одиннадцатого выхода 51 блока 20 управления позволяет сдвинуть их содержимое на один байт вправо, повтррив такое умножение дважды содержимое регистров блока 4 выходных регистров на два байта вправо. Поскольку в эти два цикла с дв€ Надцатого выхода 52 блока 20 управления сигнал не подается, то содержимое регистра 50 на выход не выдается.

В следующие четыре-цикла при наличии двенадцатого сигнала 52 производится умножение аргумента х на четыре байта величины Ax+B.l, т.е. вычисление (Ах+Б.1):Х. После каждого цикла умножения. (Ах+В. 1 );-Х () в порядке (Axi+B.l )Хз(Ах+В.1 )X4{Ax+ +B.l)X, содержимое регистров блока 4 выходных регистров сдвигается на один байт вправо, в результате чего в подрегистрах 5-8, 48 и 50 находится семь старпшх байтов проведения (Ах+В.1)-Х.

В последнем цикле к величине (Ах+В.1)-Х прибавляется величина С,, Этот цикл вьшолняется аналогично циклу Ах+В..

В результате в первом регистре имеется нуль, а с второго по седьмой (6-8,48 и 50) соответствун) байты функции у. Поскольку аргзт ент х и коэффициенты А,В и С трехбайтовые, то и результат может быть только трехбайтовым, потому что в байтах пятого 48, шестого 49 и седьмого 50 регистров имеются неточные цифры.Поэтому вычисленное значение функции у.снимается с второго 6, третьего 7, четвертого 8 регистров блока 4,

Формула изобретения

Устройство для вычисления функций табличным методом, содержащее

0 5 20 5

30

о

з п

5

первый и второй блоки памяти констант аппроксимации, блок суммирования, блок умножения и блок управления, причем первый, второй и третий выходы блока управления соединены с входами старших разрядов адреса первого блока памяти констант аппроксимации, отличающееся тем, что, с целью повышения точности за счет применения квадратичной аппроксимации, в него дополнительно введены регистр аргумента, блок выходных регистров, регистр константы, четыре группы элементов ИЛИ, причем блок умножения содержит умножитель старшего байта аргумента, умножитель среднего байта аргумента, умножитель младшего байта аргумента, а блок суммирования содержит два промежуточ ных сумматора и четыре сумматора от-, корректированных сумм, причем вход аргумента устройства соединен с информационными входами регистра аргумента, выходы старшего байта которого соединены с входами младших разрядов адреса первого блока памяти . констант аппроксимации и с входами старших разрядов адреса второго блока памяти констант аппроксимации,выходы старшего, среднего и младшего байтов регистра аргумента соединены с первыми входами элементов ИЛИ соответственно первой, второй и третьей групп, вторые входы которых соединены соответственно с выходами старшего, среднего и младшего байтов второго блока памяти констант аппроксимации, выходы элементов ИЛИ первой, второй и третьей .групп соединены с входами первых сомножителей соответственно умножителей старшего, среднего и младшего байтов блока умножения, входы вторых сомножителей которых единены с выходом элементов ИЛИ четвертой группы, первые и вторые входы которой соединены с выходом первого блока памяти констант аппроксимации и выходом регистра константы соответственно, выходы старших разрядов умножителей старшего, среднего и младшего байтов соединены с входами первых слагаемых соответственно пер вого сумматора откорректированных сумм, первого промежуточного сумматора и второго промежуточного суммато-г ра, выходы младших разрядов умножителей старшего и среднего байтов соединены с входами вторых слагаемых соот

ветственно первого и второго промежуточных сумматоров, выходы которых соединены с входами первых слагаемых соответственно второго и третье- го сумматоров откорректированных сумм вход первого слагаемого четвертого сумматора откорректированных сумм соединен с выходами младших разрядов умножителя младшего байта, выход пер носа второго промежуточного сумматора соединен с входом переноса первого промежуточного сумматора, выход переноса которого соединен с входом переноса первого сумматора откоррек- тированных сумм, вход второго слагаемого которого соединен с выходом переноса второго сумматора откорректированных сумм, вход переноса которого соединен с выходом переноса треть го сумматора откорректированных сумм вход переноса которого соединен с . выходом переноса четвертого сумматора откорректированных сумм, выходы сумматоров откорректированных сумм с первого по четвертый соединены с информационными входами соответственно регистров с первого по четвертый блока выходных регистров, выходы регистров с первого по третий блок вы- ходных регистров соединены с входами вторых слагаемых соответственно второго, третьего и четвертого сумматоров откорректированных сумм, выходы регистров с четвертого по шесто блока выходных регистров соединены с

информационными входами регистров соответственно с пятого по седьмой блока выходных регистров, выходы седьмого регистра блока выходных регистров соединены с третьими входами элементов ИЛИ четвертой группы, выходы регистров с второго по четвертый блока выходных регистров являются выходами вычисляемой функции устройства, вход запуска которого соединен с одноименным входом блока управления, четвертый и пятый выходы которого соответственно соединены с входами стробирования занесения и выборки аргумента, регистра аргумента, шестой и седьмой выходы блока управле- ния соединены соответственно с входами младших разрядов адреса второго блока памяти констант аппроксимации, восьмой выход блока управления соединен с входом стробирования сборки регистра константа, девятый и деся- тьй выходы блока управления соединены с входами соответственно стробиро- вания умножения и разрешения выборки умножителей старшего, среднего, младшего байтов, одиннадцатый выход блока управления соединен с синхронизирующими входами регистров с первого по седьмой блока выходных регистров, двенадцатый выход блока управле ния соединен с входом стробирования выборки седьмого регистра блока выходных регистров.

| 1979 |

|

SU826324A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Смолов В.Б | |||

| Функциональные преобразователи инфopмaциИi -Л.; Энерго- издат, 1981, с.144, рис.4,4а. | |||

Авторы

Даты

1988-03-23—Публикация

1986-05-15—Подача