Изобретение относится к в 1числи- тельной технике и может быть исполь зовано при отладке программ на ЭВМ в режиме реального времени.

Цель изобретения - повышение быстродействия устройства.

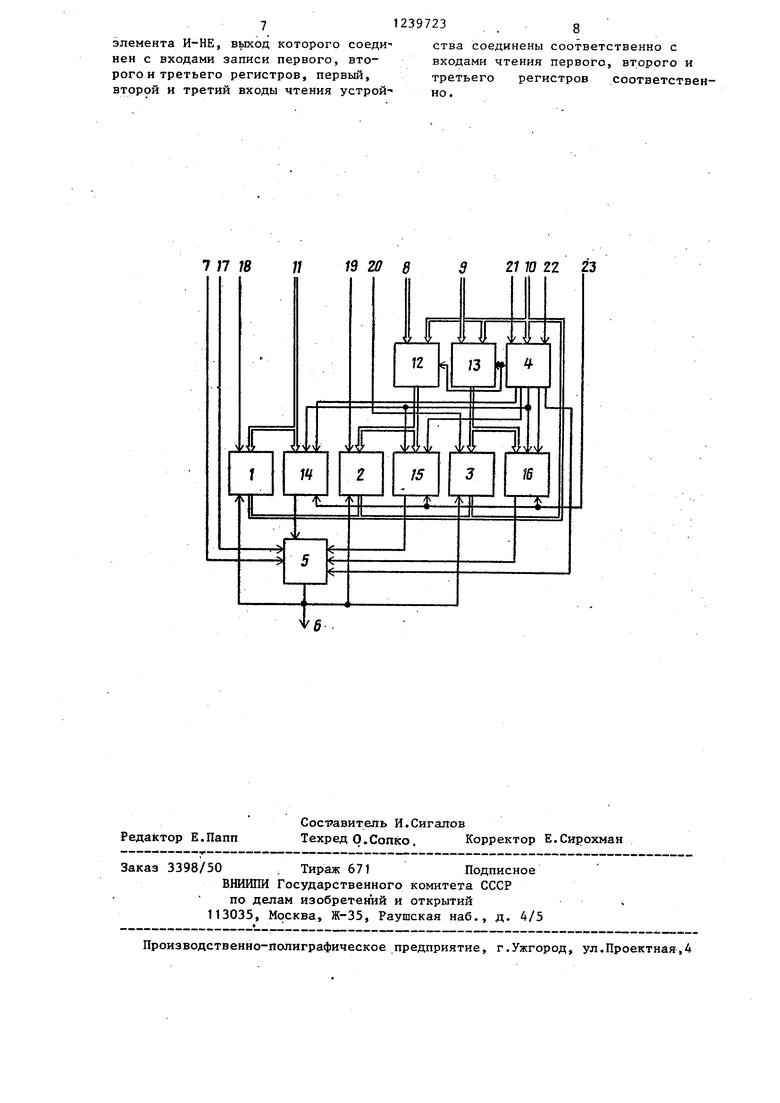

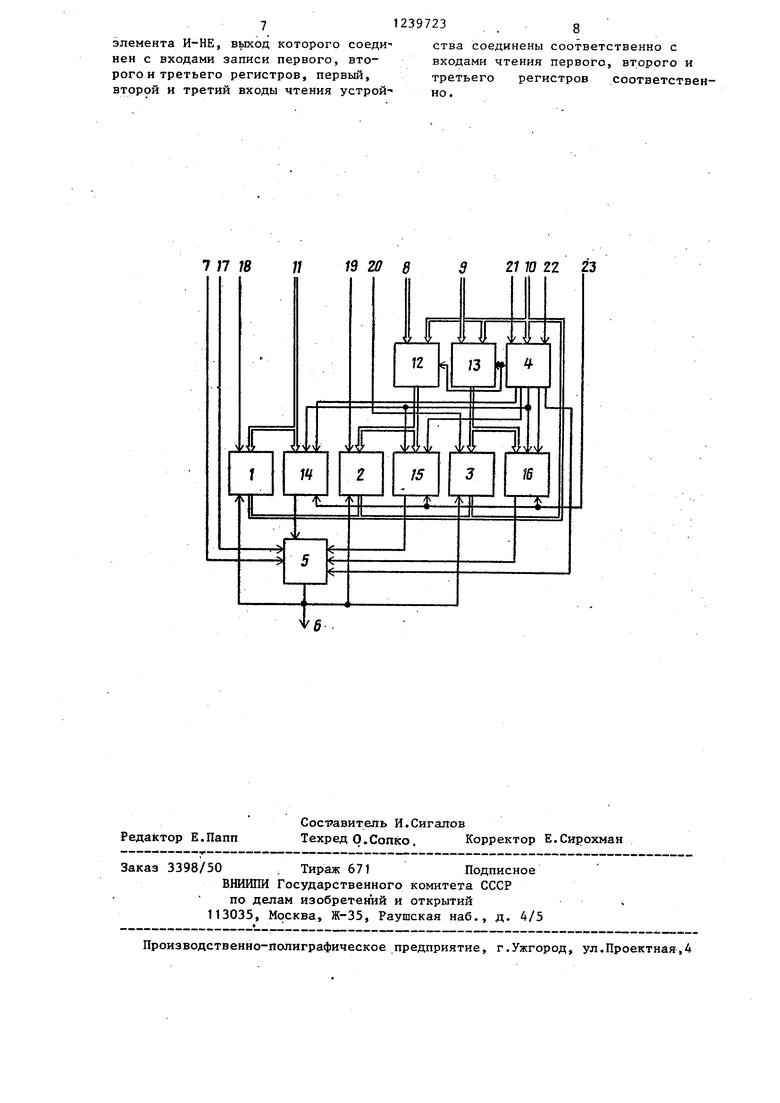

.На чертеже изображено устройство для прерывания при отладке программ.

В его состав входят первый 1, второй 2 и третий 3 регистры, регистр 4 управляющего слова, элемента И-НЕ . 5, выход 6 устройства, тактовый вход 7 стробирования устройства, первые 8 и вторые 9 адресные входы устройства, первые 10 и вторые 11. информационные входы устройства. Устройство содержит также первый 12 и второй 13 мультиплексоры, первый 14, второй 15 и третий 16 блоки памяти, вход 17 разрешения устройства, первый 18, второй 19 и третий 20 входы чтения устройства, вход 21 сброса устройства, первый 22 и второй 23 входы записи устройства.

Возможность задания произвольного числа точек прерываний обеспечивается введением трех блоков 14-16 памяти, каащът и которых хранит часть вектора прерыва ния (точки останова). Часть вектора прерьшания отображается на адрес блока памяти, этому адресу свидетельствует о том, что данная часть вектора принадлежит заданному множеству векторов. Совокупность.трех блоков памяти формирует информацию о принадлежности текущего состояния адресных и информа-г:-. ционных входов устройства к заданному множеству йекторов. Для восьмиразрядных данных и 16-разрядного адреса требуются блоки памяти емкостью 256x1 каждый. Блок 14 фиксирует часть вектора, определяющего тип машинного цикла, а блоки 15 и 16-адресную часть вектора. Мультиплексоры 12 и 13 введены для возможности подключения к адресным входам ЗУ либо информации с адресных входов устройства, либо сигналов с информационных входов. Последнее необходимо при начальной . загрузке блоков памяти заданным набором векторов прерывания. Элемент РШИ-НЕ 5 объединяет сигналы с вькодов блоков памяти и (ггактовьй сигнал с входа 7, а также сигнал запрет/разрешение с выхода регистра 4. Остальные три регистра (1-3) необходимы для воз- можности фиксации значения прервавшего ,вектора, по которому происходит пре

рывание (совпадение текущего состояния входов устройства с заданным набором векторов прерывания). Состояние регистров 1-3 можно прочитать.

Устройство подключается, например к микроэвм, и обеспечивает автоматическое слежение за работой процессора. Перед началом отладки программы устройство программируется путем записи в блоки 14-16 заданного набора векторов прерьшания. В регистр 4 записывается соответствующее управляющее слово, задающее режим работы (табл.1) .

Таблица 1

Выходы регистра 4

Режим работы

1 О 1 - -

0,0 О О О о Начальное состояние

000с Ь а Режим записи в блоки 14-16 данных а Ь, (; Соответственно; f Разрешение прерывания по заданным точкам останова (разрешение работы устройства в режиме слеже-; ния)

Разрешение пошаго-; вой отладки.

1 1 1 - - - - - - Запрет прерывания (запрет работы устройства в режиме слежения)

5

В табл.1 выход 1 - входные данные для блока 14; выход 2 - входные данные для блока 15; выход 3 - входные данные для блока 16; выход 4 - управление мультиплексорами 12 и 13; вькод -5 - запрет/разрешение блоков 14-16; выход 6 -запрет/разрешение выхода прерьтания (блокировка вьжо- да 6). Запись в регистр 4 осуществляется по входу 22 (командой вывода в порт)..

Устройство подключается к микро- ЭВМ своими входами и выходом. Дцрес- ные входы 8 и 9 и первые информаци- 5 онные входы 10 устройства подключа- j ются к адресной и информационной шине микроэвм, информационные входы 11 подключаются непосредственно к инфор-.

0

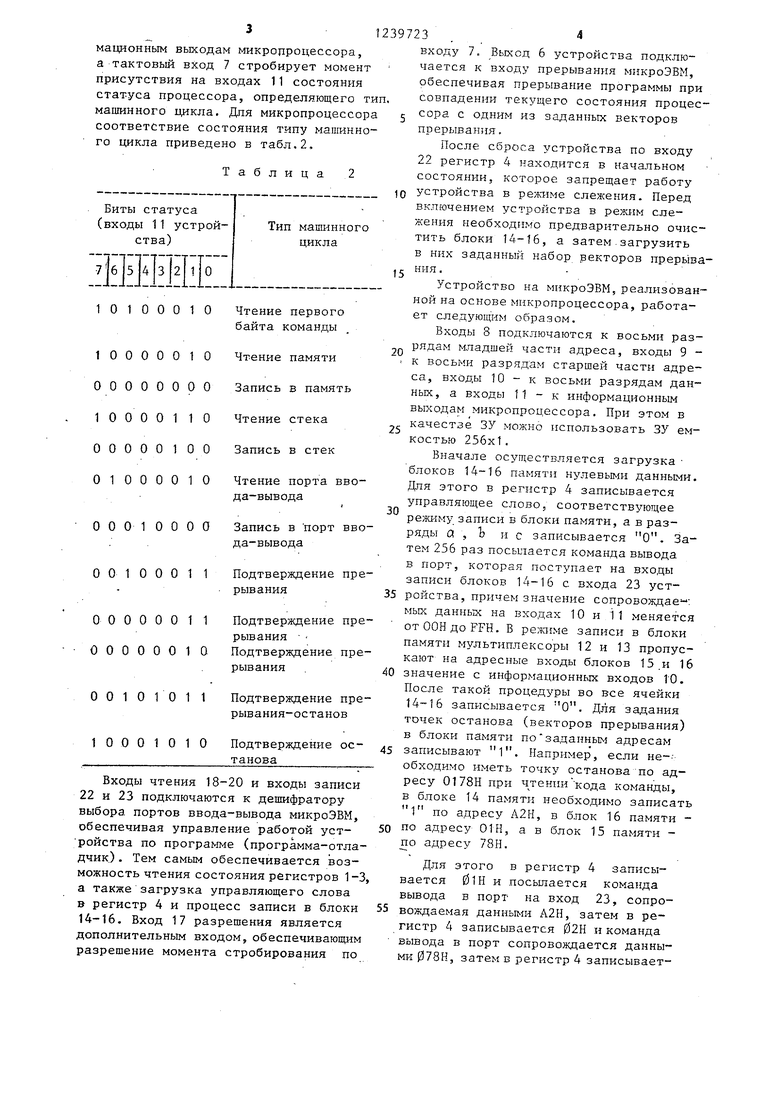

мационным выходам микропроцессора, а тактовый вход 7 стробирует момент присутствия на входах 11 состояния статуса процессора, определяющего тип, машинного цикла. Для микропроцессора соответствие состояния типу машинного цикла приведено в табл.2.

Таблица 2

Чтение первого байта команды

Чтение памяти Запись в память Чтение стека Запись в стек

Чтение порта ввода-вывода

Запись в порт ввода-вывода

Подтверждение прерывания

Подтверждение прерыванияПодтверждение прерывания

Подтверждение прерывания-ос танов

Подтверждение останова

Входы чтения 18-20 и входы записи 22 и 23 подключаются к дешифратору выбора портов ввода-вывода микроЭВМ, обеспечивая управление работой уст- ройства по программе (программа-отладчик.) . Тем самым обеспечивается возможность чтения состояния регистров 1-3, а также загрузка управляющего слова в регистр 4 и процесс записи в блоки 14-16. Вход 17 разрешения является дополнительным входом, обеспечивающим разрешение момента стробирования по

5

0

входу 7, Выход 6 устройства подключается к входу прерывания iикpoЭBM, обеспечивая прерывание программы при совпадении текущего состояния процес- g сора с одним из заданных векторов прерывания.

После сброса устройства по входу 22 регистр 4 находится в начальном состоянии, которое запрещает работу

Q устройства в режиме слежения. Перед включением устройства в режим слежения необходимо предварительно очистить блоки 14-16, а затем загрузить в них заданный набор векторов прерывания .

Устройство на микроЭВМ, реализованной на основе микропроцессора, работает следующим образом.

Входы 8 подключаются к восьми разрядам младшей части адреса, входы 9 - к восьми разрядам старшей части адреса, входы 10 - к восьми разрядам данных, а входы 11 - к информационным выходам микропроцессора. При этом в

J качестзе ЗУ можно использовать ЗУ емкостью 256x1.

Вначале осуществляется загрузка блоков 14-16 памяти нулевыми данными. Для этого в регистр 4 записывается управляющее слово, соответствующее режиму записи в блоки памяти, а в разряды а , Ь и с записывается О. Затем 256 раз посьшается команда вывода в порт, которая поступает на входы записи блоков 14-16 с входа 23 уст5 ройства, причем значение сопровождав : мьгх данных на входах 10 и 11 меняется отООНдоРГН. В режиме записи в блоки памяти мультиплексоры 12 и 13 пропускают на адресные входы блоков 15.и 16

0 значение с информационных входов 10. После такой процедуры во все ячейки 14-16 записывается О. Для задания точек останова (векторов прерывания) в блоки памяти по заданным адресам

5 записывают 1. Например, если не-- обходимо иметь точку останова по адресу 0178Н при чтении кода команды, в блоке 14 памяти необходимо записать 1 по адресу А2Н, в блок 16 памяти 0 по адресу 01Н, а в блок 15 памяти - по адресу 78Н.

Для этого в регистр 4 записывается 01Н и посьшается команда вывода в порт на вход 23, сопро- 5 вождаемая данными А2Н, затем в регистр 4 записывается 02Н и команда вывода в порт сопровождается данными 078Н, затем в регистр 4 записывает0

10

20

25

5 1239723

ся 4Н и командавывода в порт соЪ- ровождается данными 1Н. Таким же образом записываются остальные точки останова. После записи всех заданных точек останова в регистр 4 записывается состояние, разрешающее режим лежения с прерыванием по точкам останова. При этом на выход мультиплексоров 12 и 13 передается состояние адресных входов устройства. При совпадении текущего состояния входов устройства с одной из заданных точек останова на выходах всех трех блоков памяти появляется 1, что приводит к появлению импульса на выходе 6 устройства во время действия сигнала на входе 7 устройства. -Сигнал с выхода 6 подается на вход прерывания микроэвм. Тем самым осуществляется переход к подпрограмме обработки прерывания, т.е. в данном случае - к программе-отладчику.

Так как блоки 14-16 памяти не олностью эмулируют ассоциативную

амять, возможны паразитные точки станова. Это возникает за счет пеесечения точек останова в одной из трех восьмиразрядных частей Для исключения влияния .паразитньк точек останова используются регистры 1-3, в которых в момент прерывания фиксируется значение прерывающего вектора После каждого прерывания по точкам останова можно читать состояние регистров 1-3 и сверять их с заданными векторами. Если прерывающий вектор не попадает в область заданных векторов, то он игнорируется.

Если а регистр 4 записать состояние, соответствующее режиму пошаго-вой отладки (трассировки по каждой команде) , то прерывания будут происходить после каждой комадды. Если задать точки останова, которые возможны только при ошибочной работе программы то имэе тся возможность фиксировать - ошибки в работе программ.

Таким образом, использование пред лагаемого изобретения позволяет значительно сократить время отладки, так как позволяет в одном прогоне задавать различные векторы прерывания.

и т щег вых дом 5 вхо

30

40

45

50

тра соо вхо ю щ шен ны пер при ных 15 пер

вхо рог вхо дин онн тип ных сло вых ров ных инф ра бл мул ре и ро мул инф ги тре рег с у рог рег ми тье и ш го вхо рог вхо дом вто нен и т уст ной сло инф рог нен вер

35

Формула изобретения

Устройство для формирования ; запросов на прерывание при отладке программ, содержащее первый, второй

и третий регистры, регистр управляющего слова и элемент И-НЕ, причем выход элемента И-НЕ соединен с выходом прерывания устройства, тактовый 5 вход устройства и- первый ВЬЕХОД регис10

20

5

0

0

5

0

тра управляющего слова соединены соответственно с первым и вторым входами элемента И-НЕ, о т л и ч а- ю щ е е с я тем, что, с целью повы- шения быстродействия, в него введены первьш и второй мультиплексоры, первый, второй и третий блоки памяти, причем первая и вторая группы адресных входов устройства соединены с 15 первыми группами информационных

входов соответственно первого и второго мультиплексоров, первая группа входов задания данных устройства соединена с вторыми группами информационных входов первого и второго мультиплексоров, с группой информационных входов регистра управляющего слова и с группами информационных выходов, второго и третьего регистг ров, вторая группа входов задания данных устройства соединена с группами информационных входов первого регистра и группой адресных входов первого блока памяти, группа выходов первого мультиплексора соединена с группой адресных входов второго блока памяти и группой информационных входов второго регистра , группа выходов второго мультиплексора соединена с группой - информационньсх входов третьего регистра и группой адресных входов третьего блока памяти, второй выход регистра управляющего слова соединен с упрааляющими входами первого и второго -мультиплексоров, третий выход регис тра управления соединен с входами обращения первого, второго и третьего блоков памяти, четвертьй, пятый и шестой выходы регистра управляющего слова соединены с информационными входами соответственно первого, второго и третьего блок.ов памяти, первый вход записи устройства соединен с входом записи регистра управляющего слова второй вход записи устройства соединен с входами записи первого, второго и третьего блоков памяти, вход сброса устройства соеданен с входом начаггь- ной установки регистра управляющего слова, вход обращения устройства, и информационные выходы первого, второго и третьего блоков памяти соединены соответственно с третьим, чет- вертьпч, пятым и шестым входами

5

71239723 - 8

элемента И-НЕ, вькод которого соеди- ства соединены соответственно с нен с входами записи первого, вто- входами чтения первого, второго и рогои третьего регистров, первый, третьего регистров соответствен- второй и третий входы чтения устрой- но.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования прерывания при отладке программ | 1985 |

|

SU1305680A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1996 |

|

RU2110833C1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| ЦИФРОВОЙ ОТЛАДОЧНЫЙ КОМПЛЕКС | 2021 |

|

RU2773696C1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

Изобретение относится к области вьиислительной техники и может быть применено в устройствах для отладки программ. Целью изобретения является повышение быстродействия при отладке программ за счет появления возможности задания практически любого числа точек прерывания для всех возможных типов мапшнного цикла процессора. Тем самым появляется возможность обеспечивать программные вставки и режим трассировки программ. Поставленная цель достигается введением двух мультиплексоров и трех однообразных блоков памяти. 1 ил. ISD со со vj N9 00

7 17 18 П 19 20 8

21 Ю 22 23

Редактор Е.Папп

Сос-равитель И.Сигалов

Техред О.Сопко. Корректор Е.Сирохман

Заказ 3398/50 , Тираж 671Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная,4

| Устройство для отладки программ | 1979 |

|

SU849218A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для прерывания при отладке программ | 1980 |

|

SU962945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-23—Публикация

1984-03-22—Подача