Изобретение относится к вычислительной технике и может быть использовано при отладке программ на ЭВМ в режиме реального времени.

Цель изобретения - повышение быстродействия устройства.

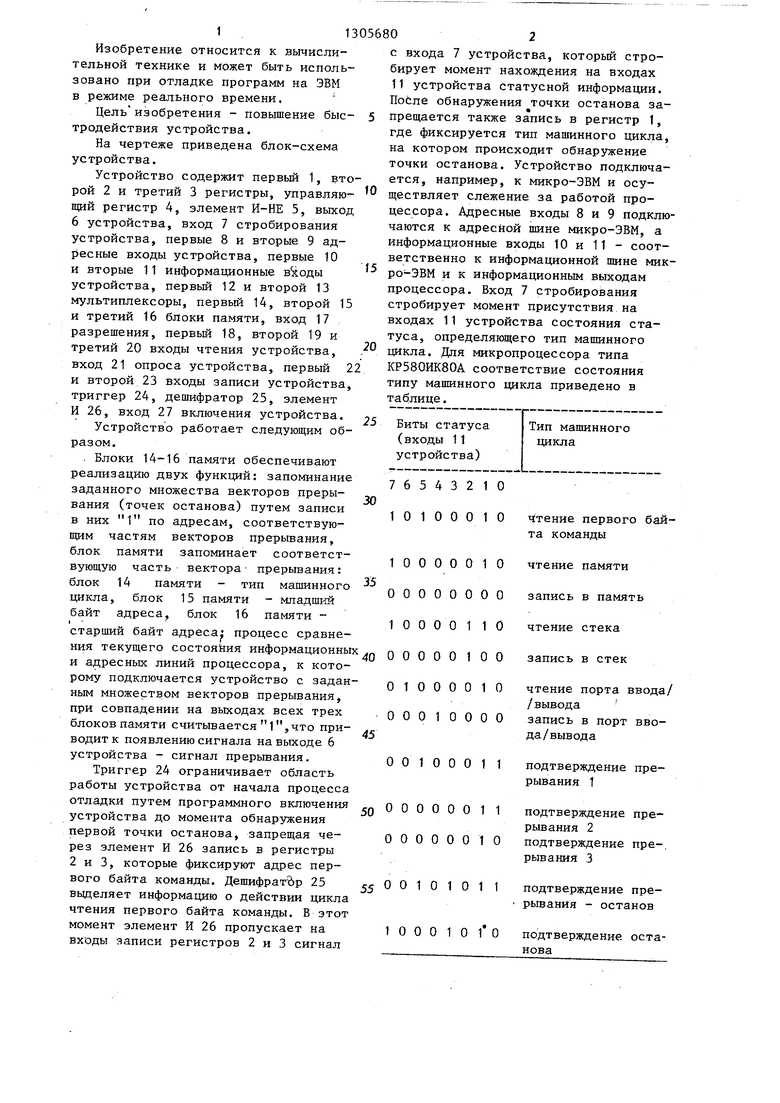

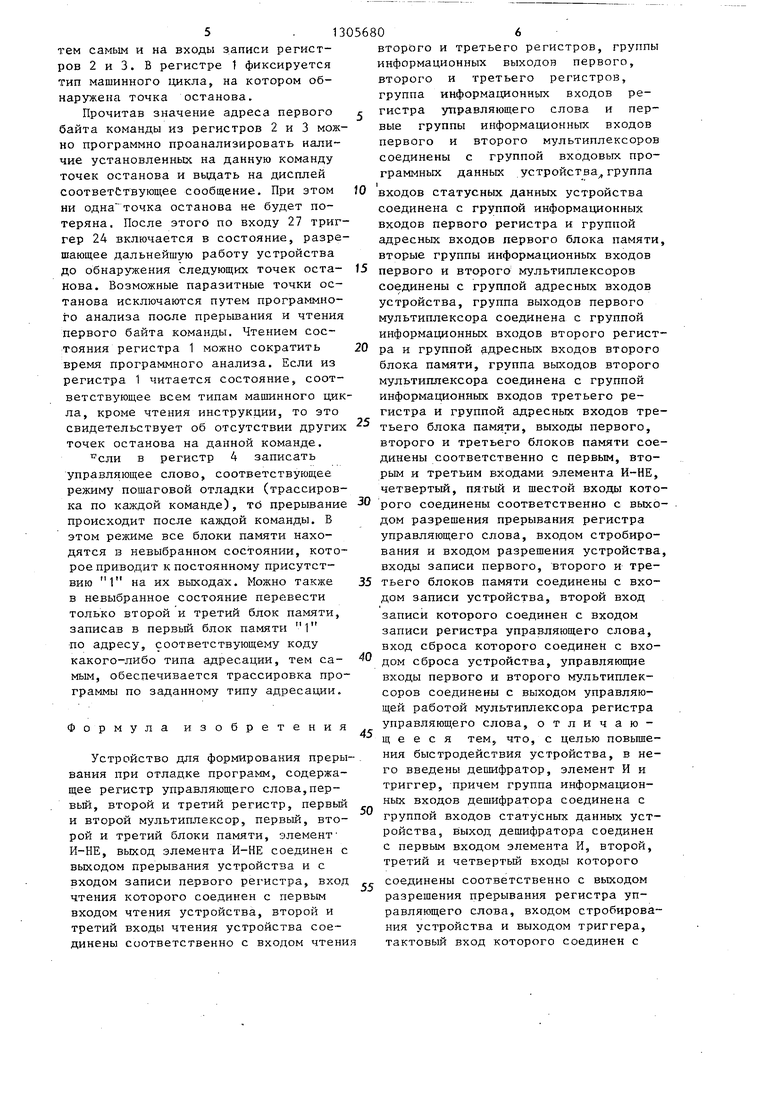

На чертеже приведена блок-схема устройства.

Устройство содержит первый 1, второй 2 и третий 3 регистры, управляющий регистр 4, элемент И-НЕ 5, выход 6 устройства, вход 7 стробирования устройства, первые 8 и вторые 9 адресные входы устройства, первые 10 и вторые 11 информационные в5соды устройства, первый 12 и второй 13 мультиплексоры, первый 14, второй 15 и третий 16 блоки памяти, вход 17 разрешения, первый 18, второй 19 и третий 20 входы чтения устройства, вход 21 опроса устройства, первый 2 и второй 23 входы записи устройства, триггер 24, дешифратор 25, элемент И 26, вход 27 включения устройства.

Устройство работает следующим образом.

. Блоки 14-16 памяти обеспечивают реализацию двух функций: запоминание заданного множества векторов прерывания (точек останова) путем записи в них 1 по адресам, соответствующим частям векторов прерывания, блок памяти запоминает соответствующую часть вектора прерывания: блок 14 памяти - тип машинного цикла, блок 15 памяти - младший байт адреса, блок 16 памяти - старший байт адреса: процесс сравнения текущего состояния информационны и адресных линий процессора, к которому подключается устройство с заданным множеством векторов прерывания, при совпадении на выходах всех трех блоков памяти считывается 1,что приводит к появлению сигнала на выходе 6 устройства - сигнал прерывания.

Триггер 24 ограничивает область работы устройства от начала процесса отладки путем программного включения устройства до момента обнаружения первой точки останова, запрещая через элемент И 26 запись в регистры 2 и 3, которые фиксируют адрес первого байта команды. Дешифрат р 25 выделяет информацию о действии цикла чтения первого байта команды. В этот момент элемент И 26 пропускает на входы записи регистров 2 и 3 сигнал

5

0

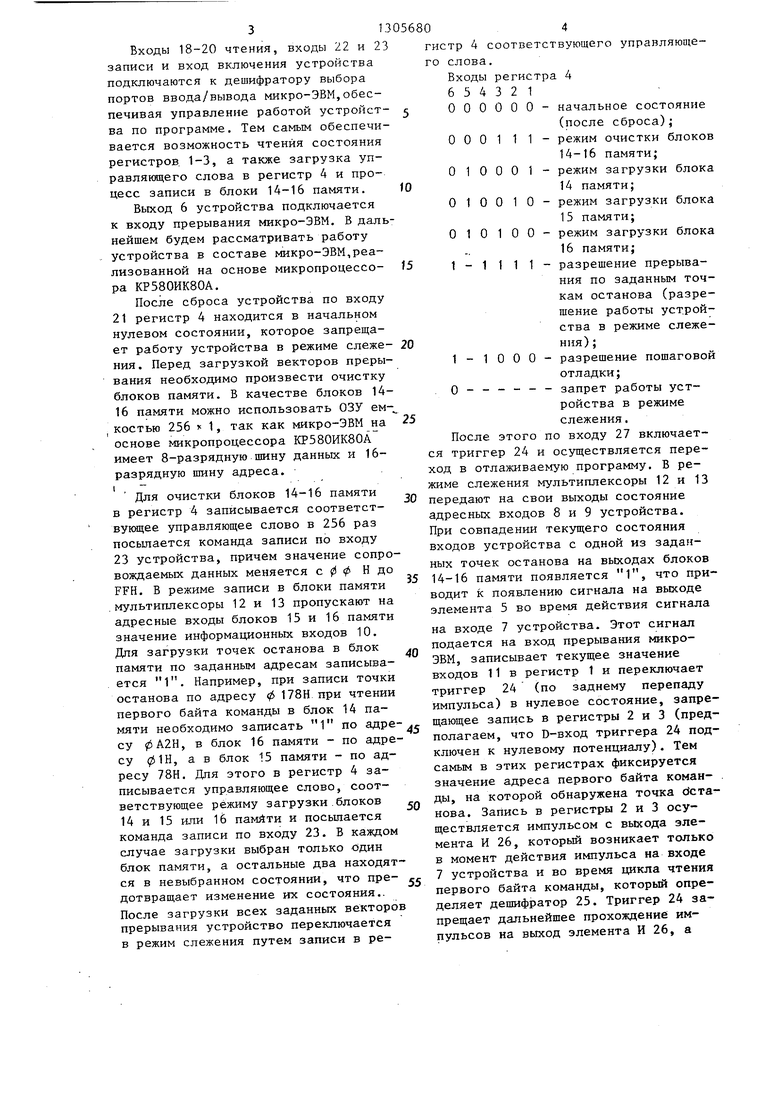

с входа 7 устройства, который стро- бирует момент нахождения на входах 11 устройства статусной информации. После обнарзжения точки останова запрещается также запись в регистр 1, где фиксируется тип машинного цикла, на котором происходит обнаружение точки останова. Устройство подключается, например, к микро-ЭВМ и осуществляет слежение за работой процессора. Адресные входы 8 и 9 подключаются к адресной шине микро-ЭВМ, а информационные входы 10 и 11 - соответственно к информационной шине микро-ЭВМ и к информационным выходам процессора. Вход 7 стробирования стробирует момент присутствия на входах 11 устройства состояния статуса, определяющего тип машинного цикла. Для микропроцессора типа КР580ИК80А соответствие состояния типу машинного цикла приведено в таблице.

5

0

5

00010000

0010001 1

00000011

00000010

0010101 1

10001010

/вывода запись в порт ввода/вывода

подтверждение прерывания 1

подтверждение прерывания 2

подтверждение пре-. рывания 3

подтверждение прерывания - останов

подтверждение останова

Входы 18-20 чтения, входы 22 и 23 записи и вход включения устройства подключаются к дешифратору выбора портов ввода/вывода микро-ЭВМ,обеспечивая управление работой устройства по программе. Тем самым обеспечивается возможность чтения состояния регистров. 1-3, а также загрузка управляющего слова в регистр 4 и процесс записи в блоки 14-16 памяти.

Выход 6 устройства подключается к входу прерывания микро-ЭВМ, В дальнейшем будем рассматривать работу устройства в составе микро-ЭВМ,реализованной на основе микропроцессора КР580ИК80А.

После сброса устройства по входу 21 регистр 4 находится в начальном нулевом состоянии, которое запрещает работу устройства в режиме слежения. Перед загрузкой векторов прерывания необходимо произвести очистку блоков памяти. Б качестве блоков 14- 16 памяти можно использовать ОЗУ ем- костью 256 X 1, так как микро-ЭВМ на основе микропроцессора КР580ИК80А имеет 8-разрядную шину данных и 16- разрядную шину адреса.

Для очистки блоков 14-16 памяти в регистр 4 записывается соответствующее управляющее слово в 256 раз посьшается команда записи по входу 23 устройства, причем значение сопровождаемых данных меняется с ф ф Н до FFH. В режиме записи в блоки памяти мультиплексоры 12 и 13 пропускают на адресные входы блоков 15 и 16 памяти значение информационных входов 10. Для загрузки точек останова в блок памяти по заданным адресам записывается 1. Например, при записи точки останова по адресу ф 178Н при чтении первого байта команды в блок 14 памяти необходимо записать 1 по адресу А2Н, в блок 16 памяти - по адресу 01Н, а в блок 15 памяти - по адресу 78Н. Для этого в регистр 4 записывается управляющее слово, соответствующее режиму загрузки .блоков 14 и 15 или 16 памйти и посылается команда записи по входу 23. В каждом случае загрузки выбран только йдин блок памяти, а остальные два находятся в невыбранном состоянии, что предотвращает изменение их состояния.. После загрузки всех заданных векторов прерывания устройство переключается в режим слежения путем записи в ре10

15

0

5

0

5

0

5

0

5

0100010100100101001-11111-10000

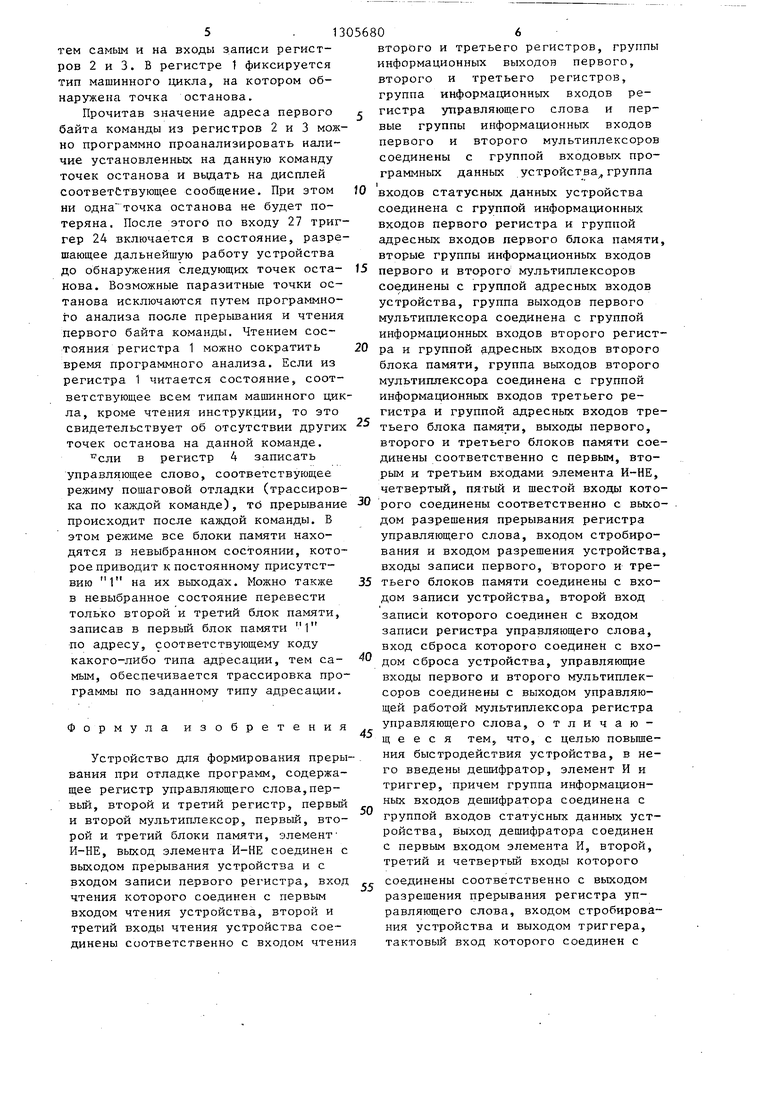

гистр 4 соответствующего управляющего слова.

Входы регистра 4

654321

О О О О О О - начальное состояние

(после сброса)j

О О О 1 1 1 - режим очистки блоков 14-16 памяти; режим загрузки блока

14памяти;

режим загрузки блока

15памяти;

режим загрузки блока

16памяти;

разрешение прерывания по заданным точкам останова (разрешение работы устройства в режиме слежения) ;

разрешение пошаговой отладки;

запрет работы устройства в режиме слежения.

После этого по входу 27 включается триггер 24 и осуществляется переход в отлаживаемую программу. В режиме слежения мультиплексоры 12 и 13 передают на свои выходы состояние адресных входов 8 и 9 устройства. При совпадении текущего состояния входов устройства с одной из заданных точек останова на выходах блоков 14-16 памяти появляется 1, что приводит к появлению сигнала на выходе элемента 5 во время действия сигнала

на входе 7 устройства. Этот сигнал подается на вход прерывания микро- ЭБМ, записывает текущее значение входов 11 в регистр 1 и переключает триггер 24 (по заднему перепаду импульса) в нулевое состояние, запрещающее запись в регистры 2 и 3 (предполагаем, что D-вход триггера 24 подключен к нулевому потенциалу). Тем самым в этих регистрах фиксируется значение адреса первого байта команды, на которой обнаружена точка йота- нова. Запись в регистры 2 и 3 осуществляется импульсом с выхода элемента И 26, который возникает только в момент действия импульса на входе 7 устройства и во время цикла чтения первого байта команды, который определяет дешифратор 25. Триггер 24 запрещает дальнейшее прохождение импульсов на выход элемента И 26, а

тем самым и на входы записи регистров 2 и 3. В регистре 1 фиксируется тип машинного , на котором обнаружена точка останова.

Прочитав значение адреса первого байта команды из регистров 2 и 3 можно программно проанализировать наличие установленных на данную команду точек останова и выдать на дисплей соответствующее сообщение. При этом ни одна точка останова не будет потеряна. После этого по входу 27 триггер 24 включается в состояние, разрешающее дальнейшую работу устройства до обнаружения следующих точек останова. Возможные паразитные точки останова исключаются путем программного анализа после прерьшания и чтения первого байта команды. Чтением состояния регистра 1 можно сократить время программного анализа. Если из регистра 1 читается состояние, соответствующее всем типам машинного цикла, кроме чтения инструкции, то это свидетельствует об отсутствии других точек останова на данной команде, ели в регистр 4 записать управляющее слово, соответствующее режиму пошаговой отладки (трассировка по каждой команде), то прерывание происходит после каждой команды. В этом режиме все блоки памяти находятся в невыбранном состоянии, которое приводит к постоянному присутствию 1 на их выходах. Можно также в невыбранное состояние перевести только второй и третий блок памяти, записав в первьш блок памяти 1 по адресу, соответствующему коду какого-либо типа адресации, тем самым, обеспечивается трассировка программы по заданному типу адресации.

Формула изобретения

Устройство для формирования прерывания при отладке программ, содержащее регистр управляющего слова,первый, второй и третий регистр, первый и второй мультиплексор, первый, второй и третий блоки памяти, элемент- И-НЕ, выход элемента И-НЕ соединен с выходом прерывания устройства и с входом записи первого регистра, вход чтения которого соединен с первым входом чтения устройства, второй и третий входы чтения устройства соединены соответственно с входом чтени

5

0

5

второго и третьего регистров, группы информационных выходов первого, второго и третьего регистров, группа информащ онных входов регистра управляющего слова и первые группы информационных входов первого и второго мультиплексоров соединены с группой входовых программных данньк устройства группа I входов статусных данных устройства

соединена с группой информационных входов первого регистра и группой адресных входов первого блока памяти, вторые группы информационных входов первого и второго мультиплексоров соединены с группой адресных входов устройства, группа выходов первого мультиплексора соединена с группой информационных входов второго регистра и группой адресных входов второго блока памяти, группа выходов второго мультиплексора соединена с группой информационных входов третьего регистра и группой адресных входов третьего блока памяти, выходы первого, второго и третьего блоков памяти соединены соответственно с первым, вто- рьм и третьим входами элемента И-НЕ, четвертый, пятый и шестой входы которого соединены соответственно с выходом разрешения прерывания регистра управляющего слова, входом стробиро- вания и входом разрешения устройства, входы записи первого, второго и тре- 5 тьего блоков памяти соединены с входом записи устройства, второй вход записи которого соединен с входом записи регистра управляющего слова, вход сброса которого соединен с входом сброса устройства, управляющие входы первого и второго мультиплексоров соединены с выходом управляющей работой мультиплексора регистра управляющего слова, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены дешифратор, элемент И и триггер, причем группа информационных входов дешифратора соединена с группой входов статусных данных устройства, выход дешифратора соединен с первым входом элемента И, второй, третий и четвертый входы которого

соединены соответственно с выходом разрешения прерывания регистра управляющего слова, входом стробирова- ния устройства и выходом триггера, тактовый вход которого соединен с

0

0

5

0

5

713056808

выходом элемента И-НЕ, вход сбросавторой и третий выходы загрузки ре- триггера соединен с входЪм сбросагистра управляющего слова соединены устройства, вход установки триггерасоответственно с входами выбора пер- соединен с входом включения устрой- .вого, второго и третьего блоков паства, выход триггера соединен с седь- мяти, а выход записи точки останова мым входом элемента И-НЕ, выход эле-регистра управляющего слова соединен мента И соединен с входами записис информационными входами первого,

второго и третьего регистров, первый,второго и третьего блоков памяти.

(

Составитель Г.Пономарева Редактор Г.Гербер Техред л.ОлеЙник Корректор А.Зимокосов

Заказ 1452/46 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

.Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для формирования запросов на прерывание при отладке программ | 1984 |

|

SU1239723A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

Изобретение может найти применение в вычислительной технике при отладке программ на ЭВМ в режиме реального времени. Цель изобретения - повьшение надежности устройства. Устройство содержит регистры 1-3,управляющий регистр 4, элемент И-НЕ 5, первый и второй мультиплексоры 12 и 13, блоки памяти 14-15, осуществляющие запоминание заданного множества векторов прерывания путем записи в них логической 1 по адресам, соответствующим част ям векторов прерывания. Триггер 24 ограничивает область работы устройства от начала процесса отладки путем программного включения устройства до момента обнаружения первой точки останова, запрещая через элемент И 26 запись в регистры 2 и 3, которые фиксируют адрес первого байта команды. Дешифратор 25 вьщеляет информацию о действии цикла чтения первого байта команды. 1 ил. i с 9 ю 2J гг 23

| Устройство для прерывания при отладке программ | 1984 |

|

SU1171799A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство, СССР 1239723, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-06-13—Подача