ФигЛ

Изобретение относится к вычислительной техклке средствам отображения информации и микросхемотехнике и может быть использовано в счетньЬ схемах различных устройств.

Цель изобретения расширение области применения и повышение помехоустойчивости.

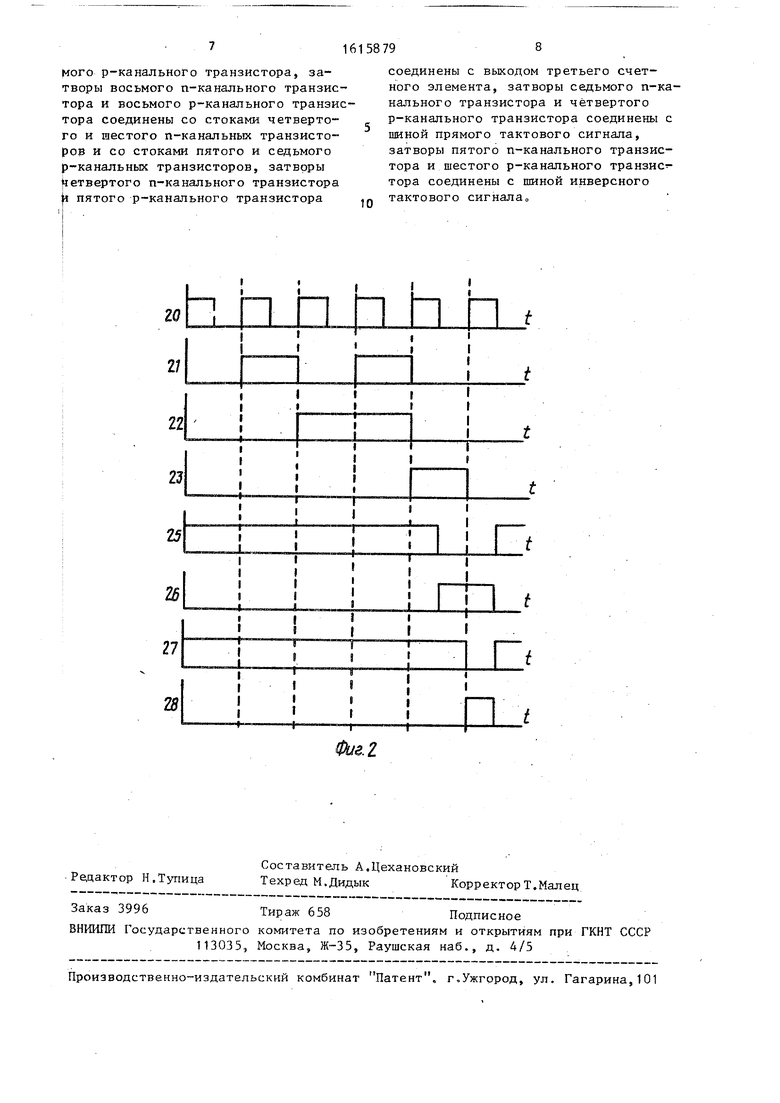

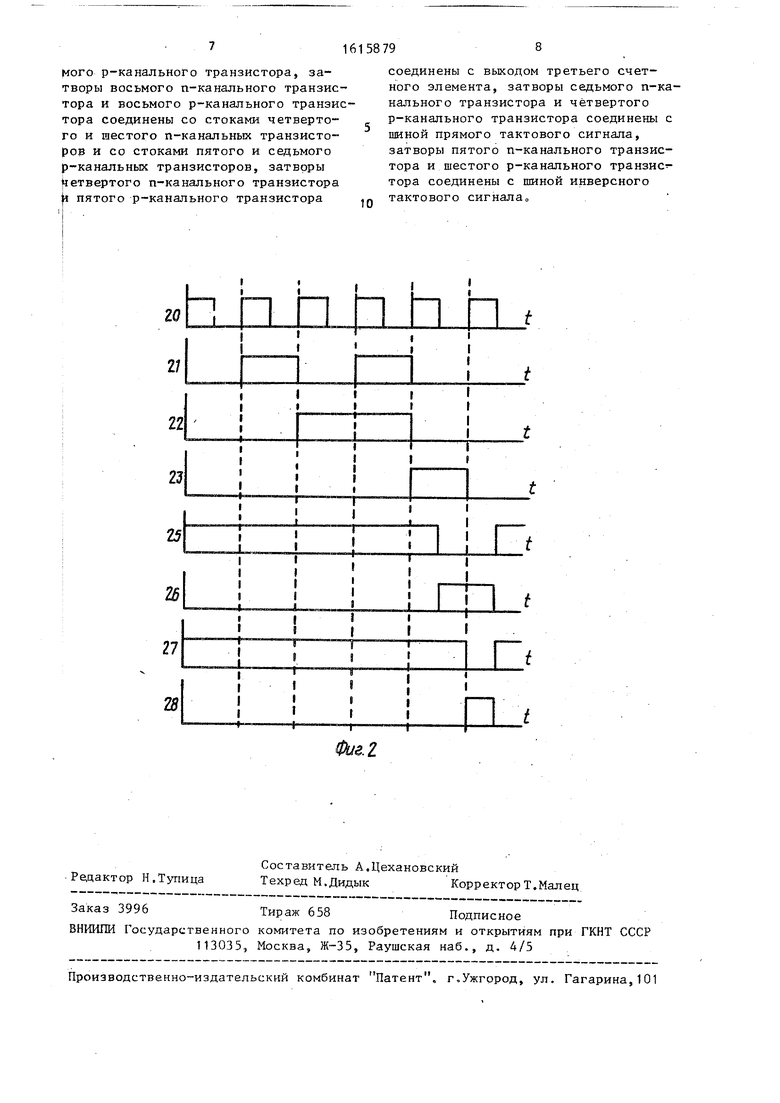

На фиг, 1 представлана электри-, ческая схема счетчика, на фиг 2 временные диаграммы работы счетчика

I

Счетчик содержит три счетных элемента 1-3, три п-канальных транзистора 4-6, два р канальнык транзисто- ipa 7 и 8, третий 9, четвертьй 10 лятьш 11, шестой 12, седьмой 13, :восьмой 14 р-канальные транзисторы, четвертый 15, пятьш 16, шестой 17;. |седьмой 18, восьмой 19 п-канальные |транзисторЫ5 первьй вход первого счетного элемента 1 соединен с шиной 20 прямого тактового сигнала, второй :вход первого счетного элемента 1 соединен с вторыми входами счетньк |элементов 2 и 3 и стоками п-канально )Го и р канапьного транзисторов 6 и 8 |Выходы 21 и 22 первого 1 и второго :2 счетных элементов соединены с пер выми входами второго 2 и третьего 3 счетных элементов соответственно, сток п-канального транзистора 5 соединен с истоком п канального тран :зистора 45 стоки п-канального транзистора 4 и .р-канального транзистора 7 соединены с затворами п-канапьис |го транзистора 6 и р канального транзистора .8 5 истоки р-канапьных транзисторов 7 и 8 соединены с шиной питания, затвор третьего р-канального транзистора 9 соединен с затвором третьего п-канального транзистора 5 и шиной 20 прямого тактового сигнала исток третьего р-канального транзистора 9 соединен с шиной питания, сток третьего р-канального транзистора 9 соединен со стоками п-канально го 4 и р-канального 7 транзисторовэ истоки п-канальных транзисторов 16, 18 и 19 соединены с общей шиной истоки п-канапьнык транзисторов 15 и 17 со стоками п-канапь- ных транзисторов 16 и 18 соответственно, истоки р канальных транзис Го - ров 10, 12 и 14 соединены с шиной питанияS истоки р-канальных транзис- TdpoB 11 и 13 соединены со стоками р-канальных транзисторов 10 и 12 соответственно, стоки п-ханального 19

0

5

0

0

и р-канального 14 транзисторов соединены с затворами п-канального 4 и р-канального 7 транзисторов, с затво- п-канального 17 и р-канального 13 транзисторов, затворы п-канального 19 и р-канального 14 транзисторов соединены со стоками п-канальных транзисторов 15 и 17 и со стоками р-канальных транзисторов 11 и 13, затворы п-канального 15 и р-канального 11 транзисторов соединены с выходом 23 третьего счетного элемента 3, затворы п-канального 18 и р-канального 10 транзисторов соединены с шиной 20 прямого тактового сигнала, затворы п-канального 16 и р-канального 12 транзисторов соединены с шиной 24 инверсного тактового сигнала

Счетчик работает следующим образом.

На вход 20 подается тактовый сигнал произвольной частоты (фигИ) и запускает цепочку счетных элементов ., которые функционируют согласно диаграмме на фиг, 2. Данная цепочка рассчитана на формирование комбинаций из m возможных Поэтому по окончании периода тактового сигнала не- Ьбходим сброс счетных элементов в начальное состояние.

Допустим, цепочка формирует пять комбинатл й по выводам 21-23 (таблица)

Ь5 е ч а н и е, 1 высокий О

I. низкий уровень

5

При этом длительность всех комбинаций должна бьггь в принципе одинаковой Описанные схемы указанной возможностью не обладают, так как при подобной организации данная цепочка счетных элементов либо сбрасывается по периоду в исходное состояние (при появлений на выходе 23 сигнала I), либо держит на выходе 23 сигнал 1 еще три периода. Схема реализует требуемую возможность следуюпцм образом. Введен в схему сброса D-триггер, образуемый транзисторами 10-19, При появлении на входе триггера (точка 23) сигна- ла Г он не инвертируется, так как транзистор 16 закрыт инверсным тактовым сигналом, а транзистор 10 прямым тактовым сигналом В то же время транзисторы 12 и 18 открыты тактовьми сигналами противопаложной полярности. Таким образом транзисторы 10, 11, 1-5 и 16 поддерживают в точке состояние высокого выходного сопротивления а транзисторы 12, 135. 17 и 18 поддерживают там инверсный сигнал с выхода инвертора образованного транзисторами 14, 19, т.е. D-триггер хранит пред.ьиущую информацию. При появлении на транзиторах 12 и 16 инверсного тактового сигнала, а на транзисторах 10 и 18 прямого тактового сигнала, точка 24 открываетсл со стороны транзисторов 10, 11, 15 и 16 и закрывается со стороны транзисторов 12, 13, 17 и 18. Щэоисходит запись новой информации в триггер. Следую1иий полутгериод шестого периода информахщя хранится, она же (дважды инвертированная) появится на выходе инвертора, образованного транзисторами 14 и 19 (точка 25). Далее ока поступает на вход элемента И-ПЕ, образованного транзисторами 4, 5, 7 и 9. В момент прихода первого подупериода шестого периода в точке 26 появится сигнал №i3Koro уровня длительностью половины периода тактового сигнала. Сигнал инвертируется (транзисторы 6 и 8) 5 и на шине 2 появляется сигнал сброса длительностью половины пе- риода тактового сигнала, Счетные эхдементы возвращаются в исходное со- стояние и в момент следующей записи D-триггера в него запишется О, т.е сигнал сброса не вырабатывается до появления на выходе 28 1. Кроме возможности одинаковой длитепьности после-довательностн комбинации необходимой в системах отображения инфор- э,ции5 схема позволяет выполнять и другие функции. Так, задавая длительность каждого пятого периода тактового сигнала, можно добиться произвапьной длительности и пятой комбинаггии.

79 Фор к у л

и 3

б г е т е н к я

15

20

Счетчик с начальной установкой, 5 содержащий три счетных элемента, три . --канальных транзистора, два р-ка- иальных транзистора, первьй вход первого счетного элемента соединен с шикой прямого тактового сигнала, to второй вход первого счетного элемента соединен с вторыми входами осталь- кых счетных элементов и стоками первых п-канального и р-канального транзисторов, выходы первого и второго счетных элементов соединены с первыми входами второго, третьего . счетных элементов соответственно, сток третьего п-канмьного транзистора соединен с истоком второго п-канального транзистора, стоки вто- рыл п-канального и р-канального транзисторов соединены с затворами пэрвьгх п канального и р-канального тра1зисторов, истоки первого и вто- 25 рого р-канального транзисторов соединены с шиной питания, отличающийся тем, что, с целью расширения области применения и повы- помехоустойчивости, в него 30 введены четвертый, пятьй, шестой.

седьмой, восьмой п-канальные транзис- торы, третий, четвертый, пятый, шестой,, седьмой, восьмой р-канальные транзисторы, затвор третьего р-канального транзистора соединен с затвором третьего п-канального транзистора, шиной прямого тактового сигнала, исток третьего р-канального транзистора соединен с шиной питания, сток третьего р-канального транзистора соединен со стоками вторых п-канального и р-канального транзисторов, истоки пятого, седьмого и восьмого п-канальных транзисторов соединены с общей шиной, истоки четвертого и шестого п-канальных транзисторов со- единены со стоками пятого и седьмого п-канальных транзисторов, истоки

третьего,, четвертого и шестого р-ка- 0 нагьных транзисторов соединены с шиной питания, истоки .пятого и седьмого р-канальных транзисторов соединены со стокам четвертого и шестого р-канальных транзисторов, jl стоки восьмого п-канального транзистора и восьмого р-канального транзис™ тора соединены с затворами вторых п- н р-канальных транзисторов, с затворами шестого п-канального и седь35

40

5

Мого р-канального транзистора, затворы восьмого п-канального транзистора и восьмого р-канального транзистора соединены со стоками четвертого и шестого п-канапьных транзисторов и со стоками пятого и седьмого р-канальных транзисторов, затворы Четвертого п-канального транзистора пятого р-канального транзистора

соединены с выходом третьего счетного элемента, затворы седьмого п-канального транзистора и четвертого р-канального транзистора соединены с пиной прямого тактового сигнала, затворы пятого п-канального транзистора и шестого р-канального транзистора соединены с шиной инверсного тактового сигнала

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1986 |

|

SU1372357A1 |

| Сумматор по модулю два | 1984 |

|

SU1191906A1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| Триггер со счетным входом на взаимодополняющих МДП-транзисторах | 1987 |

|

SU1492452A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Управляемый мажоритарный элемент | 1981 |

|

SU993479A1 |

| Логический элемент матричного умножителя | 1986 |

|

SU1352480A1 |

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

Изобретение относится к вычислительной технике, средствам отображения информации и микросхемотехнике и может быть использовано в счетных схемах различных устройств. Цель изобретения - расширение области применения и повышение помехоустойчивости. Счетчик содержит счетные элементы 1, 2, 3, шину 20 прямого тактового сигнала, шину 24 инверсного тактового сигнала, выходные шины 21, 22, 23. Введение P-канальных транзисторов 9-14 и N-канальных транзисторов 15-19, а также шины инверсного тактового сигнала 24 позволяет исключить ложный сброс счетных элементов 1, 2, 3, вызванный гонкой фронтов в счетных элементах или пульсацией напряжения питания, обеспечивает сопряжение с внешними устройствами и одинаковую длительность всех комбинаций счетчика. 2 ил.

te.2

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-12-23—Публикация

1988-10-03—Подача