Изобретение относится к вычислительной технике и может быть использовано для моделирования решения сис«- тем дифференциальных уравнений.

Цель изобретения - расширение функциональных возможностей за счет реализации операции интегрирования.

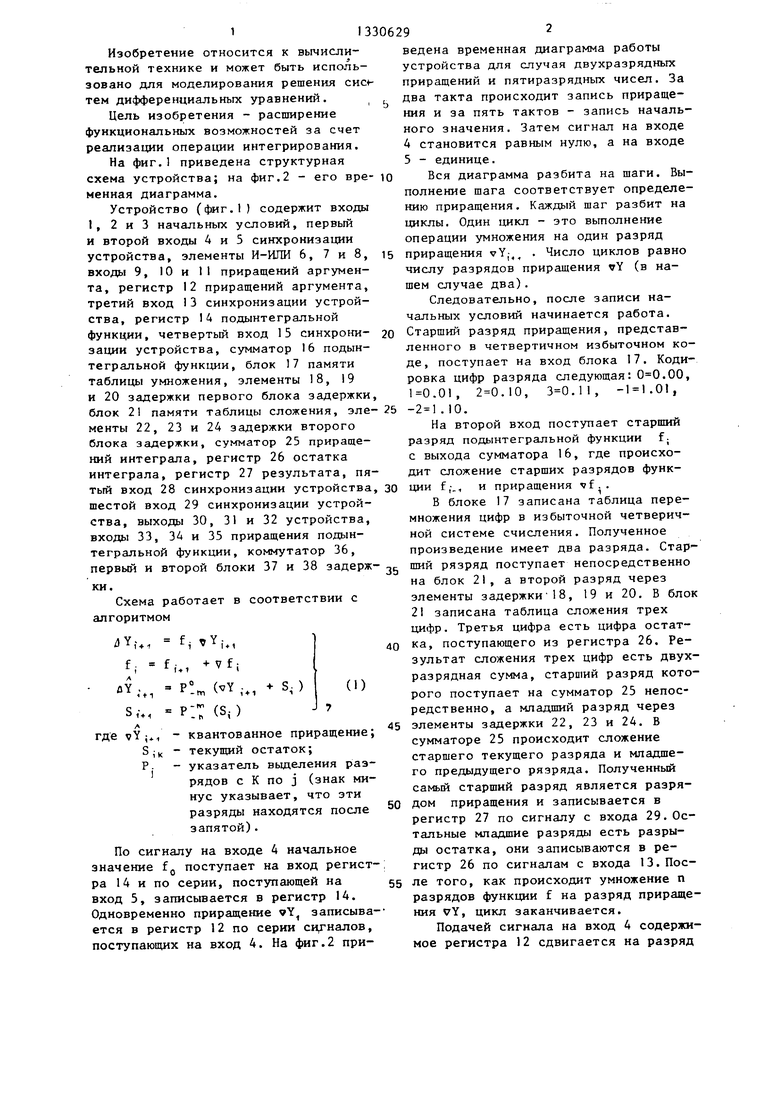

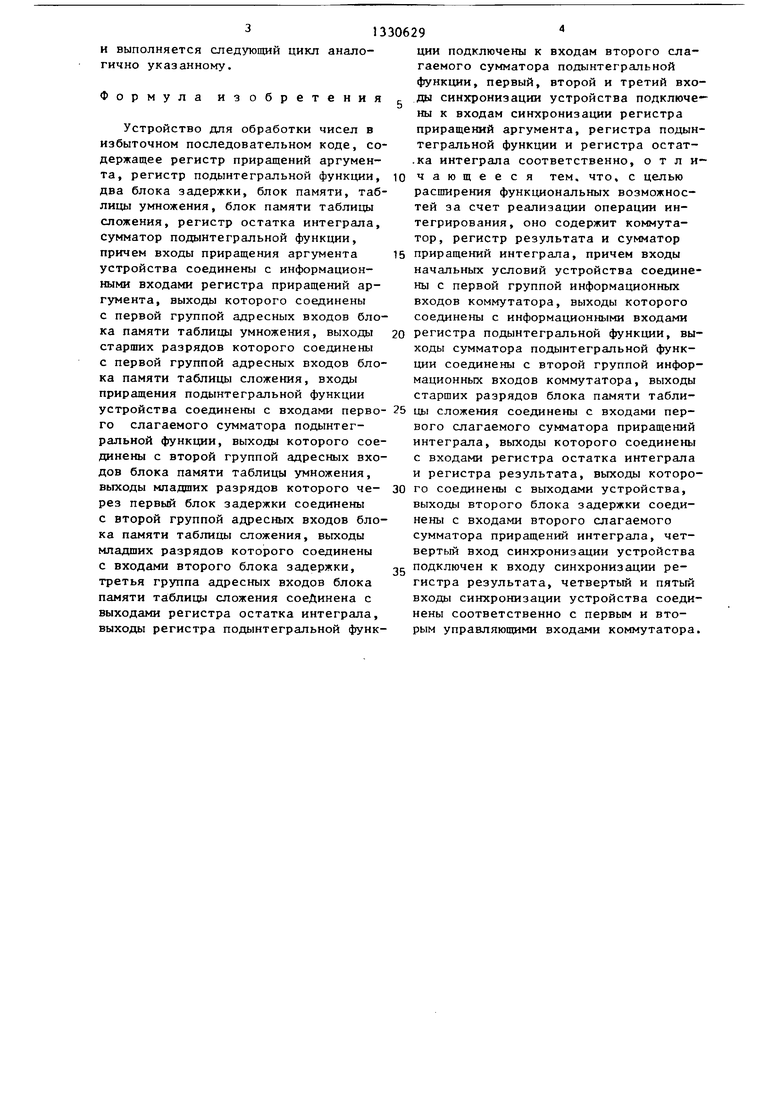

На фиг.1 приведена структурная схема устройства; на фиг.2 - его вре- менная диаграмма.

Устройство (фиг.1) содержит входы 1, 2 и 3 начальных условий, первый и второй входы 4 и 5 синхронизации

устройства, злементы И-ИЛИ 6, 7 и 8, 15 приращения vY,- . Число циклов равно входы 9, 10 и 11 приращений аргумен- числу разрядов приращения vY (в нага, регистр 12 приращений аргумента, третий вход 13 синхронизации устройства, регистр 14 подынтегральной функции, четвертый вход 15 синхрони- 20 зации устройства, сумматор 16 подынтегральной функции, блок 17 памяти таблицы умножения, элементы 18, 19 и 20 задержки первого блока задержки, блок 21 памяти таблицы сложения, эле- 25 .10.

менты 22, 23 и 24 задержки второго На второй вход поступает старший блока задержки, сумматор 25 приращений интеграла, регистр 26 остатка интеграла, регистр 27 результата, пяшем случае два).

Следовательно, после записи начальных условий начинается работа. Старший разряд приращения, представленного в четвертичном избыточном ко де, поступает на вход блока 17. Кодировка цифр разряда следующая: .00, .01, .10, .11, .01,

разряд подынтегральной функции f; с выхода сумматора 16, где происходит сложение старших разрядов функВ блоке 17 записана таблица перемножения цифр в избыточной четверичной системе счисления. Полученное произведение имеет два разряда. Стар

ки.

Схема работает в соответствии с алгоритмом

. i Y,,

fu, Vf;

f,л

aY .

11

S,4, где vY;,;

S;

(vY .,, t- S. )

P:: (S,)

(1)

тый вход 28 синхронизации устройства, ЗО ции f,-., и приращения vf.. шестой вход 29 синхронизации устройства, выходы 30, 31 и 32 устройства, входы 33, 34 и 35 приращения подынтегральной функции, коммутатор 36, первый и второй блоки 37 и 38 задерж- .,ц пшй рязряд поступает непосредственно

на блок 21, а второй разряд через элементы задержки 18, 19 и 20. В блок 21 записана таблица сложения трех цифр. Третья цифра есть цифра остат- 40 ка, поступающего из регистра 26. Результат сложения трех цифр есть двухразрядная сумма, старший разряд которого поступает на сумматор 25 непосредственно, а младший разряд через 45 элементы задержки 22, 23 и 24. В сумматоре 25 происходит сложение старшего текущего разряда и младшего предыдущего рязряда. Полученный самый старший разряд является разря- 50 дом приращения и записывается в

регистр 27 по сигналу с входа 29. Остальные младшие разряды есть разры- ды остатка, они записываются в ре- i гистр 26 по сигналам с входа 13.Пос- 55 ле того, как происходит умножение п разрядов функции f на разряд приращения 7Y, цикл заканчивается.

Подачей сигнала на вход 4 содержимое регистра 12 сдвигается на разряд

Р. квантованное приращение; текущий остаток; указатель вьщеления разрядов с К по j (знак минус указывает, что эти разряды находятся после запятой).

По сигналу на входе 4 начальное значение f поступает на вход регист-; ра 14 и по серии, поступающей на вход 5, записывается в регистр 14. Одновременно приращение vY записыва- ется в регистр 12 по серии сигналов, поступающих на вход 4. На фиг.2 приведена временная диаграмма работы устройства для случая двухразрядных приращений и пятиразрядных чисел. За два такта происходит запись приращения и за пять тактов - запись начального значения. Затем сигнал на входе

4становится равным нулю, а на входе

5- единице.

Вся диаграмма разбита на шаги. Выполнение шага соответствует определению приращения. Каждый шаг разбит на циклы. Один цикл - это вьтолнение операции умножения на один разряд

приращения vY,- . Число циклов равно числу разрядов приращения vY (в на-2 1.10.

шем случае два).

Следовательно, после записи начальных условий начинается работа. Старший разряд приращения, представленного в четвертичном избыточном коде, поступает на вход блока 17. Кодировка цифр разряда следующая: .00, .01, .10, .11, .01,

На второй вход поступает старший

разряд подынтегральной функции f; с выхода сумматора 16, где происходит сложение старших разрядов функВ блоке 17 записана таблица перемножения цифр в избыточной четверичной системе счисления. Полученное произведение имеет два разряда. Стар

ции f,-., и приращения vf.. пшй рязряд поступает непосредственно

(1)

и выполняется следующий цикл аналогично указанному.

Формула изобретения

Устройство для обработки чисел в избыточном последовательном коде, содержащее регистр приращений аргумента, регистр подынтегральной функции, два блока задержки, блок памяти, таблицы умножения, блок памяти таблицы сложения, регистр остатка интеграла, сумматор подынтегральной функции, причем входы приращения аргумента устройства соединены с информационными входами регистра приращений аргумента, выходы которого соединены с первой группой адресных входов блока памяти таблицы умножения, выходы старших разрядов которого соединены с первой группой адресных входов блока памяти таблицы сложения, входы приращения подынтегральной функции устройства соединены с входами перво- го слагаемого сумматора подынтегральной функции, выходы которого соединены с второй группой адресных входов блока памяти таблицы умножения, выходы младщих разрядов которого че- рез первый блок задержки соединены с второй группой адресных входов блока памяти таблицы сложения, выходы младших разрядов которого соединены с входами второго блока задержки, третья группа адресных входов блока памяти таблицы сложения соединена с выходами регистра остатка интеграла, выходы регистра подынтегральной функ

5 0

ции подключены к входам второго слагаемого сумматора подынтегральной функции, первый, второй и третий входы синхронизации устройства подключены к входам синхронизации регистра приращений аргумента, регистра подынтегральной функции и регистра остат- .ка интеграла соответственно, о т л и- чающееся тем. что, с целью расширения функциональных возможностей за счет реализации операции интегрирования, оно содержит коммутатор, регистр результата и сумматор 5 приращений интеграла, причем входы начальных условий устройства соединены с первой группой информационных входов коммутатора, выходы которого соединены с информационными входами регистра подынтегральной функции, выходы сумматора подынтегральной функции соединены с второй группой информационных входов коммутатора, выходы старших разрядов блока памяти таблицы сложения соединены с входами первого слагаемого сумматора приращений интеграла, выходы которого соединены с входами регистра остатка интеграла и регистра результата, выходы которого соединены с выходами устройства, выходы второго блока задержки соединены с входами второго слагаемого сумматора приращений интеграла, четвертый вход синхронизации устройства подключен к входу синхронизации регистра результата, четвертый и пятый входы синхронизации устройства соединены соответственно с первым и вторым управляющими входами коммутатора.

5

13

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| ИНТЕГРАТОР ДЛЯ ПАРАЛЛЕЛЬНОЙ ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ МАШИНЫ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 1973 |

|

SU388278A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1339554A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1042013A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

Изобретение относится к области вычислительной техники и может быть использовано при решении задач моделирования. Цель изобретения - рас- шинение функциональных возможностей. Устройство содержит регистр приращений аргумента, регистр подынтегральной функции, регистр остатка интеграла, регистр результата, два блока задержки, блок памяти таблицы умножения, блок памяти таблицы сложения, сумматор подынтегральной функции и коммутатор. Устройство позволяет реализовать наряду с умножением операции интегрирования. 2 ил. с 9 (Л со со о 05 со

Редактор М.Дылын

Составитель А.Чеканов Техред В.Кадар

Заказ 3583/50Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

fu/erf Фиг 2

Корректор И.Myска

| ФРЕЗЕРНАЯ БАБКА | 0 |

|

SU382482A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения в избыточном последовательном коде | 1983 |

|

SU1173410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-15—Публикация

1985-04-10—Подача