Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях.

Целью изобретения является расширение класса pemaeNbix задач за счёт возможности вычисления квадратного корня в избыточном четвертичном последовательном коде.

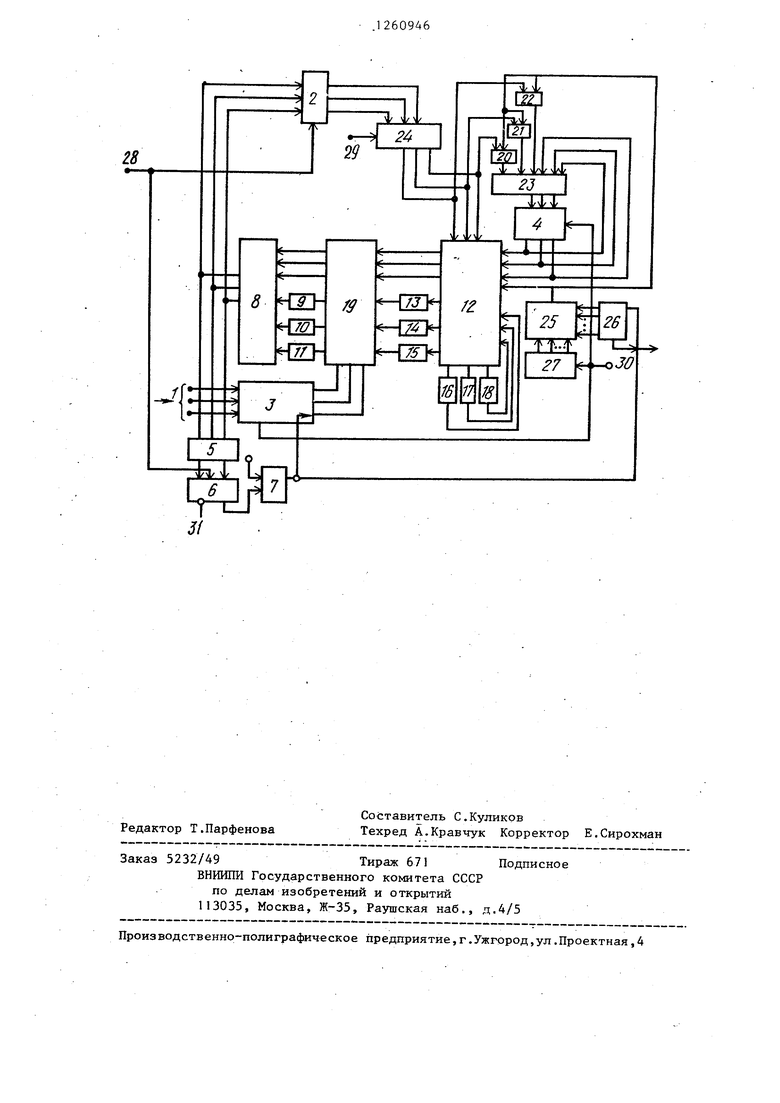

На чертеже представлена функциональная схема устройства.

Устройство содержит входы 1 аргумента, первый регистр 2, второй регистр 3, третий регистр 4, первую схему сравнения 5, триггер 6, элемент И 7, первый сумматор 8, элементы задержки 9-11 первой группы, сумматор-умножитель 12, элементы задержки 13-15 второй группы, элемент задержки 16-18 третьей группы, второй сумматор 19, элементы И 20-22 группы, третий сумматор 23, четвер- тьтй регистр 24, вторую схему сравнения 25, первый счетчик 26, втооой счетчик 27, первый 28, второй 29 и третий 30 тактирующие входы, выход 31 признака останова.

Устройство функционирует следующим образом.

Работает схема в соответствии с алгоритмом

Р-, (с.)

ь, - У,-, vy, - .

17 С - -ir 1, ,. .., tj, 2

(1)

где Р - функция выделения, которая указывает, что в качестве приращения берется старший разряд невязки; fi - текущая невязка. На первом шаге половина аргумента х в четвертичном избыточном коде старшими разрядами вперед поступает на входы 1 аргумента устройства. При прохождении старшего разряда подается сигнал на первый тактирующий вход 28, и значение старшего разряда записывается в первьй регистр 2 и одновременно в триггер 6 признак равенства нулю старшего разряда, которьй формируется первой схемой сравнения 3. После записи во второй регистр 3 всего числа подается сигнал на второй тактирующий вход 29 и, если старший разряд нулевой, то на выходе элемента И 7 формируется сигнал, который сдвигает содержимое регистра

5

3 и прибавл 1ет к содержимому счетчика 26 1. Одновременно по этому сигналу происходит перезапись содержимого регистра 2 в регистр 24. Если старший разрАд не нулевой, то на выходе элемента И 7 не образуется сигнала. На этом нулегой шаг заканчивается. В первом шаге происходит умножение разряда, записанного в ре гистре 24, на величину у, хранимую в регистре 4. Так как при извлечении квадратного корня аргумент предварительно нормализуется, то первый старший разряд всегда не нуль. В регист5 ре 4 записана величина у. . Для , у у 0. Происходит умножение на у . Эта операция выполняется на сумматоре-умножителе 12, в котором реализуются две функции: умноже ние двух четвертичных цифр и прибавление к результату половины квадрата множителя.

Выбор типа операции производится подачей сигнала на вход сумматора-умножителя 12 с выхода второй схемы сравнения 25. Сигнал, равный 1, выбирает вторую операцию, а сигнал, равный нулю, выбирает первую операцию. Это позволяет осуществить операцию (vy. у, + -г vy ). Так как

вес приращения всегда жестко связан с номером корректируемого разряда, то величина l2vy должна появить5 ся только раз в момент прохождения этого разряда. Соответствующее слежение за этим осуществляется с помощью охемы, состоящей из второй схемы сравнения 25 и двух счетчиков 26

40 и 27. В счетчике 26 хранится номер корректируемого разряда, а счетчик 27 указывает время прохождения этого разряда в текущем шаге. При совпадении содержимых счетчиков 26 и

45 27 схема сравнения выдает сигнал, равный единице. В нашем случае (первый шаг) vy. vy. Уд 0 ив первом такте вьшолняется операция

(vy. 0 + 0,2- vy/) 50 Величина 1/2 в четвертичном коде

равна 0,2. При умножении на 0,2 получаем трехразрядное число. Вес первого разряда равен весу текущего разряда, а остальные имеют веса

55 следующих младших разрядов. Произведение равно двухразрядному числу, первый разряд равен весу текущего разряда. Максимальное положительное

число, получаемое при этом, равно

М(0,ЗхО,3+0,2х(0,3)) (0,21+1,102)(0,312). Максимальное отрицательное шсло равно

М (0,2х(-0,2)+0,2х(-0,2) )0,Г20 Для кодирования чисел в избыточной четвертичной системе используются следующие цифры

(,00, 0,6l, .10, ,11, .11, .10).

Как видим, цифры в максимальных по модулю числах не превьшают разрешенного кодирования. Образующийся первый разряд выдается на первый выход, второй разряд на второй выход, а третий разряд на третий выход. Третий разряд задерживается на элементах задержки 16-18 и поступает на вход третьего аргумента сумматора- умножителя 12 в спедующем такте. Цифра этого разряда прибавляется к теТак как величи

кущему произведению

на vy формируется и прибавляется

в разряде, который определяется в данный момент, а все младшие разря- дь1 у. , следующие за ним, равны нулю то добавление цифры по третьему входу не переводит произведение двух цифр :в запрещенное кодирование. Од- повременно при прохождении корректируемого разряда необходимо величину коррекции из регистра 24 прибавить к текущему разряду. Это осуществляется подачей сигнала со схемы сравнения 25 на группу элементов И 20-22, которые открываются, и содержимое регистра 24 и текуш 1й разряд у складываются на сумматоре 23. Полученный скорректированный разряд записы- вается в текущий разряд регистра 4. Первый текуш 1Й разряд произведения двух цифр из сумматора-умножителя I2 поступает на вход второго сумматора, 19, на другой вход поступает второй разряд предыдущего произведения через элементы задержки 13-15, на третий вход сумматора 19 поступает текущий разряд невязки из регистра 2. В сумматоре 19 выполняется следующая операция : ( - (П - S ) , где i . - j - разряд невязки ; ; П первый разряд текущего произведения цифр; S - второй разряд предыдущего произведения. Получаемая сумма не превьшает двух разрядов. Старший разряд непосредственно, а младший через элементы задержки 9-11, что

5

)0

.0

5

0

609А64

позволяет выровнять веса разрядов, поступают на первый сумматор 8, где образуется первое приближение старшего разряда невязки. В следующем такте повторяются все перечисленные операции (за исключением прибавления 1/2 Vy , предполагаем, что происходит отыскание первого старшего разряда корня). После суммирования поступивших цифр Б первом сумматоре 8, если возникает перенос, то он добавляется к предыдущему разряду и формируется окончательное значение старшего разряда невязки, который .поступает на выход сумматора 8.

При выдаче старшего разряда на первый тактирующий вход 28 поступает сигнал, и он записывается в регистр 2. Одновременно результат анализа на нуль старшего разряда со схемы сравнения 5 записывается в триггер 6. Кроме того, старший и после- д пощие разряды новой невязки- записываются по серии С, поступающей со входа 30 в регистр 3. После определения всех п разрядов невязки подается сигнал на вход 29, который сдвигает содержимое регистра 3 в сторону старших разрядов и наращивает счетчик 26 на 1 в случае, если старший разряд был равен нулю в противном случае схема не реагирует на сигнал и в следующем шаге продолжается корректировка этого же разряда

5

35

30 Q j 0

5

у. , Процесс пpoдoJX кaeтcя до определения точного значения разряда, что определяется по равенству нулю старшего разряда невязки. При равенстве нулю старшего разряда происходит сдвиг на разряд невязки. Этот сдвиг увеличивает невязку. Необходимость этого обусловлена тем, что изменяется вес определенного разряда величины у ., он уменьшается. Чтобы не перестраивать схему умножения,можно увеличить вес невязки и тем самым выровнять величины и (у- vy +

1 GL

+ vy. ), кроме того, сдвиг невязки

позволяет определять по старшему раз- . ряду конец определения разряда у, т.е, независимо от того, какой разряд корректируется, временная диаграмма сохраняется. После сдвига регистра 3 происходит пустой шаг (умножение на нуль), В этом шаге определяется первое приближение текущего разряда. Затем производится процесс кор5

ректировки разряда и так далее, пока не будут определены все разряды. Это фиксируется по переполнению счетчика 26, сигнал с которого прекращает поступать на выход 31 и прекращает формирование временной диаграммы,

Формула изобретения

Вычислительное устройство, содержащее два регистра, первую схему сравнения, сумматор-умножитель, два сумматора и две группы элементов задержки, причем выходы первого сумматора соединены с информационными входами первого регистра, входы первого слагаемого первого сумматора соединены с выходами старших разрядов второго сумматора, выходы младших разрядов которого соединены через элементы задержки первой группы с входами второго слагаемого первого сумматора, входы первого слагаемого второго сумматора соединены через элементы задержки второй группы с выходами разрядов второй группы сумматора-умножителя, входы третьего слагаемого второго сумматора соединены с выходами второго регистра, отличающееся тем, что, с целью расщирения класса решаемых задач за счёт возможности вычисления квадратного корня в избыточном четвертичном последовательном коде, в него дополнительно введены третий сумматор, триггер, группа элементов И, элемент И, вторая схема сравнения, два счетчика, третий и четвертый регистры и третья группа элементов задержки, причем вход аргумента устройства соединен с информационными входами первого и второго регистров и первым информационным входом первой схемы сравнения, второй информационный вход которой соединен с шиной логического О устройства.

60946fe

выход равно первой схемы сравнения соединен с входом установки триггера, вход рброса которого соединен с выходом Не равно первой схемы 5 сравнения, выход.триггера соединен с первым входом элемента И, выход которого соединен с входом сдвига второго регистра и счетным входом первого счетчика, выход которого соеди10 нен с первым информационным входом второй схемы сравнения, второй информационный вход которой соединен с выходом второго счетчика, выход Равно второй схемы сравнения сое15 динен с входом управления типом операции сумматора-умножителя и с первым, входами элементов И группы, входы первого операнда сумматора-умножителя соединены с выходами третье20 го регистра и входами первого слагаемого третьего сумматора, входь второго операнда сумматора-умножителя соединены через элементы задержки третьей группы с выходами

5 разрядов третьей группы сумматора- умножителя, входы второго слагаемого третьего сумматора соединены с выходами элементов И группы, вторые входы которых соединены с входами

0 третьего операнда сумматора-умножителя и с выходами четвертого ре- гистра, информационные входы которого соединены с выходами первого регистра, синхронизирующие входы

5 триггера и первого регистра соединены с первым тактир топщм входом устройства, синхронизирующий вход четвертого, регистра и второй вход элемента И соединены с вторым тактирую0 щим входом устройства, третий тактирующий вход которого соединен с синхронизирующими входагФ второго и третьего регистров и со счетным входом второго счетчика, выход перепол5 нения первого счетчика является выходом завершения вычислений устройства .

tf

J/

пУ

Редактор Т.Парфенова

Заказ 5232/49Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

Составитель С.Куликов

Техред А.Кравчук Корректор Е.Сирохман

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления обратной величины | 1984 |

|

SU1241231A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Устройство для обработки чисел в избыточном последовательном коде | 1985 |

|

SU1330629A1 |

| Устройство для вычисления тригонометрических функций тангенса и котангенса | 1980 |

|

SU907545A1 |

| Вычислительное устройство | 1985 |

|

SU1283755A1 |

| Устройство для решения систем алгебраических уравнений | 1986 |

|

SU1324036A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1259259A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

Изобретение относится к вычислительной технике и может быть применено в быстродействующих специализированных вычислителях как автономно, так и в составе.больших ЭВМ в качестве функционального расширителя. Целью изобретения является расширение класса решаемых задач за счет возможности вычисления квадратного корня в избыточной четвертичной системе. Устройство содержит входа аргумента, первый регистр, второй регистр, третий регистр, первую схему сравнения, триггер, элемент И, первый сумматор, элементы задержки пер- вой группы, сумматор-умножитель, элементы задержки второй группы, элементы задержки третьей группы, второй сумматор, элементы И группы, третий сумматор, четвертый регистр, вторую схему сравнения, первый счетчик, второй счетчик, первый, второй и третий тактирующие входы, выход признака останова. Работа устройства основана на итерационном процессе вычисления разрядов значения корня, представленного в избыточном четвертичном последовательном коде. 1 ил. (Л с tsD Од О СО 4 а

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения в избыточном последовательном коде | 1983 |

|

SU1173410A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1986-09-30—Публикация

1985-05-20—Подача