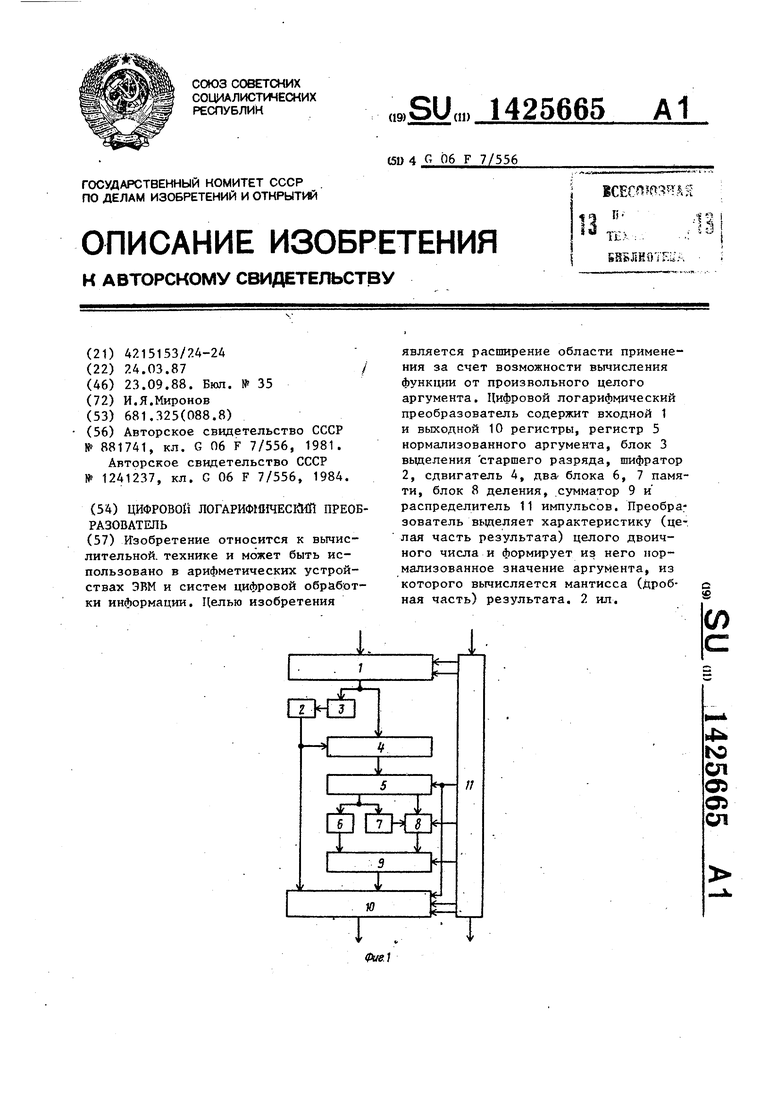

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных вычислителей, информа- ционно-измерительных систем, цифро - вых фильтров, гибридных функциональных преобразователей.

Целью изобретения является расширение области применения за счет возможности вычисления функции от произвольного целого аргумента.

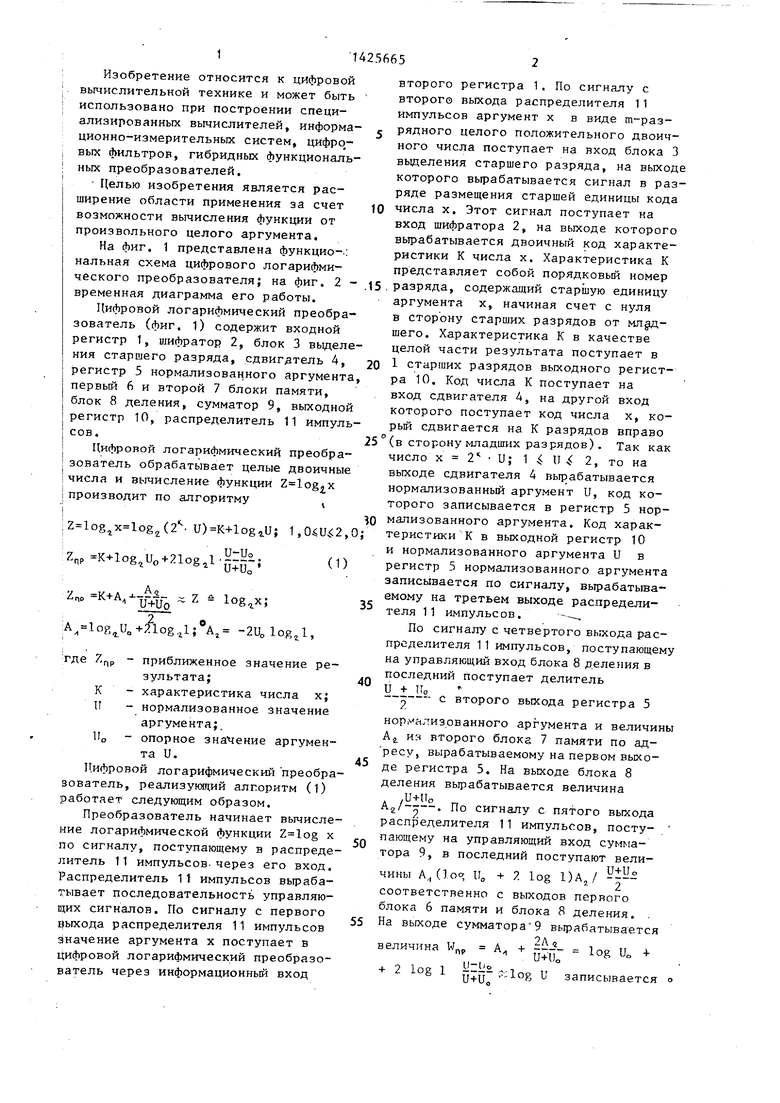

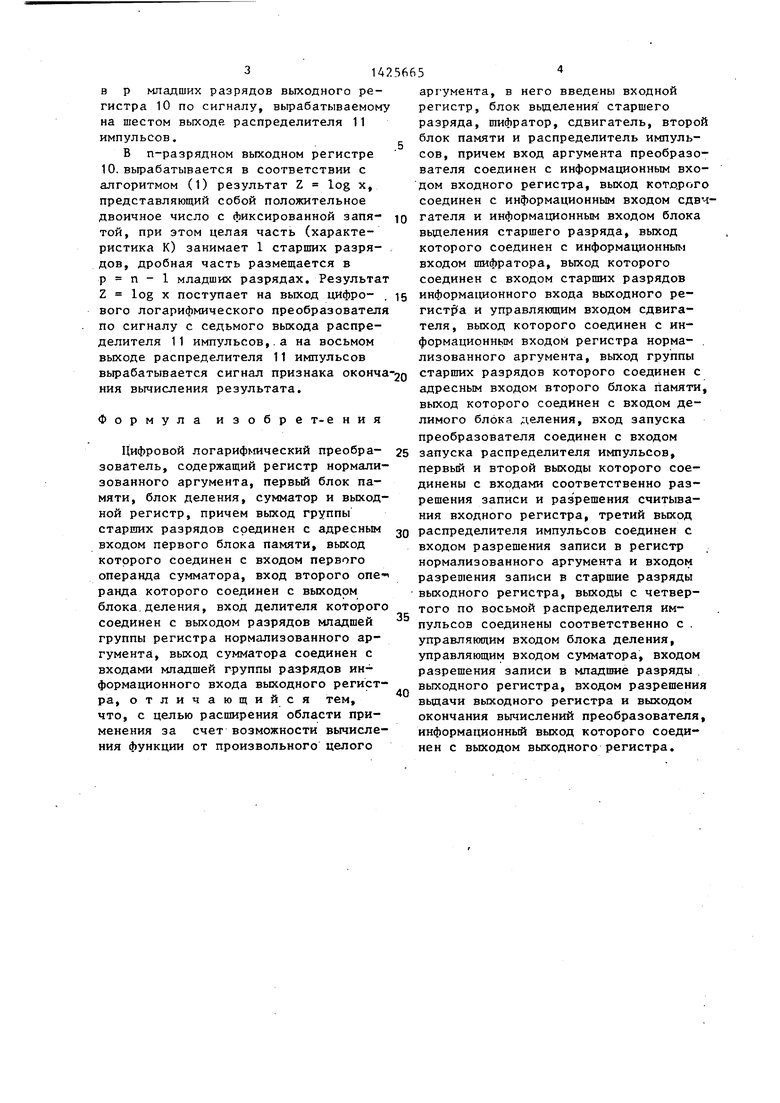

На фиг. 1 представлена функцио.: нальная схема цифрового логарифмического преобразователя; на фиг. 2 - временная диаграмма его работы.

Цифровой логарифмический преобразователь (фиг. 1) содержит входной регистр 1, шифратор 2, блок 3 выделе I ния старшего разряда, сдвиг атель 4, j регистр 5 нормализованного аргумента I первый 6 и второй 7 блоки памяти, I блок 8 деления, сумматор 9, выходной регистр 10, распределитель 11 импуль 1 сов.

I Цифровой логарифмический преобра- I зователь обрабатывает целые двоичные I числа и вычисление функции ,x I производит по алгоритму

I,

|Z lo8 x logJ2 U)K+logiU; 1,,

:Z,p K log Uo-f21ogJ.

(1)

Z,, K+A, Z s

;A 1ой

I.+2

t. °

log.J; A., -2Uc, 1ой,,1,

где Zr,p - приближенное значение результата;К - характеристика числа х; И - нормализованное значение

аргумента;.

HO опорное зна чение аргумента U. Цифровой логарифмический преобразователь, реализующий алгоритм (1) работает следующим образом.

Преобразователь начинает вычисление логарифмической функции х по сигналу, поступающему в распределитель 11 импульсов, через его вход. Распределитель 1t импульсов вырабатывает последовательность управляющих сигналов, rfo сигналу с первого 1 ъкоца распределителя 11 импульсов значение аргумента х поступает в Цифровой логарифмический преобразователь через информационный вход

,

5

0 5

0

5

0

второго регистра 1. Цо сигналу с второго выхода распределителя 11 импульсов аргумент х в виде рядного целого положительного двоичного числа поступает на вход блока 3 вьзделения старшего разряда, на выходе которого вьфабатывается сигнал в разряде размещения старшей единицы кода числа X. Этот сигнал поступает на вход шифратора 2, на выходе которого вьфабатывается двоичный код характеристики К числа X. Характеристика К представляет собой порядковьй номер

. разряда, содержащий старшую единицу аргумента х, начиная счет с нуля в сторону старших разрядов от шего. Характеристика К в качестве целой части результата поступает в 1 старших разрядов выходного регистра 10. Код числа К поступает на вход сдвигателя 4, на другой вход которого поступает код числа х, ко- рьй сдвигается на К разрядов вправо

° (в сторону младших разрядов). Так как число X 2 U; 1 U 2, то на выходе сдвигателя 4 вырабатывается нормализованный аргумент U, код которого записывается в регистр 5 нормализованного аргумента. Код характеристики К в выходной регистр 10 и нормализованного аргумента U в регистр 5 нормализованного аргумента записывается по сигналу, вырабатываемому на третьем выходе распределителя 11 импульсов. .

По сигналу с четвертого выхода распределителя 11 импульсов, поступающему на управляющий вход блока 8 деления в последний поступает делитель и -н

2

1 ° .

-. Q

второго выхода регистра 5

нормализованного аргумента и величины А из второго блока 7 памяти по ад- ресу, вырабатываемому на первом выходе регистра 5. На выходе блока 8 деления вырабатывается величина

л /и+Ио

Ag/---. По сигналу с пятого выхода

распр еделителя 11 импульсов, посту- , пающему на управляющий вход сумматора 9, в последний поступают велиU+Uo

2

соответственно с выходов первого

блока 6 памяти и блока 8 деления. . На вькоде сумматора 9 вырабатывается

чины А, (0 Ио + log 1)А,/ --величина W.,

2 logl Jj;;jf..logu

Ш: °8 и. +

записывается о

3142

в р младших разрядов выходного регистра 10 по сигналу, вырабатываемому на шестом выходе распределителя 11 импульсов.

В п-разрядном выходном регистре 10. вьфабатывается в соответствии с алгоритмом (1) результат Z log х, представляющий собой положительное двоичное число с фиксированной запятой, при этом целая часть (характеристика К) занимает 1 старших разрядов, дробная часть размещается в р п - 1 младших разрядах. Результат Z log X поступает на выход цифрового логарифмического преобразователя по сигналу с седьмого выхода распределителя 11 импульсов,, а на восьмом выходе распределителя 11 импульсов вырабатывается сигнал признака окончания вычисления результата.

Формула изобрет-ения

Цифровой логарифмический преобразователь, содержащий регистр нормализованного аргумента, первый блок памяти, блок деления, сумматор и выходной регистр, причем выход группы старших разрядов соединен с адресным входом первого блока памяти, выход которого соединен с входом первого операнда сумматора, вход второго one- ранда которого соединен с выходом блока.деления, вход делителя которого соединен с выходом разрядов младшей группы регистра нормализованного аргумента, выход сумматора соединен с входами младшей группы разрядов информационного входа выходного регистра, отличающийся тем, что, с целью расширения области применения за счет возможности вычисления функции от произвольного целого

0

5

0

665

аргумента, в него введены входной регистр, блок вьщеления старшего разряда, шифратор, сдвигатель, второй блок памяти и распределитель И1 туль- сов, причем вход аргумента преобразователя соединен с информационным входом входного регистра, выход которого соединен с информационным входом сдвч- гателя и информационным входом блока вьзделения старшего разряда, выход которого соединен с информационным входом шифратора, выход которого соединен с входом старших разрядов информационного входа вькодного ре- гистр а и управляющим входом сдвига- теля, выход которого соединен с ин- формационньтм входом регистра норма- . лизованного аргумента, выход группы старших разрядов которого соединен с адресным входом второго блока памяти, выход которого соединен с входом делимого блока деления, вход запуска преобразователя соединен с входом запуска распределителя импульсов, первый и второй выходы которого соединены с входами соответственно разрешения записи и разрешения считывания входного регистра, третий выход

0 распределителя импульсов соединен с входом разрешения записи в регистр нормализованного аргумента и входом разрешения записи в старшие разряды вькодного регистра, вькоды с четвертого по восьмой распределителя импульсов соединены соответственно с . управляющим входом блока деления, управляющим входом сумматора, входом разрешения записи в младшие разряды выходного регистра, входом разрешения вьщачи выходного регистра и выходом окончания вычислений преобразователя, информационный выход которого соединен с выходом выходного регистра.

5

5

rx «O

Jt

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Устройство для вычисления функции @ | 1985 |

|

SU1305671A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1976 |

|

SU593212A1 |

| Цифровое устройство для логарифми-РОВАНия дВОичНыХ чиСЕл | 1979 |

|

SU813414A2 |

| Устройство для деления | 1981 |

|

SU987621A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

| Устройство для логарифмирования массивов двоичных чисел | 1979 |

|

SU926654A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

Изобретение относится к вычислительной, технике и может быть использовано в арифметических устройствах ЭВМ и систем цифровой обработки информации. Целью изобретения является расширение области применения за счет возможности вычисления функции от произвольного целого аргумента. Цифровой логарифмический преобразователь содержит входной 1 и выходной 10 регистры, регистр 5 нормализованного аргумента, блок 3 вьщеления старшего разряда, шифратор 2, сдвигатель 4, два блока 6, 7 памяти, блок 8 деления, .сумматор 9 и распределитель 11 импульсов. Преобразователь вьщеляет характеристику (целая часть результата) целого двоичного числа и формирует из него нормализованное значение аргумента, из которого вычисляется мантисса (Дробная часть) результата. 2 ил. с (Л го СП о: а сд

«V4

«o.

ro

«Q5s

| Цифровой логарифмический преобразователь | 1979 |

|

SU881741A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для логарифмирования двоичных чисел | 1984 |

|

SU1241237A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-24—Подача