Изобретение относится к автоматике и. контрольно-измерительной технике и может быть использовано при создании автоматических устройств контроля и поиска дефектов в синхронных цифровых схемах,

Цель изобретения - повышешие быстродействия устройства и расширение класса контролируемых объектов .(синхронные последовательные схемы)о

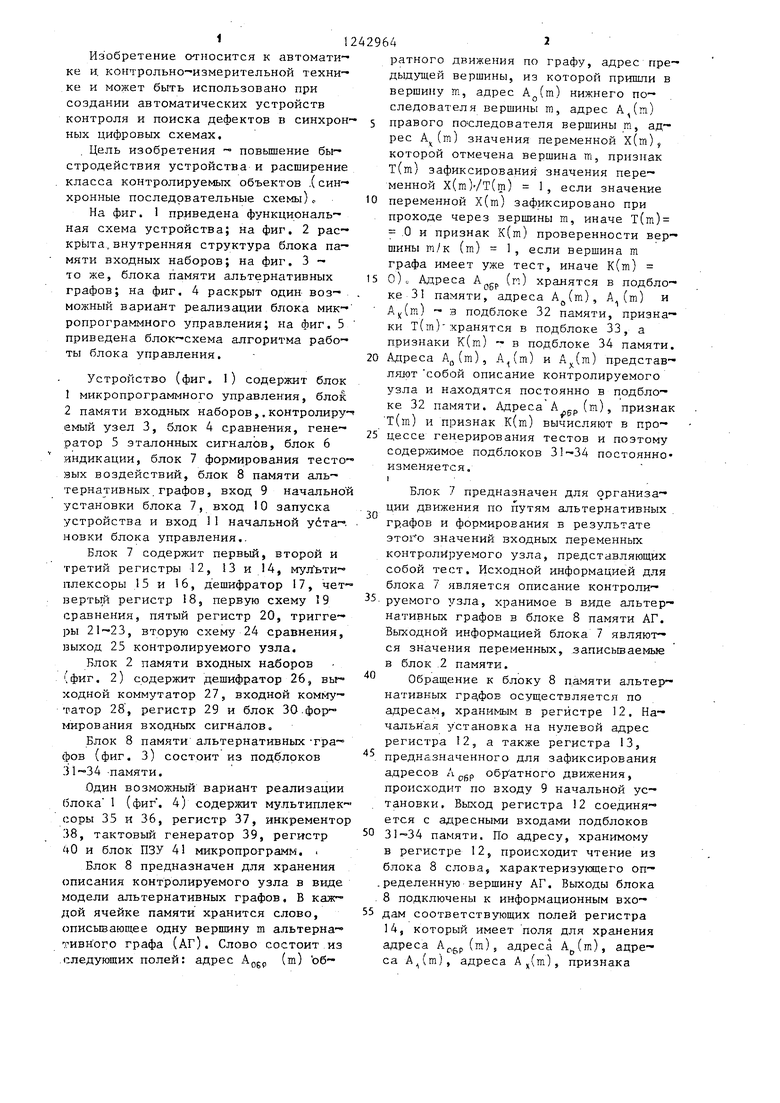

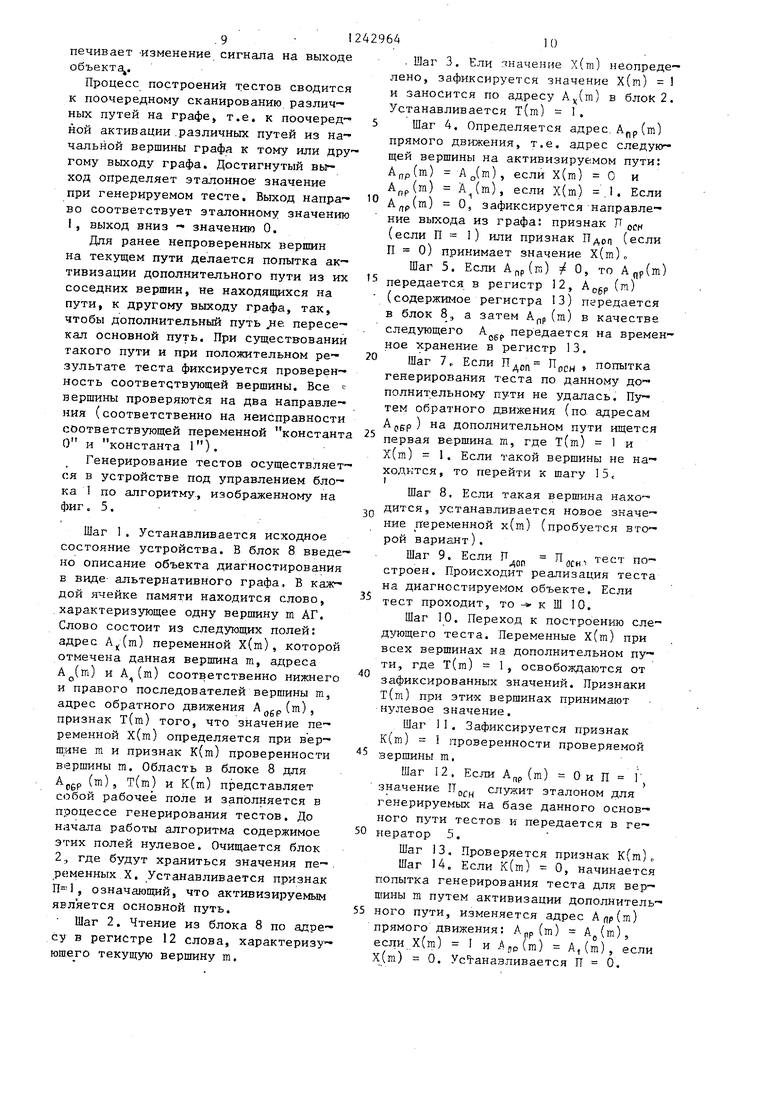

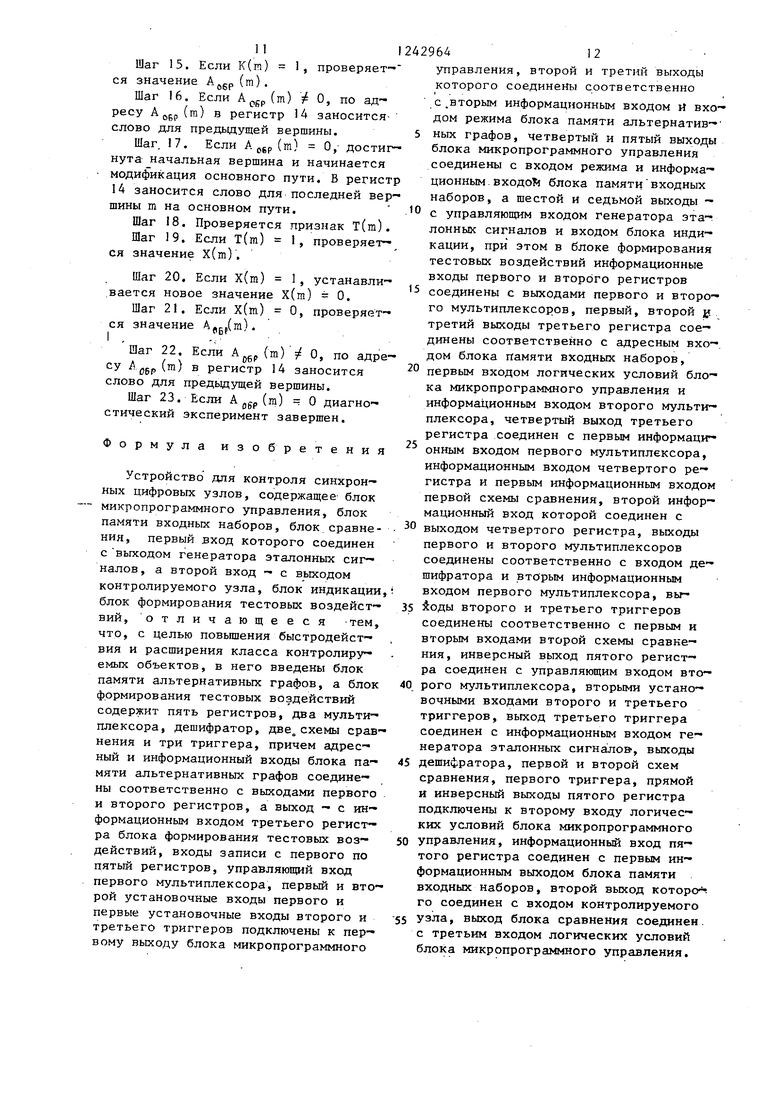

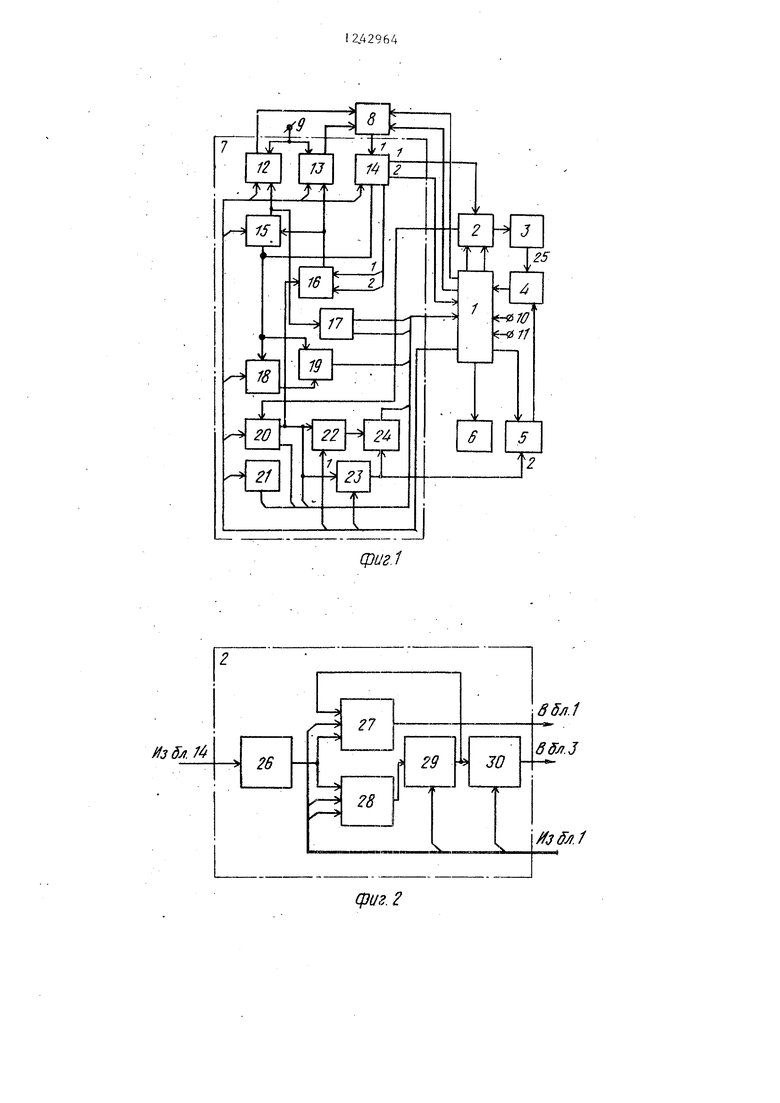

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 раскрыта, внутренняя структура блока памяти входных наборов; на фиг, 3 - то же, блока памяти альтернативных графов; на фиг, 4 раскрыт один возможный вариант реализации блока мик- ропрограммного управления; на фиг, 5 приведена блок-схема алгоритма работы блока управления.

Устройство (фиг, 1) содержит блок

1микропрограммного управления, блок

2памяти входных наборов,.контролиру емый узел 3, блок 4 сравнения, генератор 5 эталонных сигналов, блок 6 индикации, блок 7 формирования тестовых воздействий, блок 8 памяти альтернативных графов, вход 9 начальной установки блока 7, вход 10 запуска устройства и вход 11 начальной уста-. новки блока управления,.

Блок 7 содержит первый, второй и третий регистры 12, 13 и 14, мул ьти- плексоры 15 и 16, дешифратор I7, чет вертьгй регистр IS, первую схему 19 сравнения, пятый регистр 20, триггеры 21-23, вторую схему 24 сравнения, )зыход 25 контролируемого узла,

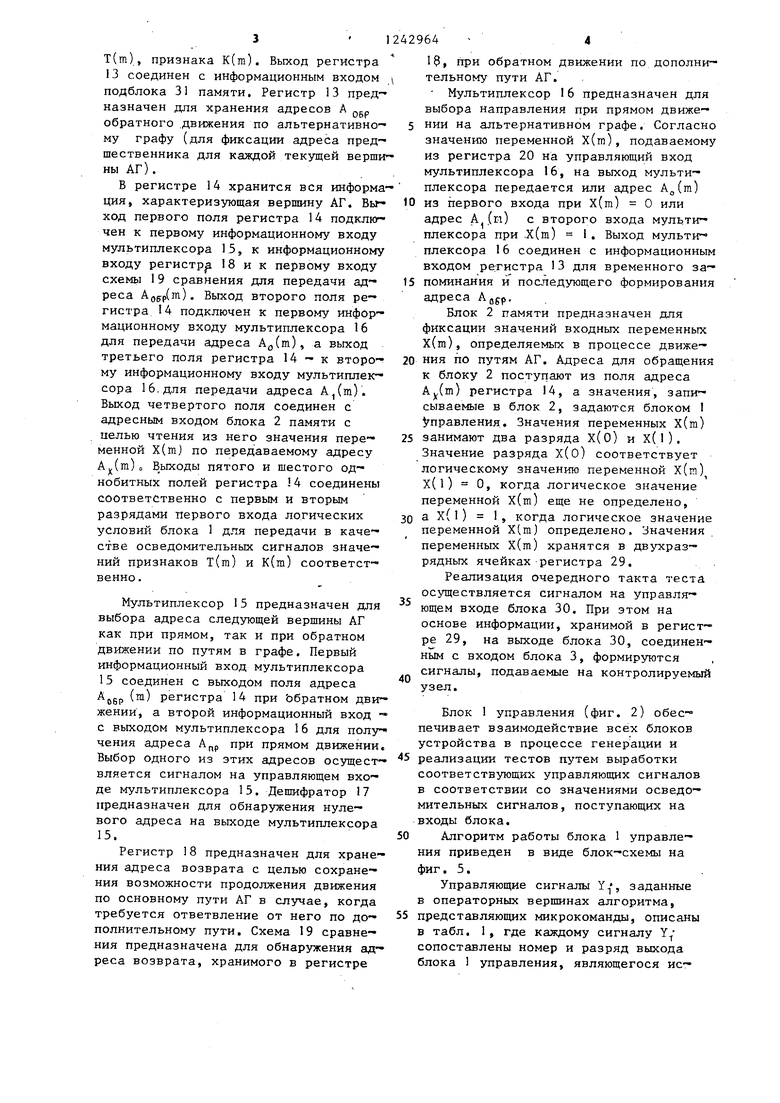

Блок 2 памяти входных наборов (фиг, 2) содержит дешифратор 26, выходной коммутатор 27, входной коммутатор 28, регистр 29 и блок З0.фор мирования входных сигналов.

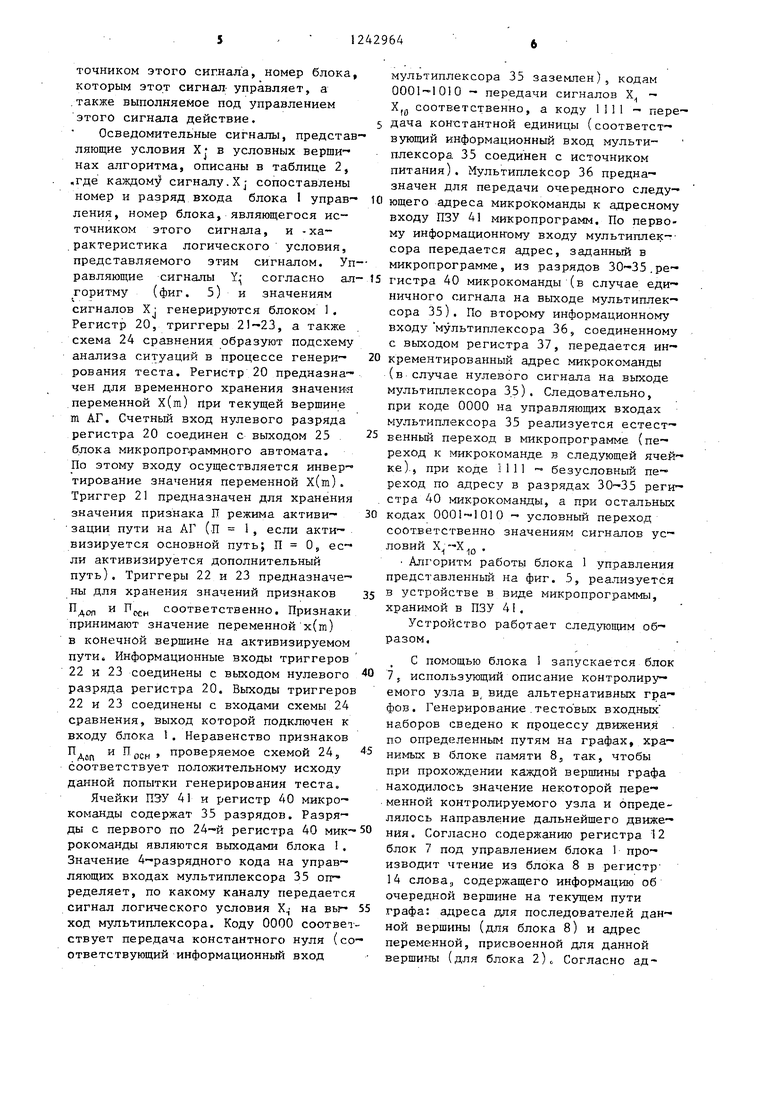

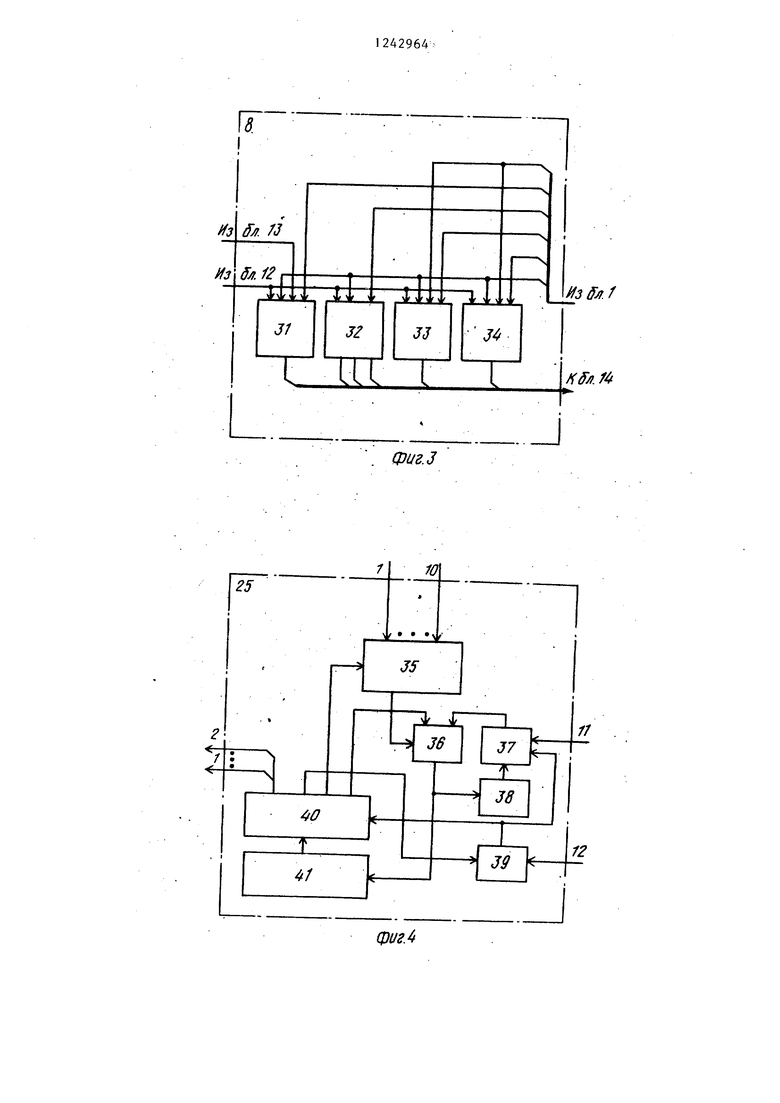

Блок 8 памяти альтернативных тра- фов (фиг, З) состоит из подблоков 31-34 -памяти,

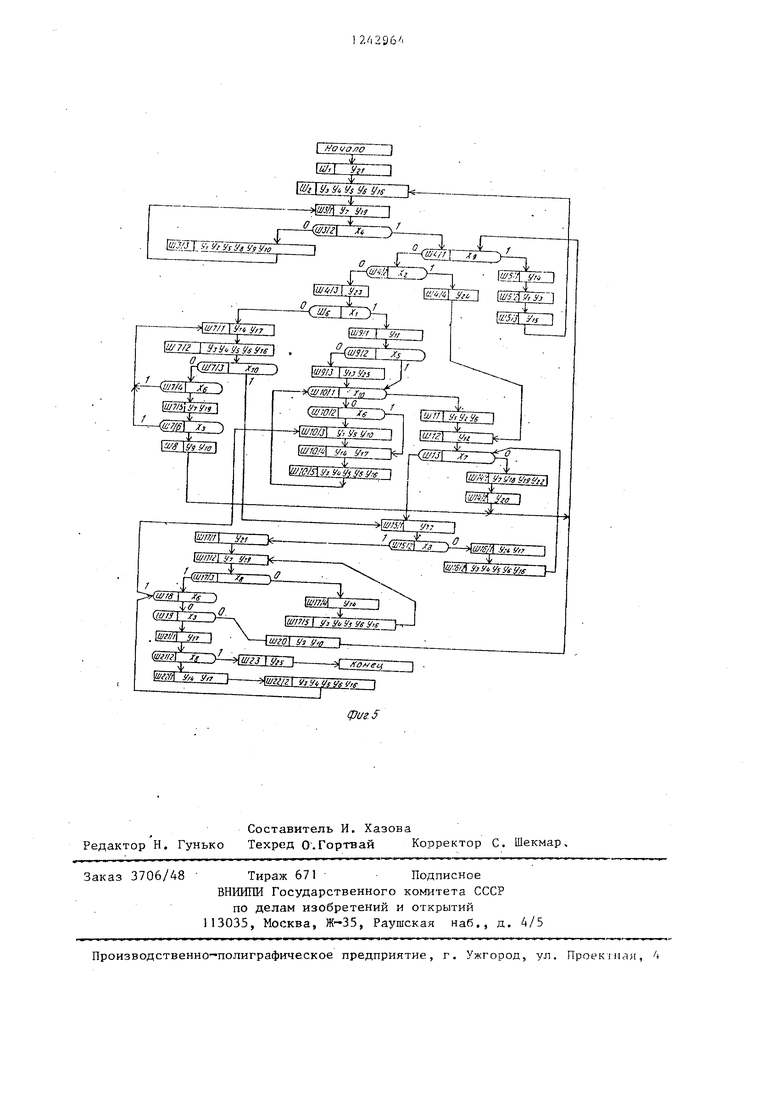

.Один возможный вариант реализации блока 1 (фиг , 4) содержит мультиплексоры 35 и 36, регистр 37, инкременто 38, тактовый генератор 39, регистр 40 и блок ПЗУ 41 микропрограмм, .

Блок 8 предназначен для хранения (шисания контролируемого узла в виде модели альтернативных графов, В каждой ячейке памяти хранится слово, (шисьюающее одну вершину m альтерна- тивного графа (АГ), Слово состоит,из .следующих полей: адрес (m) обратного движения по графу, адрес предыдущей вершины, из которой пришли в вершину т, адрес Ag(m) нижнего последователя вершины т, адрес А(п)

правого по-следователя вершины т, адрес А(т) значения переменной х(т), которой отмечена вершина т, признак Т(т) зафиксирования значения переменной Х(т)-/Т(т) 1, если значение

переменной Х(т) зафиксировано при проходе через вершины га, иначе Т(т) ,0 и признак К(т) проверенности вершины т/к (т) 1, если вершина m графа имеет уже тест, иначе К(т)

о) с Адреса (п) хранятся в подблоке 3 памяти, адреса A(m), А(m) и А(т) - 3 подблоке 32 памяти, приэна- ки Т(т)-хранятся в подблоке 33, а признаки К(т) - в подблоке 34 памяти,

Адреса А,, (т), А(т) и А(га) представляют собой описание контролируемого узла и находятся постоянно в подблоке 32 памяти, Дреса А (п), признак Т(т) и признак К(т) вычисляют в процессе генерирования тестов и поэтому содерхшмое подблоков 31-34 постоянно- изменяется.

Блок 7 предназначен для организации движения по путям альтернативных графов и формир ования в результате этого значений входных переменных контролируемого узла, представляющих собой тест. Исходной информацией для блока 7 является описание контроли-

руемого узла, хранимое в виде альтернативных графов в блоке 8 памяти АГ, Выходной информацией блока 7 являются значения переменных, записьшаемые в блок .2 памяти.

Обращение к блоку 8 памяти альтернативных графов осуществляется по адресам, хранимым в регистре 12, Начальная установка на нулевой адрес регистра 12, а также регистра 13,

предназначенного для зафиксирования а,цресов А р обратного движения, происходит по входу 9 начальной установки. Выход регистра 12 соединяется с адресными входами подблоков

31-34 памяти. По адресу, хранимому в регистре 12, происходит чтение из блока 8 слова, характеризугацего оп- ределенную верщину АГ, Выходы блока 8 подключены к информационным вхо-

ам соответствующих полей регистра 14, который имеет поля для хранения адреса A,gp(ra)j адреса Ар(т), адреса А(т), адреса А(т), признака

T(m), признака К(га). Выход регистра 13 соединен с информационным входом подблока 31 памяти. Регистр 13 предназначен для хранения адресов А обратного .движения по альтернативному графу (для фиксации адреса предшественника для каждой текущей вершины АГ ).. В регистре 14 хранится вся информация, характеризующая вершину АГ, Выход первого поля регистра 14 подключен к первому информационному входу мультиплексора 15, к информационному входу регистру I8 и к первому входу схемь 19 сравнения для передачи адреса A(j5p(m). Выход второго поля регистра 14 подключен к первому информационному входу мультиплексора 16 для передачи адреса ), а выход третьего поля регистра 14 - к второму информационному входу мультиплексора 16.для передачи адреса А(т). Выход четвертого поля соединен с адресным входом блока 2 памяти с целью чтения из него значения переменной Х(т) по передаваемому адресу А,(т) о В ькоды пятого и шестого однобитных полей регистра i 4 соединены соответственно с первым и вторым разрядами первого входа логических условий блока 1 для передачи в качестве осведомительных сигналов значений признаков Т(т) и К(т) соответственно .

Мультиплексор 15 предназначен для выбора адреса следующей вершины АГ как при прямом, так и при обратном движении по путям в графе. Первый информационный вход мультиплексора 15 соединен с выходом поля адреса А

10

(т) регистра 14 при Ьбратном дви- , а второй информационный вход -

19, при обратном движении по допо тельному пути АГ.

Мультиплексор 16 предназначен выбора направления при прямом дви

5 НИИ на альтернативном графе. Согл значению переменной X(in), подавае из регистра 20 на управляющий вхо мультиплексора 16, на выход мульт плексора передается или адрес А( из первого входа при Х(т) О или адрес А (п) с второго входа муль плексора при .Х(т) I , Выход муль плексора 16 соединен с информацио входом регистра 13 для временного

15 поминания и последующего формиров адреса ,

Блок 2 памяти предназначен для фиксации значений входных перемен Х(т), определяемых в процессе дви

20 ния по путям АГ. Адреса для обращ к блоку 2 поступают из поля адрес Ау(т) регистра 14, а значения, за сываемые в блок 2, задаются блоко Управления. Значения переменных х

25 занимают два разряда х(0) и Х(1). Значение разряда Х(0) соответству логическому значению переменной х Х( 1) О, когда логическое значен переменной Х(т) еще не определено

а Х(1) 1, когда логическое знач переменной Х(т) определено. Значе переменных Х(т) хранятся в двухра рядных ячейках-регистра 29.

Реализация очередного такта те осуществляется сигналом на управл ющем входе блока 30. При этом на основе информации, хранимой в рег ре 29, на выходе блока 30, соеди ным с входом блока 3, формируются сигналы, подаваемые на контролиру узел.

30

35

40

ЧбР жении

с выходом мультиплексора 16 для получения адреса при прямом движении. Выбор одного из этих адресов осущест- реализации тестов путем выработки

Блок 1 управления (фиг. 2) обе печивает взаимодействие всех блоко устройства в процессе генерации и

вляется сигналом на управляющем входе мультиплексора 15. Дешифратор 17 предназначен для обнаружения нулевого адреса на выходе мультиплексора 15.

Регистр 18 предназначен для хранения адреса возврата с целью сохранения возможности продолжения движения по основному пути АГ в случае, когда требуется ответвление от него по дополнительному пути. Схема 19 сравнения предназначена для обнаружения адреса возврата, хранимого в регистре

19, при обратном движении по дополнительному пути АГ.

Мультиплексор 16 предназначен для выбора направления при прямом движе-

НИИ на альтернативном графе. Согласно значению переменной X(in), подаваемому из регистра 20 на управляющий вход мультиплексора 16, на выход мультиплексора передается или адрес А(т из первого входа при Х(т) О или адрес А (п) с второго входа мультиплексора при .Х(т) I , Выход мультиплексора 16 соединен с информационным входом регистра 13 для временного за-

поминания и последующего формирования адреса ,

Блок 2 памяти предназначен для фиксации значений входных переменных Х(т), определяемых в процессе движе-

ния по путям АГ. Адреса для обращения к блоку 2 поступают из поля адреса Ау(т) регистра 14, а значения, записываемые в блок 2, задаются блоком 1 Управления. Значения переменных х(т)

занимают два разряда х(0) и Х(1). Значение разряда Х(0) соответствует логическому значению переменной х(т) Х( 1) О, когда логическое значение переменной Х(т) еще не определено,

а Х(1) 1, когда логическое значение переменной Х(т) определено. Значения переменных Х(т) хранятся в двухраз- рядных ячейках-регистра 29.

Реализация очередного такта теста осуществляется сигналом на управляющем входе блока 30. При этом на основе информации, хранимой в регистре 29, на выходе блока 30, соединенным с входом блока 3, формируются сигналы, подаваемые на контролируемый узел.

реализации тестов путем выработки

Блок 1 управления (фиг. 2) обеспечивает взаимодействие всех блоков устройства в процессе генерации и

соответствующих управляющих сигналов соответствии со значениями осведомительных сигналов, поступающих на входы блока.

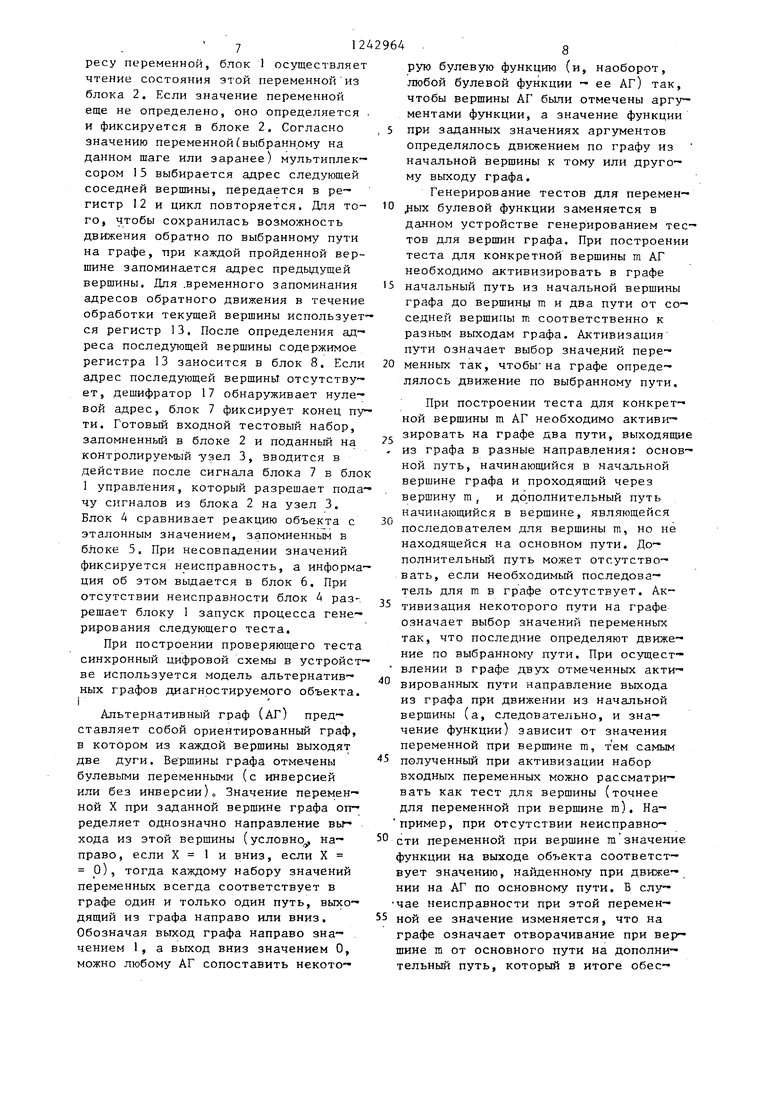

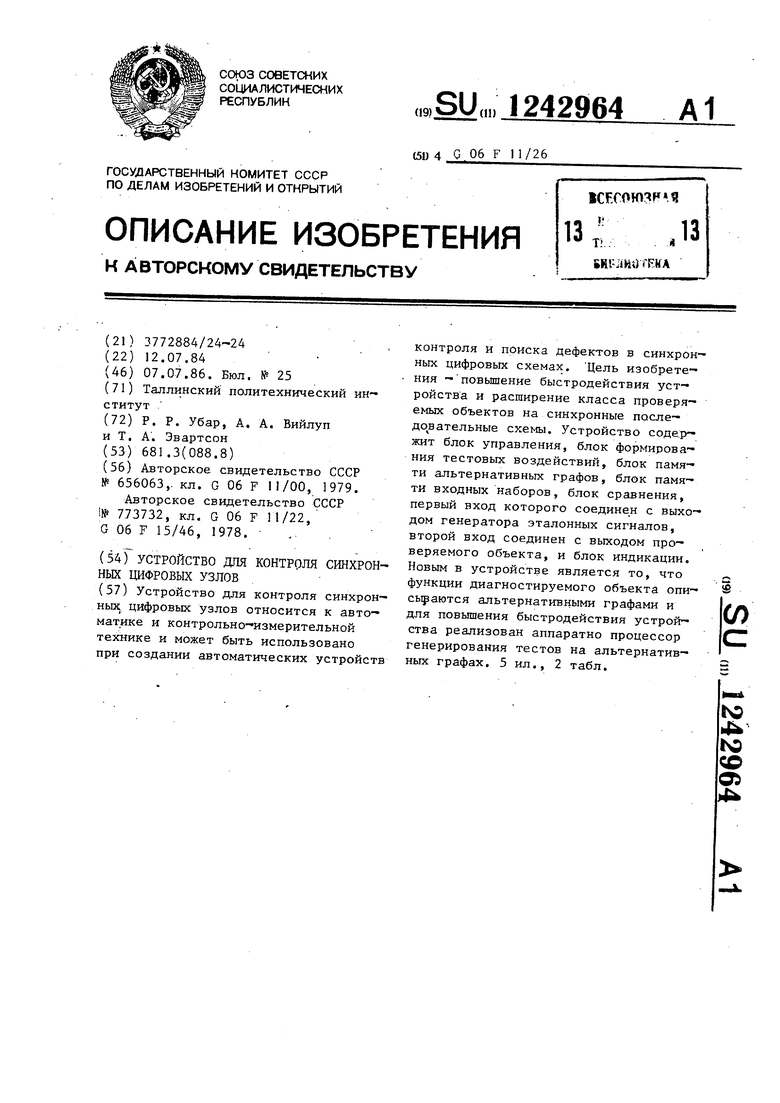

Алгоритм работы блока 1 управления приведен в виде блок-схемы на фиг. 5.

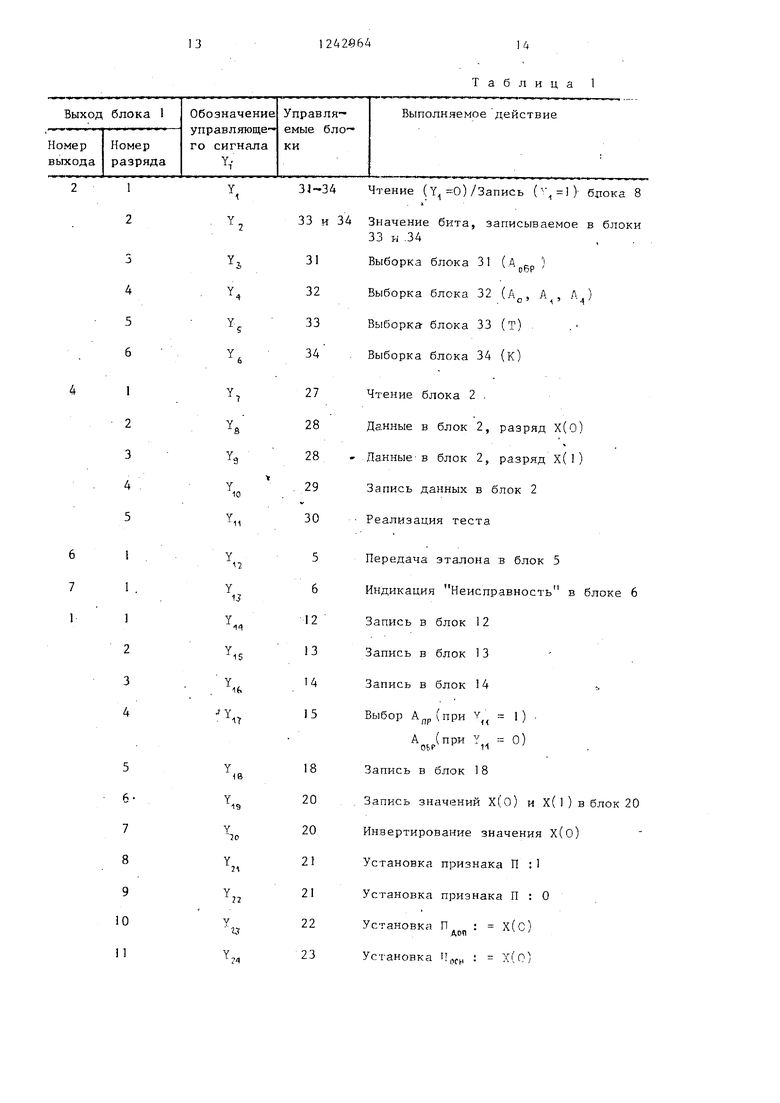

Управляющие сигналы , заданные в операторных вершинах алгоритма,

представляющих микрокоманды, описаны в табл. 1, где каждому сигналу Y., сопоставлены номер и разряд выхода блока 1 управления, являющегося ис-

точником этого сигнала, номер блока, которым этот сигнал- управляет, а .также выполняемое под управлением этого сигнала действие.

Осведомительные сигналы, представ ляющие условия Х- в условных вершинах алгоритма, описаны в таблице 2, ,где каждому сигналу.Xj сопоставлены номер и разряд входа блока 1 управ- ления, номер блока, являющегося источником этого сигнала, и -характеристика логического условия, представляемого этим сигналом. Уп равляющие сигналы Y согласно ал горитму (фиг. 5) и значениям сигналов X; генерируются блоком 1. Регистр 20, триггеры 21-23, а также схема 24 сравнения образуют подсхему анализа ситуаций в процессе генери- рования теста. Регистр 20 предназна- чен для временного хранения значени-я переменной Х(т) при текущей вершине m АГ. Счетный вход нулевого разряда регистра 20 соединен с выходом 25 блока микропрог заммного автомата. По этому входу осуществляется инвертирование значения переменной Х(т). Триггер 21 предназначен для хранения значения признака П режима активи- зации пути на АГ (-11 1 , если активизируется основной путь; П О, если активизируется дополнительный путь). Триггеры 22 и 23 предназначены для хранения значений признаков Пдоп осн соответственно. Признаки принимают значение переменной х(т) в конечной вершине на активизируемом пути. Информационные входы триггеров 22 и 23 соединены с выходом нулевого разряда регистра 20. Выходы триггеро 22 и 23 соединены с входами схемы 24 сравнения, выход которой подключен к входу блока 1. Неравенство признаков Пд и Пд(, , проверяемое схемой 24, соответствует положительному исходу данной попытки генерирования теста.

Ячейки ПЗУ 41 и регистр 40 микрокоманды содержат 35 разрядов. Разряды с первого по 24-й регистра 40 мик рокоманды являются выходами блока . Значение 4-разрядного кода на управляющих входах мультиплексора 35 определяет, по какому каналу передаетс сигнал логического условия на вы- ход мультиплексора. Коду 0000 соотвествует передача константного нуля (сответствующий информационный вход

мультиплексора 35 заземлен), кодам 0001-1010 - передачи сигналов Х - Х,д соответственно, а коду 1111 - передача константной единицы (соответствующий информационный вход мультиплексора 35 соединен с источником питания). Мультиплексор 36 предназначен для передачи очередного следующего адреса микрокоманды к адресному входу ПЗУ 4 микропрограмм. По первому информационному входу мультиплек-- сора передается адрес, заданный в микропрограмме, из разрядов 30-35.регистра 40 микрокоманды (в случае единичного сигнала на выходе мультиплексора 35). По второму информационному входу мультиплексора 36, соединенному с выходом регистра 37, передается ин- крементированный адрес микрокоманды (в случае нулевого сигнала на выходе мультиплексора 35). Следовательно, при коде 0000 на управляющих входах мультиплексора 35 реализуется естест- венньш переход в микропрограмме (переход к микрокоманде в следующей ячейке),, при коде 1111 - безусловный переход по адресз; в разрядах 30-35 регистра 40 1 ШКрокоманды, а при остальных кодах 0001-1010 - условный переход соответственно значениям сигналов условий .. .

Алх оритм работы блока 1 управления представленньш на фиг. 5, реализуется в устройстве в виде микропрограммы, хранимой в ПЗУ 41.

Устройство работает следующим образом.

С помощью блока 1 запускается блок 7, использующий описание контролируемого узла в, виде альтернативных графов. Генерирование.тестовых входных наборов сведено к процессу движения по определенным путям на графах, хранимых в блоке памяти 8, так, чтобы при прохождении каждой верщины графа находилось значение некоторой пере- .менной контролируемого узла и определялось направление дальнейшего движения. Согласно содержанию регистра 12 блок 7 под управлением блока 1 производит чтение из блока 8 в регистр 14 слова., содержащего информацию об очередной вершине на текущем пути графа: адреса для последователей данной вершины (для блока 8) и адрес переменной, присвоенной для данной вершиз-ш (для блока 2) о Согласно ад7

ресу переменной, блок 1 осуществляет чтение состояния этой переменной из блока 2. Если значение переменной еще не определено, оно определяется . и фиксируется в блоке 2. Согласно значению переменной(выбранному на данном шаге или заранее) мультиплексором 15 выбирается адрес следующей соседней вершины, передается в регистр 12 и цикл повторяется. Для того, чтобы сохранилась возможность движения обратно по выбранному пути на графе, при каждой пройденной вершине запоминается адрес предьщущей вершины. Для .временного запоминания адресов обратного движения в течение обработки текущей вершины используется регистр 13, После определения адреса последующей вершины содержимое регистра 13 заносится в блок 8, Если адрес последующей вершинь отсутству-

124

ет, дешифратор 17 обнаруживает нулевой адрес, блок 7 фиксирует конец пути. Готовый входной тестовый набор, запомненный в блоке 2 и поданный на контролируемый -узел 3, вводится в действие после сигнала блока 7 в бло 1 управления, который разрешает подачу сигналов из блока 2 на узел 3, Блок 4 сравнивает реакцию объекта с эталонным значением, запомненным в блоке 5. При несовпадении значений фиксируется неисправность, а информация об этом выдается в блок 6, При отсутствии неисправности блок 4 разрешает блоку 1 запуск процесса генерирования следующего теста.

При построении проверяющего теста синхронный цифровой схемы в устройстве используется модель альтернативных графов диагностируемого объекта.

Альтернативный граф (АГ) представляет собой ориентированный граф, в котором из каждой вершины выходят две дуги, Ве ршины графа отмечены булевыми переменными (с инверсией или без инверсии)о Значение переменной X при заданной вершине графа определяет однозначно направление выхода из этой вершины (условно, направо, если X 1 и вниз, если X о), тогда каждому набору значений переменных всегда соответствует в графе один и только один путь, выходящий из графа направо или вниз. Обозначая выход графа направо значением 1, а выход вниз значением О, можно любому АГ сопоставить некото-

2964 .g

рую булевую функцию (и, наоборот, любой булевой функции - ее АГ) так, чтобы вершины АГ бьши отмечены аргументами функции, а значение функции

5 при заданных значениях аргументов определялось движением по графу из начальной вершины к тому или другому выходу графа.

Генерирование тестов для перемен-

О jibDc булевой функции заменяется в

данном устройстве генерированием тестов для вершин графа. При построении теста для конкретной вершины m АГ необходимо активизировать в графе

15 начальный путь из начальной вершины графа до вершину m и два пути от соседней вершины m соответственно к разным выходам графа. Активизация пути означает выбор значений пере20 менных так, чтобы-на графе определялось движение по выбранному пути.

При построении теста для конкретной вершины m АГ необходимо активизировать на графе два пути, выходящие из графа в разные направления: основной путь, начинающийся в начал.ьной вершине графа и проходящий через вершину га , и дополнительный путь начинающийся в вершине, являющейся последователем для вершины т, но не находящейся на основном пути. Дополнительный путь может отсутствовать, если необходимый последователь для m в графе отсутствует, Ак тивизация некоторого пути на графе означает выбор значений переменных так, что последние определяют движение по выбранноь5 пути. При осущест- влении в графе двух отмеченных активированных пути направление выхода из графа при движении из начальной вершины (а, следовательно, и значение функции) зависит от значения переменной при вершине т, т ем самым полученный при активизации набор входных переменных можно рассматривать как тест для вершины (точнее для переменной при вершине т). Например, при отсутствии неисправности переменной при вершине m значение функции на выходе объекта соответствует значению, нaйдeннo ry при движении на АГ по основному пути, В слу- чае неисправности при этой перемен- ной ее значение изменяется, что на графе означает отворачивание при вершине m от основного пути на дополнительный путь, который в итоге обес

печивает Изменение сигнала на выходе объекта,.

Процесс построения тестов сводится к поочередному сканированию различных путей на графе, т.е. к поочеред ной активации .различных путей из начальной вершины графя к тому или другому выходу графа. Достигнутый выход определяет эталонное значение при генерируемом тесте. Выход направо соответствует эталонному значению 1, выход вниз - значению 0.

Для ранее непроверенных вершин на текущем пути делается попытка активизации дополнительного пути из их соседних вершин, не находящихся на пути, к другому выходу графа, так, чтобы дополнительный путь .не пересекал основной путь. При существовании такого пути и при положительном результате теста фиксируется проверен- кость соответствующей вершины. Все вершины проверяются на два направления (соответственно на неисправности соответствующей переменной констант О и константа Г ).

Генерирование тестов осуществляется в устройстве под управлением блока 1 по алгоритму, изображенному на фиг,5,

Шаг 1. Устанавливается исходное состояние устройства. В блок 8 введено описание объекта диагностирования в виде альтернативного графа, В каждой ячейке памяти находится слово, характеризующее одну вершину m АГ. Слово состоит из следующих полей: адрес А|(т) переменной Х(т), которой отмечена данная вершина т, адреса А (т) и А(т) соответственно нижнего и правого последователей вершины т, адрес обратного движения Aggp(m), признак Т(т) того, что значение переменной Х(т) определяется при вер- щине m и признак К(т) проверенности вершины т. Область в блоке 8 для Apgp (m), T(m) и К(т) представляет собой рабочее поле и заполняется в п}эоцессе генерирования тестов. До начала работы алгоритма содержимое этих полей нулевое. Очищается блок 2., где будут храниться значения пе-. ременных X. Устанавливается признак , означающий, что активизируемым является основной путь.

Шаг 2. Чтение из блока 8 по адресу в регистре 12 слова, характеризующего текущую вершину т.

10

IS

25

4296410

. Шаг 3. Ели г иачение Х(т) неопреде- лено, зафиксируется значение Х{п) и заносится по адресу А,,(т) в блок 2. Устанавливается Т(т) I.

Шаг 4. Определяется адрес. (т) прямого движения, т.е. адрес следующей вершины на активизируемом пути:

О и

т), если Х(т) .1. Если О, зафиксируется направление выхода из графа: признак П оси (если П i ) или признак Пдоп (если П о) принимает значение Х(т)„

Шаг 5. Если Апр(гг.) О, то А„р(т) передается в регистр 12, Apgp (т) (содержимое регистра 13) передается

AfjpM Ад(т), если Х(т)

А„Лт) А/

(т,

затем АПР (т) в качестве

ПР

30

в блок 8,, а

следующего А передается на времен ное хранение в регистр 13. ° Шаг 7„ Если Т1 П , попытка генерирования теста по данному дополнительному пути не удалась. Путем обратного движения (по. адресам Ajigp ) на дополнительном пути ищется первая вершина т, где Т(т) 1 и Х(т) 1. Если такой вершины не находится, то перейти к шагу 15, I

Шаг 8, Если такая вершина нахо- дится, устанавливается новое значение переменной х(т) (пробуется второй вариант).

Шаг 9. Если П П,, тест по строен. Происходит реализация теста на диагностируемом объекте. Если тест проходит, то - к Ш 10.

Шаг 10. Переход к построению следующего теста. Переменные х(т) при всех вершинах на дополнительном пути, где Т(т) 1, освобождаются от зафиксированных значений. Признаки Т(т) при этИ Х вершинах принимают нулевое значение.

Шаг 1I. Зафиксируется признак K(in) : 1 проверенности проверяемой вершины т.

35

40

45

Шаг 12. Если А

пр

(т)

Ои П Г

значение Пр, служит эталоном для генерируемых на базе данного основного пути тестов и передается в генератор 5.

Шаг 13, Проверяется признак К(т)„ Шаг 14. Если К (т) О, начинается попытка генерирования теста для вершины га путем активизации дополнитель- ного пути, изменяется адрес Апр(т) прямого движения: А-р(т) Ag(m), если X(m) I и Applm) А,(m), если Х(т) 0. Ус ганавливается 17 0.

11 I

Шаг 15, Если К(т) 1, проверяет- ся значение (m).

Шаг 16, Если (m) О, по адресу А (.,gp (m) в регистр 14 заносится- слово для предыдущей вершины.

Шаг. 17, Если (т) О,- достигнута начальная вершина и начинается модификация основного пути, В регистр 14 заносится слово для последней вершины m на основном пути.

Шаг 18, Проверяется признак Т(т),

Шаг 19, Если т(т) 1, проверяется значение Х(т),

Шаг 20, Если х(т) 1, устанавливается новое значение Х(т) О,

Шаг 21, Если Х(т) О, проверяет(1БГ

ся значение А.с.(го),

Шаг 22, Если Apgp(m)V О, по адресу (т) в регистр 14 заносится слово для предьщущей вершины.

Шаг 23, Если А gp (га) О диагностический эксперимент завершен.

Формула изобретения

Устройство для контроля синхронных цифровых узлов, содержащее- блок микропрограммного управления, блок памяти входных наборов, блок.сравне- ния, первый вход которого соединен с выходом генератора эталонных сигналов, а второй вход - с вькодом контролируемого узла, блок индикации блок формирования тестовых воздействий, отличающееся тем, что, с целью повышения быстродействия и расширения класса контролируемых объектов, в него введены блок памяти альтернативных графов, а блок формирования тестовых воздействий содержит пять регистров, два мультиплексора, дешифратор, две„ схемы сравнения и три триггера, причем адресный и информационный входы блока памяти альтернативных графов соединены соответственно с выходами первого и второго регистров, а выход - с информационным входом третьего регистра блока формирования тестовых воздействий, входы записи с первого по пятый регистров, управляющий вход первого мультиплексора, первый и второй установочные входы первого и первые установочные входы второго и третьего триггеров подключены к первому выходу блока микропрограммного

4296412

управления, второй и третий выходы которого соединены соответственно с.вторым информационным входом и входом режима блока памяти альтернатив- 5 ных графов, четвертый и пятый выходы блока микропрограммного управления соединены с входом режима и информационным .входов блока памяти входных наборов, а шестой и седьмой вькоды -

10

с управляющим входом генератора зталонных сигналов и входом блока индикации, при этом в блоке формирования тестовьк воздействий информационные входы первого и второго регистров

соединены с выходами первого и второго мультиплексоров, первый, второй f. третий выходы третьего регистра соединены соответственно с адресным вхо-. дом блока памяти входных наборов,

первым входом логических условий блока микропрограммного управления и информационным входом второго мультиплексора, четвертый выход третьего регистра соединен с первым информационным входом первого мультиплексора, информационным входом четвертого регистра и первым информационным входом первой схемы сравнения, второй информационный вход которой соединен с

выходом четвертого регистра, выходы первого и второго мультиплексоров соединены соответственно с входом дешифратора и вторым информационным входом первого мультиплексора, вьгйоды второго и третьего триггеров соединены соответственно с первым и вторым входами второй схемы сравнения, инверсный вьгход пятого регистра соединен с управляющим входом вто-

рого мультиплексора, вторыми установочными входами второго и третьего триггеров, вьгход третьего триггера соединен с информационным входом генератора эталонных сигналов-, выходы

дешифратора, первой и второй схем сравнения, первого триггера, прямой и инверсный выходы пятого регистра подключены к второму входу логических условий блока микропрограммного

управления, информационный вход пятого регистра соединен с первым информационным выходом блока памяти входных наборов, второй выход которое го соединен с входом контролируемого

узла, выход блока сравнения соединен, с третьим входом логических условий блока микропрограммного управления.

Таблица 1

15

4 7 6

5

X.

X,

1 2

1

2 3

IB

1242964

16

Продолжение табл.I

Таблица 2

Х 1 при У П

Хд П

Х5 1 при Х(0) О

Х Х(1)

Результат теста (Х 1 при положительном исходе теста)

14 Х. 1 при ) О

. ,

14 Х К(т)

17

Xfl 1 при (т) О

а

Хд 1 при А-Лш) 7 О

9 « пр Признак искомого адреса

Сигнал начальной установки устройства

10

Запуск устройства

Из5л7

85Л.1

в5л.З

.f

(риз. 2

Из

/J

Из

5л.12

к Ул. Г

.. J

Фиг.З

Составитель И. Хазова Редактор н. Гунько Техред О .Гортвай Корректор С. Шекмар,

3706/48

Тираж 671- Подписное ВНИРШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектам, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для тестового контроля больших интегральных схем | 1984 |

|

SU1218390A1 |

| Устройство для диагностики неисправностей технических объектов | 1988 |

|

SU1536357A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1168939A1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| САМОКОНТРОЛИРУЕМЫЙ АВТОМАТ | 2011 |

|

RU2502121C2 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Устройство для обработки нечеткой информации | 1990 |

|

SU1758642A1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

Устройство для контроля синхронных цифровых узлов относится к автоматике и контрольно-измерительной технике и может быть использовано при создании автоматических устройств контроля и поиска дефектов в синхронных цифровых схемах. Цель изобретения - повьшение быстродействия устройства и расширение класса проверяемых объектов на синхронные после- до вательные схемы. Устройство соде.р- жит блок управления, блок формирования тестовых воздействий, блок памяти альтернативных графов, блок памяти входных наборов, блок сравнения, первый вход которого соединен с выходом генератора эталонных сигналов, второй вход соединен с выходом проверяемого объекта, и блок индикации. Новым в устройстве является то, что функции диагностируемого объекта опи- сь аются альтернативными графами и для повышения быстродействия устройства реализован аппаратно процессор генерирования тестов на альтернативных графах. 5 ил., 2 табл. 4 О) ьо 4 Ю СО О)

| Устройство для автоматического контроля цифровых объектов | 1977 |

|

SU656063A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU773732A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ,- . | |||

Авторы

Даты

1986-07-07—Публикация

1984-07-12—Подача