«

Изобретение относится к цифровой f-ехнике и может быть использовано для наладки, контроля и ремонта цифровых устройств.

Цель изобретения - цовышение достоверности диагностики неисправностей цифровых устройств путем выявления изолированных ошибок в любом нечетном количестве бит и выявления пйчек ошибок люб.ой длины, кроме вида 12п, гдеh- натуральное число, в последовательностях любой длины.

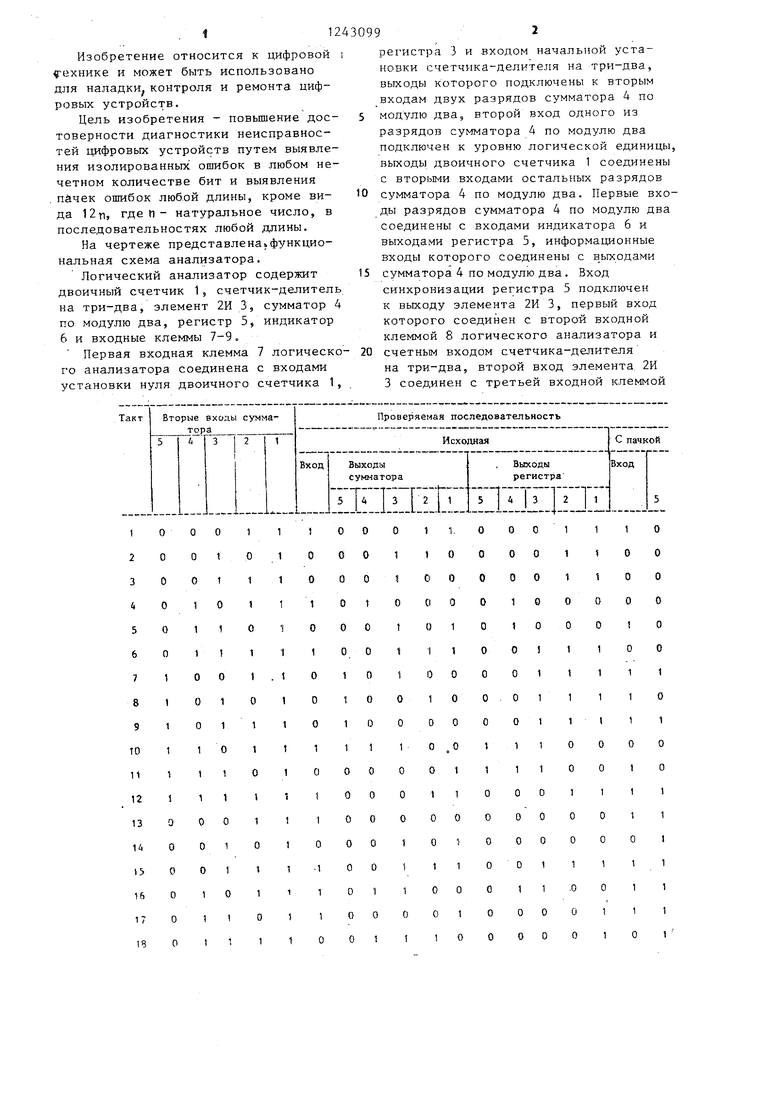

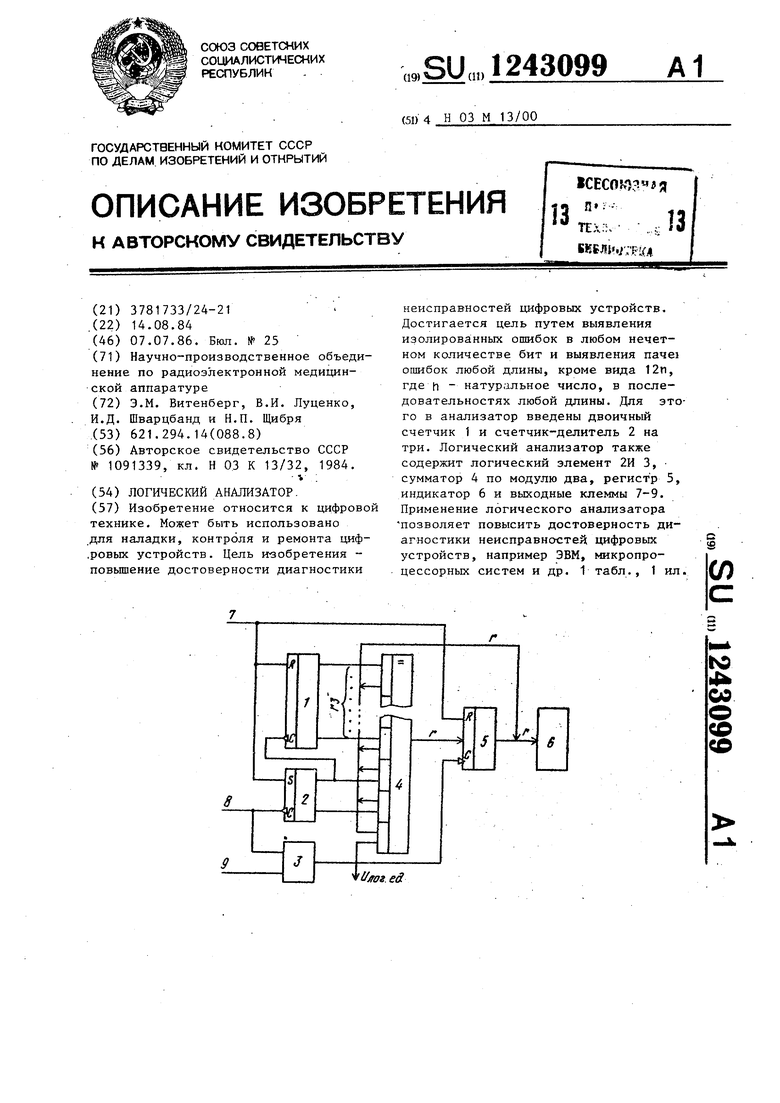

На чертеже представлена функциональная схема анализатора.

Логический анализатор содержит двоичный счетчик 1, счетчик-делитель на три-два, элемент 2И 3, сумматор 4 по модулю два, регистр 5, индикатор 6 и входные клеммы 7-9.

12430992

регист эа 3 и входом начальной установки счетчика-делителя на три-два, выходы которого подключены к вторым входам двух разрядов сумматора 4 по

5 модулю два, второй вход одного из разрядов сумматора 4 по модулю два подключен к уровню логической единицы, выходы двоичного счетчика 1 соединены с вторыми входами остальных разрядов

10 сумматора 4 по модулю два. Первые входы разрядов сумматора 4 по модулю два соединены с входами индикатора 6 и выходами регистра 5, информационные входы которого соединены с в ыходами

15 сумматора 4 по модулю два . Вход

синхронизации регистра 5 подключен к выходу элемента 2И 3, первый вход которого соединен с второй входной

клеммой 8 логического анализатора и Первая входная клемма 7 логическо- 20 счетным входом счетчика-делителя го анализатора соединена с входами на три-два, второй вход элемента, 2И установки нуля двоичного счетчика 1, . 3 соединен с третьей входной клеммой

О О

о

о

о

о

1

1

1

1

1

1

о

о

о

о

о

о

о о 1 1 1 о о о 1 1 1

о о о

1 1

1

t

о

1

t

о

1

1

о

1

1

о

1 1

о 1

1

о

1

1

о

1

1

о

1

1

о

1

1

о

t

1

о

1

1 1 1

1 1 | t 1 1 t 1

1 1 1 1 1

1 о о 1 о 1 о

D

о

1

о

1

1

о

1

1

1

о

о о о о

о о

о

1

о о

0о о о

D

11 оо оо оо оо оо о1 оо о1

о 1 о 1

о

1

1

о

t

1

1

о

о

1

о

о

о

1

1

1

о

1

1 1

о

С1

о

1

1. о о о 1 1

0о

1о

о о о .0

01

11 о о

01

11

о о о

о

о

о

о

о

о

1

1

о

о

о

о

о

о

о

о о о о о о о о 1 1 1 1 1 1 о

1 1 о

о о о 1 1

о

о о о о

01

11 о о о о

1 1

1 о

о 1 1

1 1

о о 1

о о 1 .0

о о

1 1

о о 1 1 1 1

о о

1

о о

1 о 1 1

1 о

о о 1

о 1 1 1

о 1 I 1 о 1 1 1 о

о о о о

о о 1 о 1 о о 1 1 1 1 1

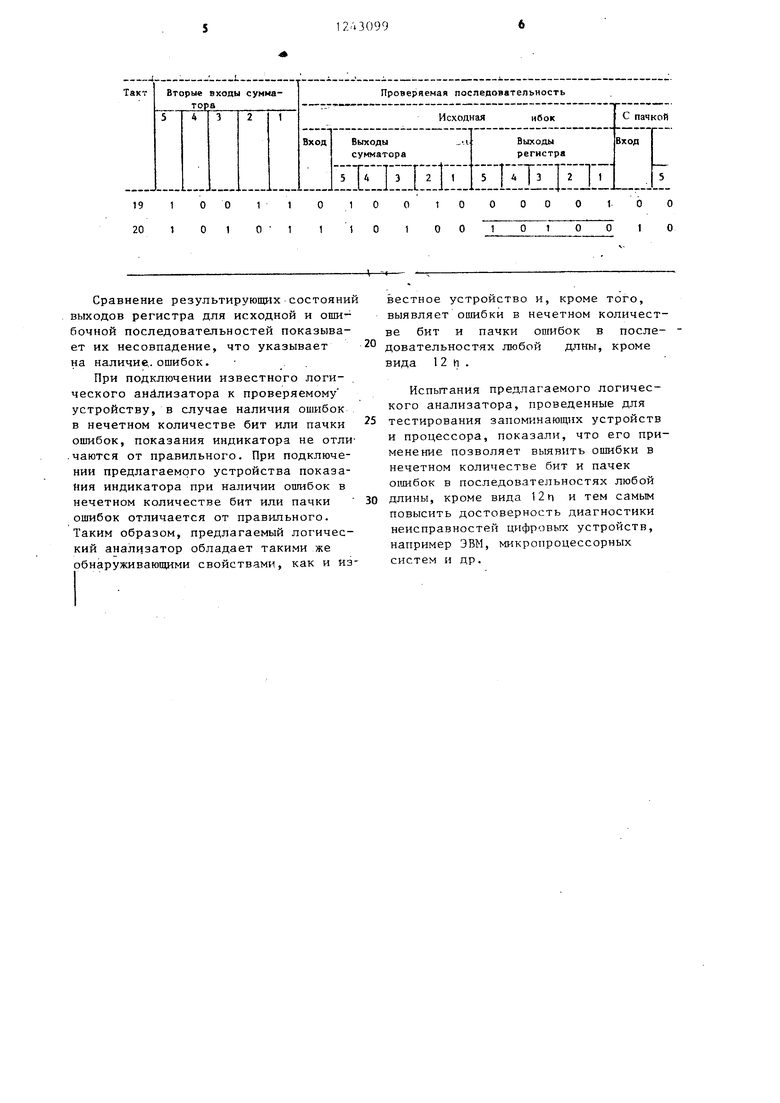

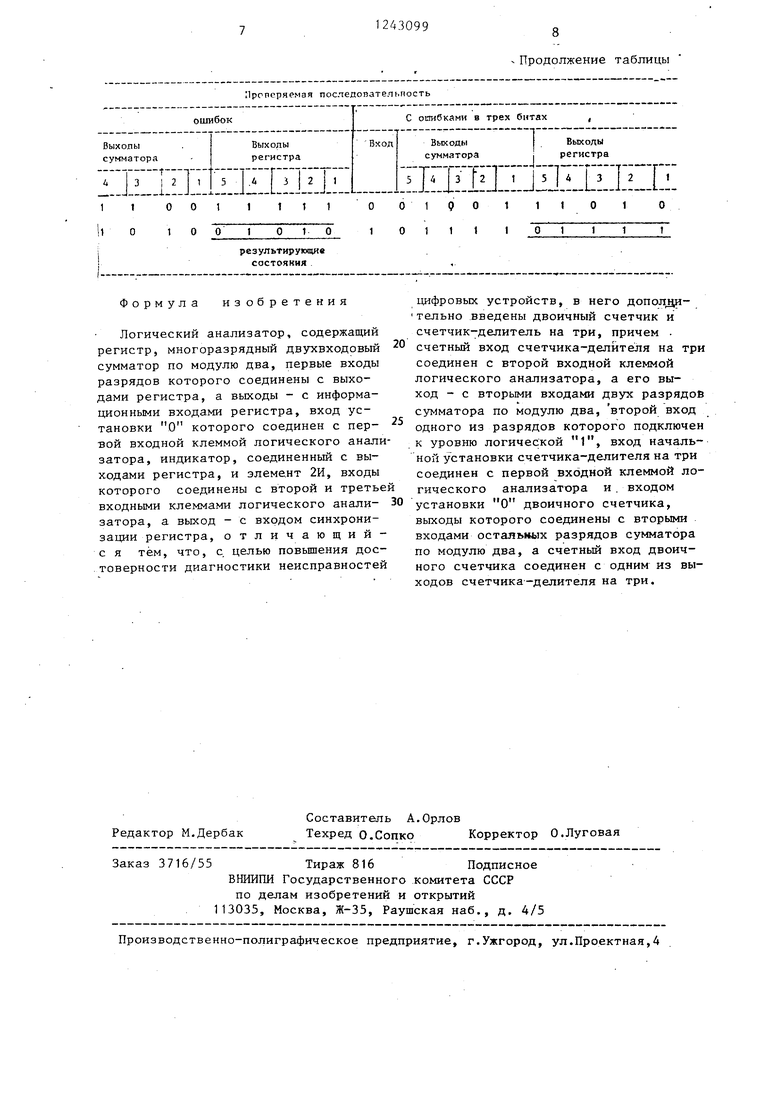

Сравнение результирующих состояний выходов регистра для исходной и ошибочной последовательностей показывает их несовпадение, что указывает на наличие., ошибок.

При подключении известного логического анализатора к проверяемому устройству, в случае наличия ошибок в нечетном количестве бит или пачки ошибок, показания индикатора не отличаются от правильного. При подключении предлагаемого устройства показания индикатора при наличии ошибок в нечетном количестве бит или пачки ошибок отличается от правильного. Таким образом, предлагаемый логический анализатор обладает такими же обнаруживающими свойствами, как и из0

5

0

вестное устройство и, кроме того, выявляет ошибки в нечетном количестве бит и пачки ошибок в последовательностях любой длны, кроме вида 1 2 п .

Испытания предлагаемого логического анализатора, проведенные для тестирования запоминающих устройств и процессора, показали, что его применение позволяет выявить ошибки в нечетном количестве бит и пачек отиибок в последовательностях любой длины, кроме вида 12ri и тем самым повысить достоверность диагностики неисправностей цифровых устройств, например ЭВМ, микропроцессорных систем и др.

9 логического анализатора. Счетный вход двоичного счетчика 1 соединен с одним из выходов счетчика-делителя на три-два.

Логический анализатор работает следующим образом.

Перед началом работы импульсом на входной клемме двоичный счетчик 1 и регистр 5 устанавливают в положение О, а счетчик-делитель на три-два - в положение 1. Проверяемую после- .довательность подают на входную г клемму 9. На входную клемму 8 подают синхроимпульсы, синхронизирующие каждый разряд последовательности. По переднему фронту происходит запись в регистр 5, а по заднему - переключение счетчика-делителя на три-два.

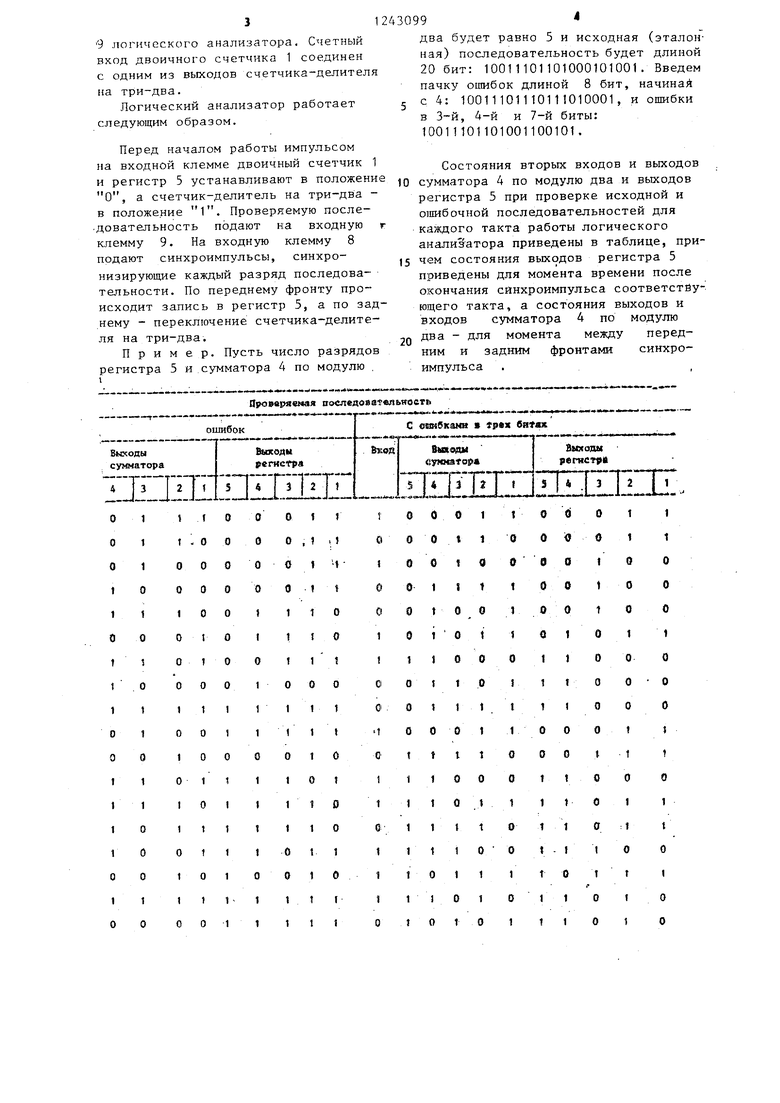

Пример. Пусть число разрядов регистра 5 и сумматора 4 по модулю ,

два будет равно 5 и исходная (эталон ная) последовательность будет длиной 20 бит: 10011101101000101001. Введем пачку ошибок длиной 8 бит, начинай с 4: 10011101110111010001, и ошибки в 3-й, 4-й и 7-й биты: 10011101101001100101.

Состояния вторых входов и выходов сумматора 4 по модулю два и выходов регистра 5 при проверке исходной и ошибочной последовательностей для каждого такта работы логического анализатора приведены в таблице, при- чем состояния выходов регистра 5 приведены для момента времени после окончания Синхроимпульса соответствующего такта, а состояния выходов и входов сумматора 4 по модулю два - для момента между передним и задним фронтами синхроимпульса .

Пропоряемэя последовательность

рез ультируюоу состояния

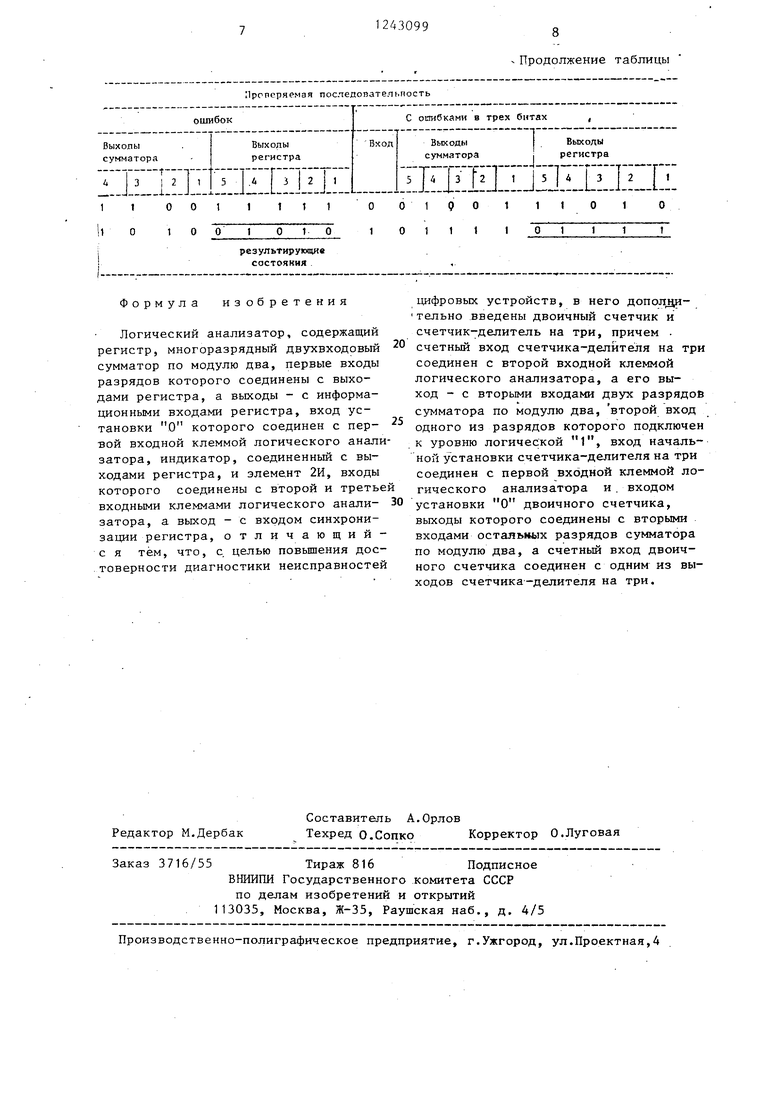

Формула изобретения

Логический анализатор, содержащий регистр, многоразрядный двухвходовый сумматор по модулю два, первые входы разрядов которого соединены с выходами регистра, а выходы - с информационными входами регистра, вход установки О которого соединен с первой входной клеммой логического анализатора, индикатор, соединенный с выходами регистра, и элемент 2И, входы которого соединены с второй и третьей

- 3

входными клеммами логического анали

затора, а выход

- с входом синхронизации регистра, отличающий- с я тем, что, с целью повышения достоверности диагностики неисправностей

Редактор М.Дербак

Составитель А.Орлов

Техред О.Сопке Корректор 0.Луговая

Заказ 3716/55Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Продолжение таблицы

й

20

25

30

цифровых устройств, в него дополди- тельно введены двоичный счетчик и счетчик-делитель на три, причем . счетный вход счетчика-делителя на три соединен с второй входной клеммой логического анализатора, а его выход - с вторыми входами двух разрядов сумматора по модулю два, второй вход одного из разрядов которого подключен к уровню логической 1, вход начальной у становки счетчика-делителя на три соединен с первой входной клеммой логического анализатора и . входом установки О двоичного счетчика, выходы которого соединены с вторыми входами остальных разрядов сумматора по модулю два, а счетный вход двоичного счетчика соединен с одним из выходов счетчика-делителя на три.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1986 |

|

SU1311011A2 |

| Логический анализатор | 1983 |

|

SU1160569A1 |

| Логический анализатор | 1982 |

|

SU1091339A1 |

| Кодек блочных кодов | 1984 |

|

SU1270899A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

| СПОСОБ ПЕРЕДАЧИ МНОГОМЕРНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ, СПОСОБ СЛОВНОЙ СИНХРОНИЗАЦИИ МАЖОРИТАРНО УПЛОТНЕННЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2004 |

|

RU2262206C1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1837291A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

Изобретение относится к цифровой технике. Может быть использовано для наладки, контроля и ремонта циф- .ровых устройств. Цель изобретения - повьшение достоверности диагностики неисправностей цифровых устройств. Достигается цель путем выявления изолирова:нньгх опшбок в любом нечетном количестве бит и выявления паче ошибок любой длины, кроме вида 12п, где h натуральное число, в последовательностях любой длины. Для этого в анализатор введены двоичный счетчик 1 и счетчик-делитель 2 на три. Логический анализатор также содержит логический элемент 2И 3, сумматор 4 по модулю два, регистр 5, индикатор 6 и выходные клеммы 7-9. Применение логического анализатора позволяет повысить достоверность диагностики неисправностей; цифровых устройств, например ЭВМ, микропроцессорных систем и др. 1 табл., 1 ил. с в ел N9 оо о ;0

| Логический анализатор | 1982 |

|

SU1091339A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| : | |||

Авторы

Даты

1986-07-07—Публикация

1984-08-14—Подача