с т

к

а

R&

я

ел

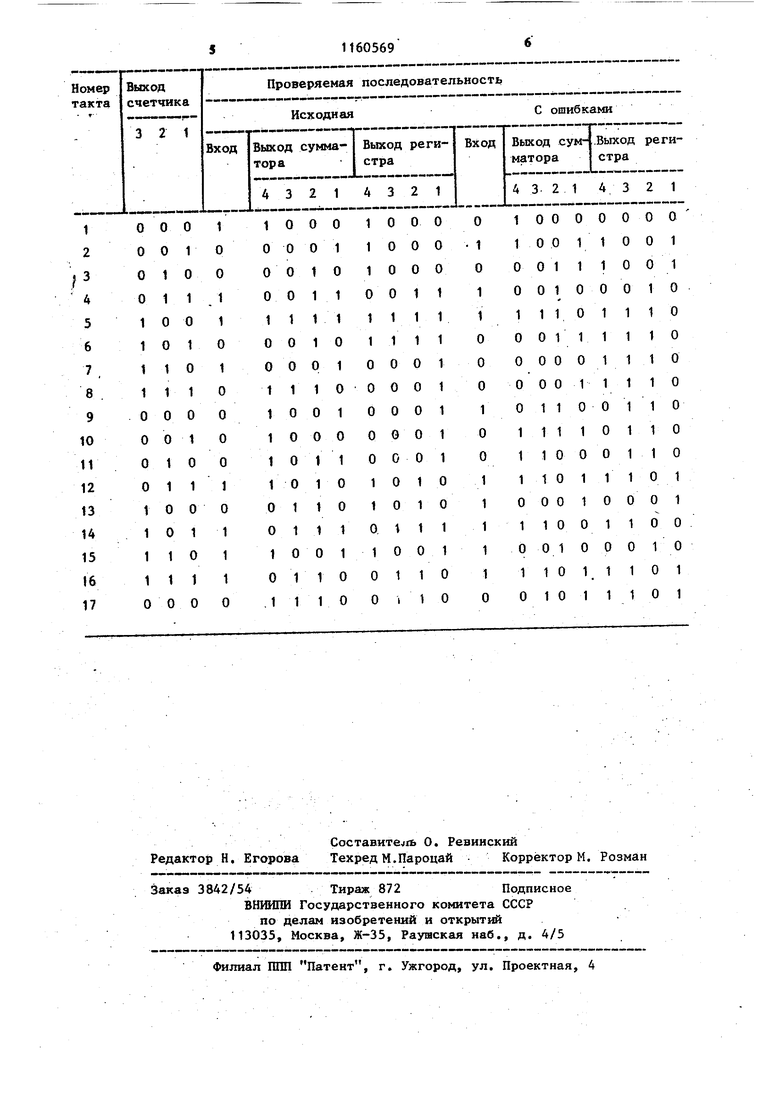

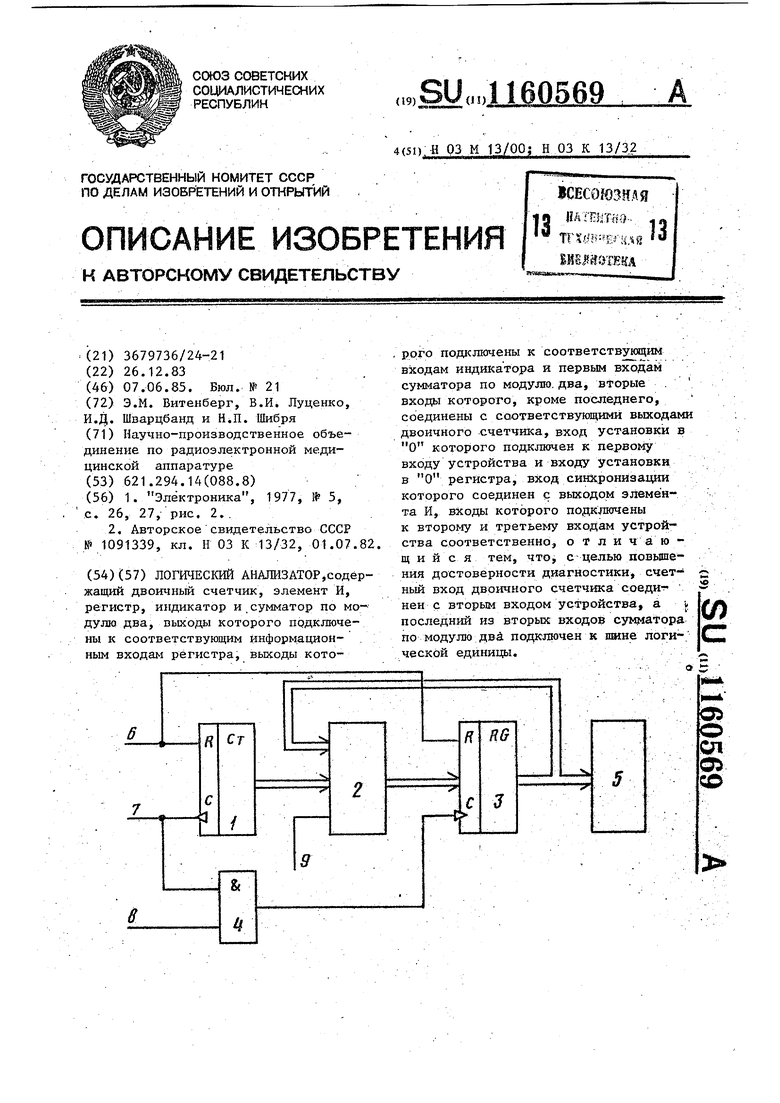

б: со Изобретение относится к импульс ной технике и может быть применено для наладки, ремонта и контроля цифровых устройств (например, ЭВМ, микропроцессорные системы, и прочее) Известен логический анализатор, содержащий регистр, индикатор и сум матор по модулю два, входы которого подключены к выходам соответствующи разрядов регистра сдвига, вход кото рого соединен с выходом сумматора п модулю два ,fl3 . Недостатком этого устройства является невозможность локализовать ошибку во входной последовательност Наиболее близким техническим решением к предлагаемому является логический анализатор, содержащий двоичный счетчик, элемент И, регист индикатор и сумматор по модулю два выходы которого подключены к соотве ствующим информационным входам реги стра, выходы которого подключены к соответствующим входам индикатора и первым входам сумматора по модулю два, вторые входы которого, кроме последнего, соединены с соответствующими выходами двоичного счетчика, вход установки в О которого подключен к первому входу устройст- на и ВХОДУ: установки в О регистра, вход синхронизации которого соединен с вькодом элемента И, вход которого подключены к второму и третьему входам устройства соответственно, при этом двоичный счетчик входит в состав счетчика с исключен ным нулевым состоянием, содержащим, кроме этого, три элемента И-НЕ и триггер 3 Однако известному логическому анализатору присуща недостаточная достоверность диагностики, заключающаяся в невозможности выявления ошибки более, чем в двух разрядах входной последовательности. Цель изобретения - повьшение дос товерности диагностики. Для достижения поставленной цели в логическом анализаторе, содержащем двоичньй счетчик, элемент И, регист индикатор и сумматор по модулю два, выходы которого подключены к соответствуияцим информационным входам регистра, выходы которого подключены к соответствукщим входам индикатора и первым входам сумматора п модуЛю два, вторые входы которого. кроме последнего, соединены с соответствую цими выходами двоичйого счетчика, вход установки в О которого подключен к первому входу устройства и входу установки в О регистра, вход синхронизации которого соединен с вькодом элемента И, входы которого подключены ко второму и третьему входам устройства соответственно, счетный вход двоичного счетчика соединен со вторым входом устройст-ва, а последний из вторых входов сумматора по модулю два подключен к шине логической единицы. На чертеже приведена функциональная схема логического, анализатора. Логический анализатор содержит двоичный счетчик 1, сумматор 2 по модулю два, регистр 3, элемент И 4, индикатор 5, первый, второй и третий входы 6-8, шину 9 логической t. Вход 6 логического анализатора соединен со входами установки в О двоичного счетчика 1 и регистра 3, вход 7 соединен со счетным входом двоичного счетчика 1 и первым входом элемента И 4, выход которого соединен со входом синхронизации регистра 3. Выходы регистра 3 соединены со входами индикатора 5 и первыми входами сумматора 2 по модулю два. Вбкоды двоичного счетчика 1 соединены со вторыми входами сумматора 2 по модулю два, кроме последнего, который соединен с шиной 9 логической 1. Вход 8 подключен ко второму входу элемента И 4. Логический анализатор работает следующим образом. Перед началом работы импульсом по входу 6 счетчик 1 и регистр 3 устанавливают в состояние О. Проверяемую последовательность подают на вход 8, на вход 7 подают синхроимпульсы,синхронизирующие каждый разряд последовательности. По переднему фронту синхроимпульсов происходит запись в регистр 3, по заднему - переключение счетчика 1. Состояние выходов регистра 3 опи- сьюается уравнением ft(d)dL- h, где k - длина последовательности; я6 - значение i-ro бита последовательности, .«з/ { 0,1); 3 hj - сигнал на входах сумматора по модулю два на i-ом шаге € - суммирование по модулю 2 Обозначим содержимое (г-1) разря дов, у .которых входы сумматора 2 со динены со .счетчиком, индексом г-1, содержимое г-го разряда, для которо го вход сумматора 2 подключен к шин 9 логической единицы, индексом 1. Тогда tr-i . пля : , (2) ДЛЯ hf;/ : Последовательность с ошибками мо но представить в виде .ofcd(-©e, последовательность, содержащая О в правильных битах и IV в битах, где есть ошибка Тогда,воспользовавшись линейность операции XI), можно записать ft(d)-. (d.- . e)l74 -ftU) Т 3) - 1-1jr-l где i, j - номера бит содержащих ошибку} V - количество бит, содержа, J , щих ошибку. Обнаружение и локализация ошибки производится путем анализа суммы Д по модулю два состояния (с( ) регистра 3 для заведомо правильной по следовательности и состоякия /3 (о( ) - для анализируемой последова тельности, возмшсно содержащей ошиб Из формулы (3) следует V () А /3(с(| + 3(с().Ъ2: Подставив значение формулы (2) в формулу (4), получим mod. 1J52- (5) -: i:uj-i). . j:1 , Отсюда вытекают следующие выводы. Для последовательности любой дли ны любые ошибки в нечетком числе бит будут обнаружены, так как t jt Oj для последовательности длиной г при ошибке в одном бите 1, следовательно, такая ошибка однозначно локализуется: 9 (Г-1) i Л- + где i-i номер ошибочного битаг для-последовательности длиной при ошибке в (i,-0 0 (ia-bO, так как-1 , следовательно, лю бая такая ошибка будет обнаружена, П р и м е. р. Пусть число г разрядов регистра, сумматора по модулю два и счетчика будет равно 4 и исходная (эталонная) последовательность будет длиной 17 бит: 01110100001011001. Введем ошиёки в 1, 2, 7, 9 и 13 биты: 01111100100011010 (счет бит идет с конца). Состояния выходов счетчика 1, сумматора 2 по модулю Два, регистра 3 при проверке исходной и ошибочной последовательностей для каждого такта работы анализатора приведены в таблице, причем состояния выходов регистра приведены для момента времени после окончания синхроимпульса соответствующего такта, а состояния выходов счЁ1чика и сумматора по модулю два - для момента времени между передним и задним фронтами синхроимпульса. Сравнение результирующих состояний выходов регистра 3 для исходной и ошибочной последовательностей показывает их несовдадение, что указывает на наличие ошибки (см, таблицу),5 При подключении устройства показания индикатора 5 в случае наличия однобитовой ошибки или двухбитовой ошибки при k будут отличаться от показания для правиль-yf ной последовательности, таким об- разом, эти ошибки будут обнаружены; возможна локализация однобитовой ошибки при k . Кроме того, при любых k возможно выявление ошибок в любом нечетном числе бит, . Так.им образом, подключение счетного входа двоичного счетчика ко входу синхронизации, а последнего з вторьк входом сумматора по модую два к шине логической. Т повыает .достоверность диагностики цифpOBbix устройств с помощью предложен ого логического анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1984 |

|

SU1243099A1 |

| Логический анализатор | 1982 |

|

SU1091339A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Логический анализатор | 1986 |

|

SU1311011A2 |

| Сигнатурный анализатор | 1986 |

|

SU1388869A1 |

| Логический анализатор | 1980 |

|

SU890396A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1430956A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1837291A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1797118A1 |

ЛОГИЧЕСКИЙ АНАЛИЗАТОР,содержащий двоичный счетчик, элемент И, регистр, индикатор и.сумматор по модулю два, выходы которого подключены к соответствующим информационным входам регистра, выходы которого подключены к соответствувяцим входам индикатора и первым входам сумматора по модулю, два, вторые . входы которого, кроме последнего, соединены с соответствующими выходами двоичного счетчика, вход установки в О которого подключен к первому входу устройства и входу установки в О регистра, вход синхронизации которого соединен с вьгкодом элемента И, входы которого подключены к второму и третьему входам устройства соответственно, о т л и ч а ю щ и и с я тем, что, с целью повышения достоверности диагностики, счетный вход двоичного счетчика соеди нен с вторым входом устройства, а i. О) последний из вторых входов cy iatopa с по модулю ДВА подключен к пине логи-. ческой единицы.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроника, 1977, i 5, с | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Логический анализатор | 1982 |

|

SU1091339A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-06-07—Публикация

1983-12-26—Подача