Изобретение относится к цифровой технике, может быть применсию ;(,ля наладки, ремонта и контроля цифровых устройств и является усовер Шен- ствов Шием изобретения по основному авт.св. № 1091339.

Целью изобретения является pacniHрение функциональных возможностей за счет обеспечения локализации двух-, трех- и четырехбитовой ошиГ)ок

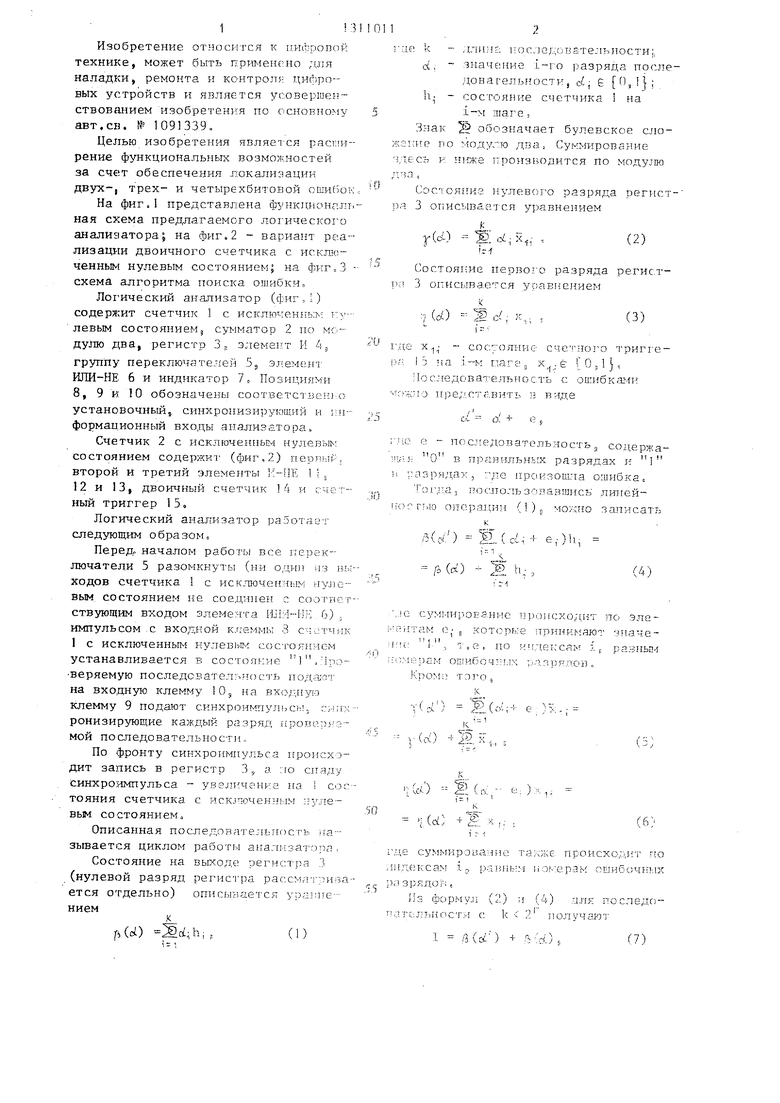

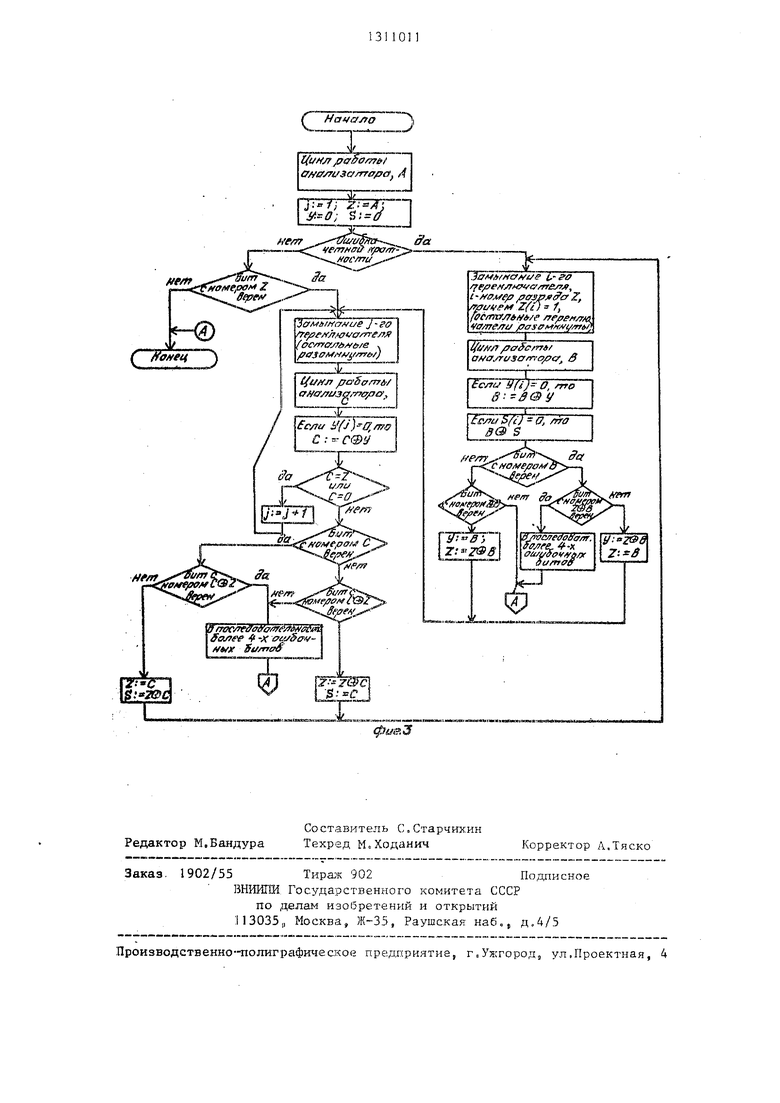

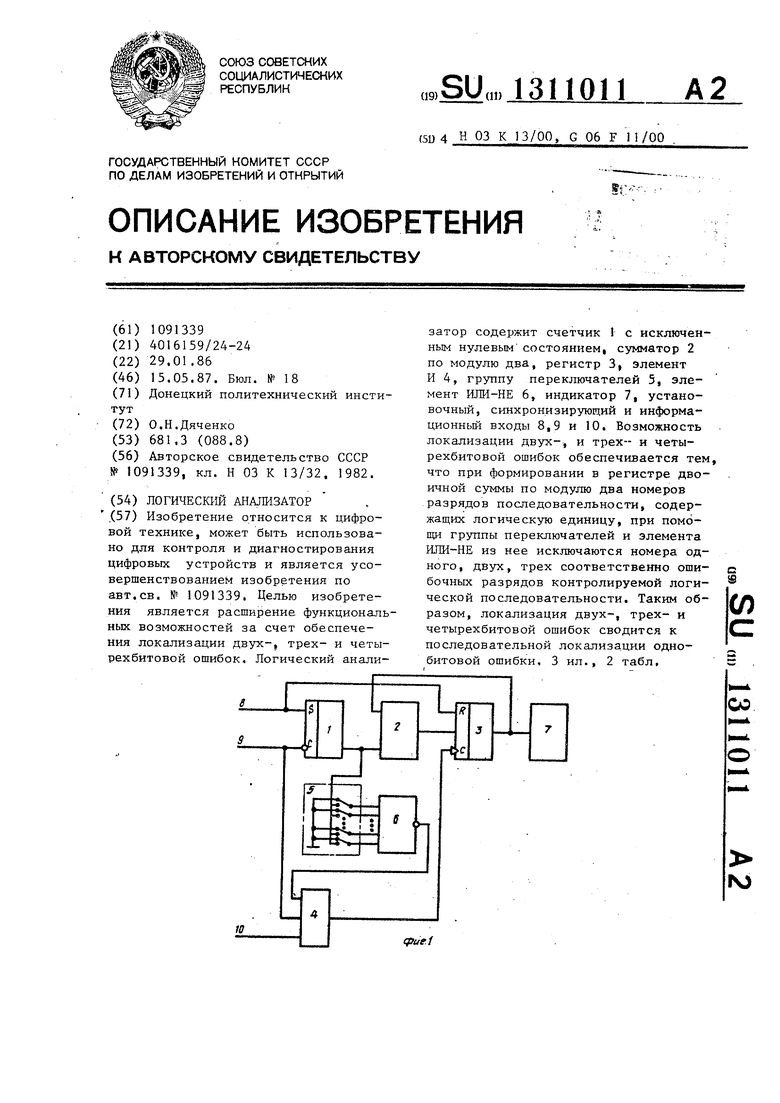

На фиг. представлена функциональная схема предлагаемого логического анализатора; на фиг.2 - вариант реализации двоичного счетчика с исклл ;- ченным нулевым состоянием; на фиг.З схема алгоритма поиска ошибки,

Логический анализатор (фиг,;.) содержит счетчик 1 с исклтченпьз: г:у левым состояниемJ сумматор 2 но мс:- дулю два, регистр 3. элемент 1-1 -i, группу переключателей 5, элемент ШШ-НЕ 6 и индикатор 7, Позициями 8, 9 и 10 обозначены COOTBBTCI ) о установочный, синхронизирующий и lui- формационный входы анализатора.

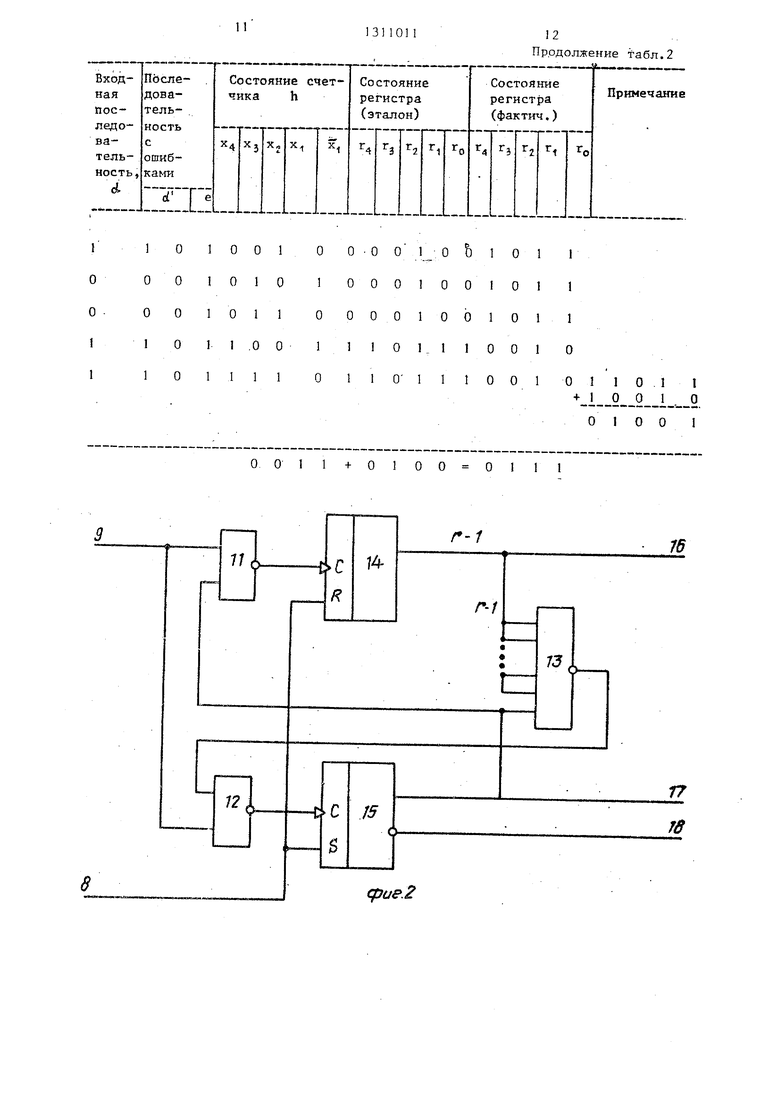

Счетчик 2 с исключен Ы1 1 нулевым: состоянием содержит (сЬиг,2) перпыи, второй и третий элементы 1-1-ПЕ 1 I , 12 и 13, двоичный счетчик 14 и счетный триггер 15.

Логический анализатор работает следующим образом.

Перед, началом работы все лючатеди 5 разомкнуты (ни о/дин из вь ходов счетчика с исключенным нуле;- вым состоянием не соединег с соотвст ствующим входом элеме:чта Ш1А-1К 6) , нмпульсом .с входной к.г;;еммь: 3 счотчик 1 с исключенным нулевьм состоянием устанавливается в состояь ие Г .Мпо- веряемую последовательность поджот на входную клемму 10 на Е(Х(дну|0 клемму 9 подают синхроиг-лпульсь,, г;:.-пг; ронизирующие каждый разряд провер;;-::- мой последовательности.

По фронту синхроимпульса нроисхс - дит запись в регистр 3, а ::го С1таду синхроимпульса - увгличанкг на i тояния счетчика с исклпочевным нуле вым состоянием о

Описанная после/АОВятельпость :ira зьшается циклом работы анагп-гзаторл

Состояние на выходе регистра 3 (нулевой разряд регистра рассмотри ется отдельно) описглнается урашге нием

pW

це k - ти следовательности;; ci, - значение i-ro разряда последовагельности, &( с П,; - состояние счетчика 1 на

1-м aiare,

Знак 25 обозначает булевское сло- кс;1:ие по модулю два Сумм1- рованне л,есь и 1 нже произволится по модулю

1ЧС, ,

Coc.TOHHjie нулевого разряда регистра 3 онисъпзается уравнением

Г(с) - Ш..;Х,; .(2)

1:1

Состояние первого разряда регист- 1; 3 онисывается уравггением

(3)

r,i

ле х.,- - состоя1-Н1е- счетного тригге- i;i 15 на ;i-K пагй,, х.ё Г0,1},

Последовательность с ошибка -1н r vrjio н)5едст; .вить ij виде

ci о + ; f

iic е - носледовательность,, содержа- О в п эавильных разрядах и 1 разряда :, ::м1е нроизотла ошибка. Тог,па, вос-но.чь зппавшись лшгей- гог гью операции (1 ) мокно записать

к й(с/ ) lL(ci;+ e.)h,

(4)

С cyMb HpoESBi- e ттрглгсходит по эле- ьч-rrraN; с ,, :от(рь:е тринимают значе- л К: . а, е, по ил.чексаь i разньп-i :;о;.п;1)ам oniH6oq;;Mx гп1)ял:ов . ро);; тэго ,

T(ci ) е, );.; 1L

v(ci) ., .. (5;

(в

где I i

-1 + l2

+ 1

n

1 - номера разрядов с ошибкой;, n - количество ошибочных разрядов.

Из формул (5), (6).вытекают следующие выводы: любая ошибка нечетной кратности будет обнаружена, Это следует из того, что в случае ошибки нечетной кратности

11

;(х.+ 1)х

-1

li

т.е.

к

где суммирование происходит по индексам i, равным номерам ошибочных разрядов.

В случае ошибок четной кратности или отсутствия ошибок к к

м;

1гк

0.

Из формул (5) - (9) следует, что, если сумма- vi(ci ) + г (о) + J, () + + (d) равна единице, то произопша ошибка нечетной кратности; если эта сумма равна нулю, .то произошла ошибка четной кратности или ошибочных разрядов нет. Таким образом значения нулевого Гр и первого г разрядов регистра 3 позволяют судить о четной или нечетной кратности ошибок.

На фиг. 3 показан порядок локали зации ошибочных разрядов последовательности длиной k ; 2, для которой должны быть известны (г+1) контрольных сумм (одна из них соответствует разомкнутому положению всех переключателей, г остальных - каждому из переключателей в замкнутом положении при разомкнутых (г-1) остальных).

Условные обозначения на фиг.З: - А,В,С - двоичные суммы по модулю два соответствующих показаний индикатора 7 и соответствуюш 1х контрольных сумм; Y(i), S(i) -i-й разряд двоичных

чисел (Y,S); Y(j) j-й разряд двоичного

числа (У);

Y,S - номера локализованных ошибочных разрядов контролируемой последовательности,

Возможность локализации однобитовой ошибки (т.е. указания ошибочно

10

t5

25

30

35

40

45

50

55

го разряда последовательности) обеспечивается тем, что состояния двоичного счетчика 1 с исключенным нулевым состоянием (.его г- - выходов - выходы счетчиков 14,15) соответствуют номерам разрядов контролируемой логической последовательности.

При этом в г разрядах г ...г регистра 3 записана двоичная сумма по модулю два номеров разрядов последовательности, содержащих логическую единипу.

В случае однобитовой ошибки полученная сумма будет отличаться от правильной на состояние счетчика, соответствующее моменту ошибки, т.е. на номер ошибочного разряда, кроме того, сумма по модулю два состояний нулевого г и первого г разрядов регистра 3 будет отличаться от суммы известных правильных состояний этих разрядов,

Осуществив сложение по модулю два полученного содержимого регистра 3 с известным правильным, получают но- Meip ошибочного разряда в последова- .тельности,

Локализация однобитовой ошибки (согласно фиг.З) осуществляется следующим образом. После первого цикла работы анализатора, который производится при разомкнутых переключателях, полученное показание индикатора 7 суммируют по модулю два с соответствующей контрольной суммой. Анализ нулевого и первого разряда полученного числа А покажет, что произошла ошибка нечетной кратности. Проверив бит последовательности с номером А

(нулевой разряд числа А при этом I отбрасывается), убеждаются в том,

что этот бит ошибочен, т.е. действительно имеет место только один ошибочный бит.

Возможность локализации двух-, трех-, четырехбитовой ошибок обеспечивается тем, что при формировании в регистре 3 двоичной суммы по модулю два номеров разрядой последовательности-, содержащих логическую единицу, при помощи группы пе- реключетелей 5 и элемента ИЛИ-НЕ 6 из нее исключаются номера одного, двух, трех соответственно ошибочных разрядов контролируемой логической последовательности. Таким образом локализация двух-, трех-, четырех- битрвой ошибок сводится к последовательной локализации о,;иобито} о ошибки.

Если замкнут 1-й перекшочатель (остальные должны быть разомкнуты) ,. то при формировании в регистре 3 двоичной суммы по модулю два номеров битов последовательностИз, содержащих логическую единицу, из неа исключаются все номера битов посл-е- довательности, в i-м разряде ко . ор ,гл содержится логическая един и и, а,

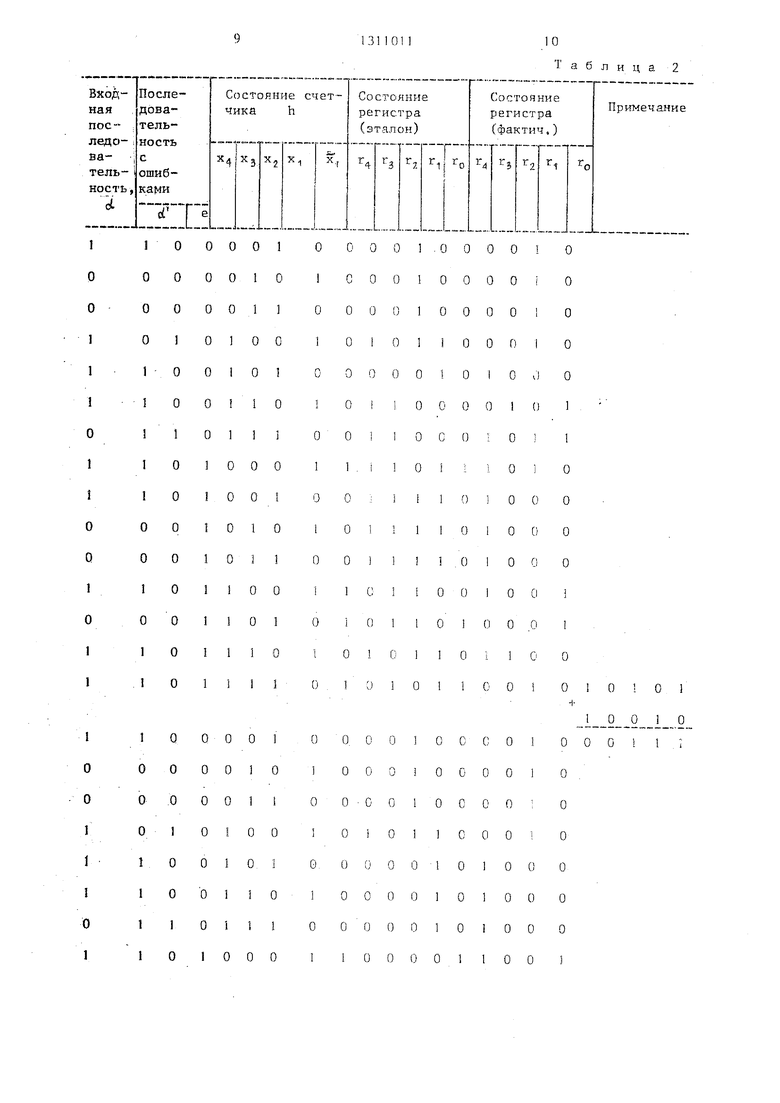

В качестве примера локэ.пизаг1ли ошибочных разрядов рассматривают локализацню однобитовой и двухбитоиол ошибок (табл. 1 и 2),

После первого цикла рабо Г Ь nisr-j;- - затора получают чис:1О А анализ нулевого и первого разр.ядо кс горс1; о показывает 5 что нронзошла О1пкбк;1 четной кратности - сумма по молу. ло два этих разрядов панна нулю, О гбр,- сывая нулевой разряд числа /.. и вая равенство (7). нолучают

А I L, + i,

где i.,|5 i - номера ошнбс чшчх разря;:;ов ,

Так как i., i. , то Л i О,

Согласно фиг . 3 э Zs А н -a:-;h;K. гнется i нереключателт, э нрнчсм i-и разряд числа Z такой что Z(i) --- 1 .

Посхсе проделанного иерекл юч( и еще одного цикла работы ai-iajHi i;rriv pa номер одной из ошибок исключается из суммы, получаемой i- )лл и-:/ ре 3, комер другой остается, :,, полученное число В будет у к;;;лл:г гь номер одного из о чибо пп1(х о.-кг )я гсп номер другого oшибo iH() о дет равен Z + В

Если проверка разридо); ьсс.не мм;; тельности нокгшет,. что оба раз1;:. йерны, то это значит „ что и г:ос:. ,сл;: вательности более четырех оиптбо г-гх битовJ если оши{5очен одил из проверяемьпс разри ов, это означает, что в последовательности четыре oiiKi- бочных бита (в этом случае о :: ( алллыу три нелокализонанных о:иибол1 ых p-rjju да локализуются а1;алог -;чло ч ;( вой ошибке)9

Особенностью локализации ТОБОЙ ошибки является ,,. ч т:) гпрек- пючатели замыкаются последоБате.:,1с один за другим, ьгачина;; с лервог,. и после каждого нереклктчения про;:г,- водится цикл работы а:и1ллзатора ..ю

тех лор, пока ;{ вь:г1о:пл.л ся условиз С i: J, причем С t (J.

Кроме тог о 5 (1собснность лока л-;за- лли ошибочных битов когда один из четырех (трех) опибочньгх битов y)i{e лoкaJrизc)Eaн,

lip;-; четырех ошибочных битах „ как уже отмечалось, лераходят к той нос- л.гдова. 1Л;льЕ10ст ; дейст1Л1Й,, которая - п|П 1е 1иется для ;1ока: изации одного И -rjiex ошибочных 6:-iTCin,. а нрн трех О|:1ибочньгх битах переходят к той пос- лсло1латс;льности действий, которая лр:илл1яется для лок::5Л1 запии двух о:пи- е()ч;Л)К битов,, с той in-:i: b особен- ч:тс нес бхо;;лмг с,т:едить за Разрядами уже лгжагл-лк: )апньк номеров /- пГ Счлых Злтог; Я ,Y (см.фигчЗ);

гл1г заь ьгкается -и лереключа- г мл, (остальньгс: разо:-1клуты) и i-и гомера укс .п()Л Зованного : ::;лг;олл(1го бит : нулю, то к по- J V к:лт1о:чу лока.а1ппл индикатора сум- I ytJTo: Hii то::;7лсс кон7 ро.льлая сум- га по }:. нонар лока.лизованлот о отгн- о:1 л .ого бита ,

Галсль образсм ло -л-ра ;юкализован-- Ч;:л сигол лсключаются кз .-ммм с ло:чера;-:л други5с ошибочных :л :пл и это ;-га(2т Л О змож Л сэ сть , лока- лизплав из че -:;:рех5 например . оплсочлых osjTfiB,. .1 окализо1зать далее :ло1;ой,, трет;л и че гвертьш,

1 л)едла1 ае гый логч т-;еский алалггза- : ч; р У С явол ;ет (лл -; а лоследс j aTejTb- Л:.л-тл Tie Сслк;;.; 2 ) : облар -жлть и ьЛ:. fii iojiaTb Д;юбу10 слрхюи 1ЛМ1ую слпиб- i.y лбла и jios аллзолать люблтс ;ч(5;ггодую оллбкл ( i ,, - ) i обX

- ;1:р;; ЖЛ ; Л Л .лш; 7 Л; кл ; ..ть ;no6yio :ЛЛ;Х- ,)1 лбк / (л- - ; ; o .f c:i,ine; ч;л:г . , ,., .; , U- яа слет тогОс . :): Л1ару :-:ллл : :ЛЛ- . поба;-; оп; 5Г;{лг не- . кра гл)г 1 и); локали юла .:Л)

о 1ноблтовой шглока i ; ,л;укблтолсч : ,-; ; : чохб ттолой о У1гбка ); ;

. )ЛХбЛ С;Л 1Л r); i if:i ;p ) .

713

Формула изобретения

Логический анализатор по авт.св. № 1091339, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения локапизации двух-, трех- и четырехбитовой ошибок, он содержит элемент И-НЕ и группу переключателей, подвижные контакты

0011

8

которых соединены .с входами элемента ИЛИ-НЕ, выход которого соединен с третьим входом элемента И замыкающие контакты группы переключате- лей подключены к соответствующим разрядным выходам двоичного счетчика с исклзоченным нулевым состоянием, размыкающие контакты группы переключателей объединены и подключены к гаине нулевого потенциала,

Т а б л и ц I

10 Таблица 2

001 1 + О

00 01 1 1

с

Hai/a/ro

1(инл jucfSo/rfert I a/ cf/Ti/за/ттара A

,J

7Tr7; fTS7j - . S;

ffa

vefnHffu .4:гяэw -- - ac/nu

/fOf/ft4 }

JffMA/ffO iVi/ff J-fff

fre/je/f/Tfoi/a/rre/rj ( - /fffSi Miff/yfrTti/)

:k

jytySarrri,/ cffiaf/7ej3a,v7a/3O,,

О

EZ

С . - г®у

//л

в ffOC/reffaifaflrfyfMfffm Sa/yef -X ffo/Sffv- fK St/ff

имиJi .tH Je J

TS7j - ;

3af iifticff i/e I,-ffo /je/3eff K a/rr&/r/, i-//ff f/7 /ypyaj ffcr Z, o-ai/vfM Z{t) 1, lecmw/rirffir/c /геоен/гм Va/fT(JTtj aas MffjVum

/fc C frrtf она./ге/зато с/, S

сли ffij- О, mo e:-S&y

) (7, ma

eijma/feooffa/rr. ,. -x ff ifffffwg/jf aufrrffff

|g.

LS. C.J

Редактор M,Бандура

Составитель С.Старчихин Техред М.Ходанич

Заказ. 1902/55 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035,, Москва, Ж-35, Раушская наб.5 д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор А.Тяско

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1983 |

|

SU1160569A1 |

| Логический анализатор | 1982 |

|

SU1091339A1 |

| Сигнатурный анализатор | 1984 |

|

SU1193680A2 |

| Сигнатурный анализатор | 1981 |

|

SU962962A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1430956A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1837291A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1797118A1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

Изобретение относится к цифровой технике, может быть использовано для контроля и диагностирования цифровых устройств и является усовершенствованием изобретения по авт.св. № 1091339. Целью изобретения является расширение функциональных возможностей за счет обеспечения локализации двух-, трех- и четырехбитовой ошибок. Логический анализатор содержит счетчик I с исключенным нулевым состоянием, сумматор 2 по модулю два, регистр 3, элемент И 4, группу переключателей 5, элемент ИЛИ-НЕ 6, индикатор 7, установочный, синхронизирующий и информационный входы 8,9 и 10. Возможность локализации двух-, и трех- и четырехбитовой ошибок обеспечивается тем, что при формировании в регистре двоичной суммы по модулю два номеров разрядов последовательности, содержащих логическую единицу, при помощи группы переключателей и элемента ИЛИ-НЕ из нее исключаются номера одного, двух, трех соответственно ошибочных разрядов контролируемой логической последовательности. Таким образом, локализация двух-, трех- и четырехбитовой ошибок сводится к последовательной локализации однобитовой ошибки. 3 ил., 2 табл. (Л го (puei

| Логический анализатор | 1982 |

|

SU1091339A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1987-05-15—Публикация

1986-01-29—Подача