Изобретение относится к автоматике и вычислительной технике, в частности к техническим средствам сбора и обработки информации, и может быть использовано для организагщи диалогового режима обмена информацией в системах коллективного цользования вычислительными ресурсами, мультипрограммных вычислительных системах, комплексах и классах для автоматизированного обучения.

Целью изобретения является повышение быстродействия и расширение функциональных возможностей за счет секционирования общего поля оперативной памяти и совмещения во времени операций обмена информацией свободных от связи с процессором, блоков оперативной памяти с периферийными устройствами.

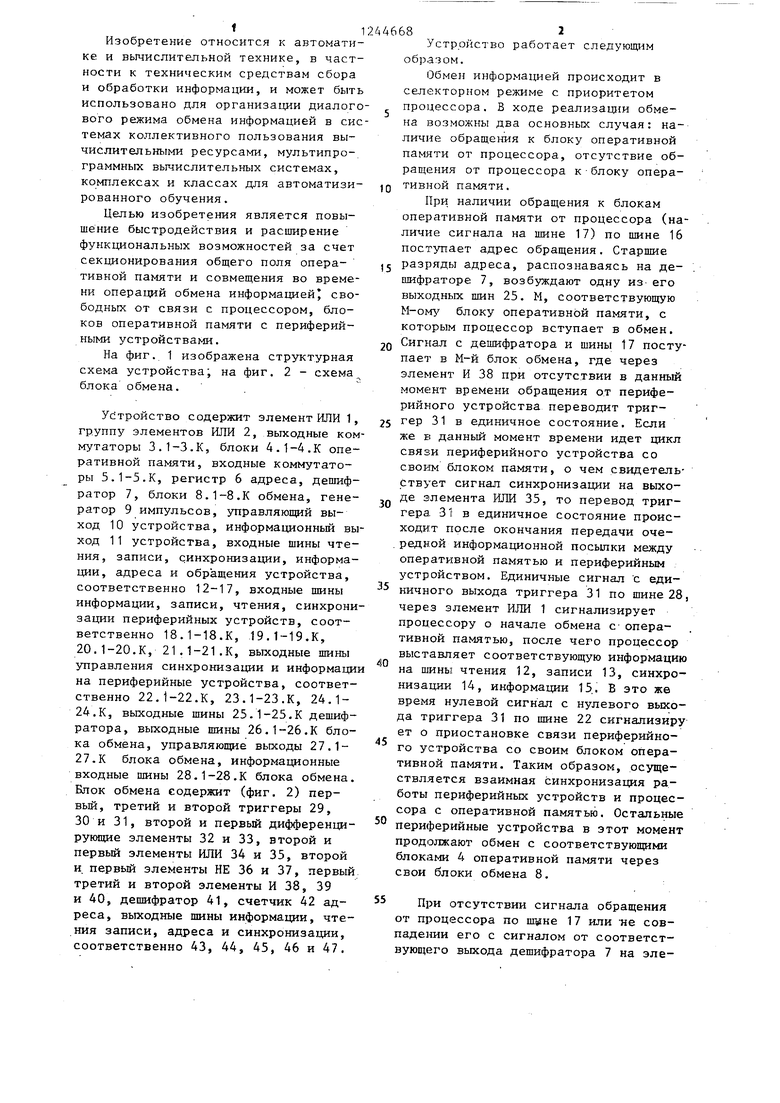

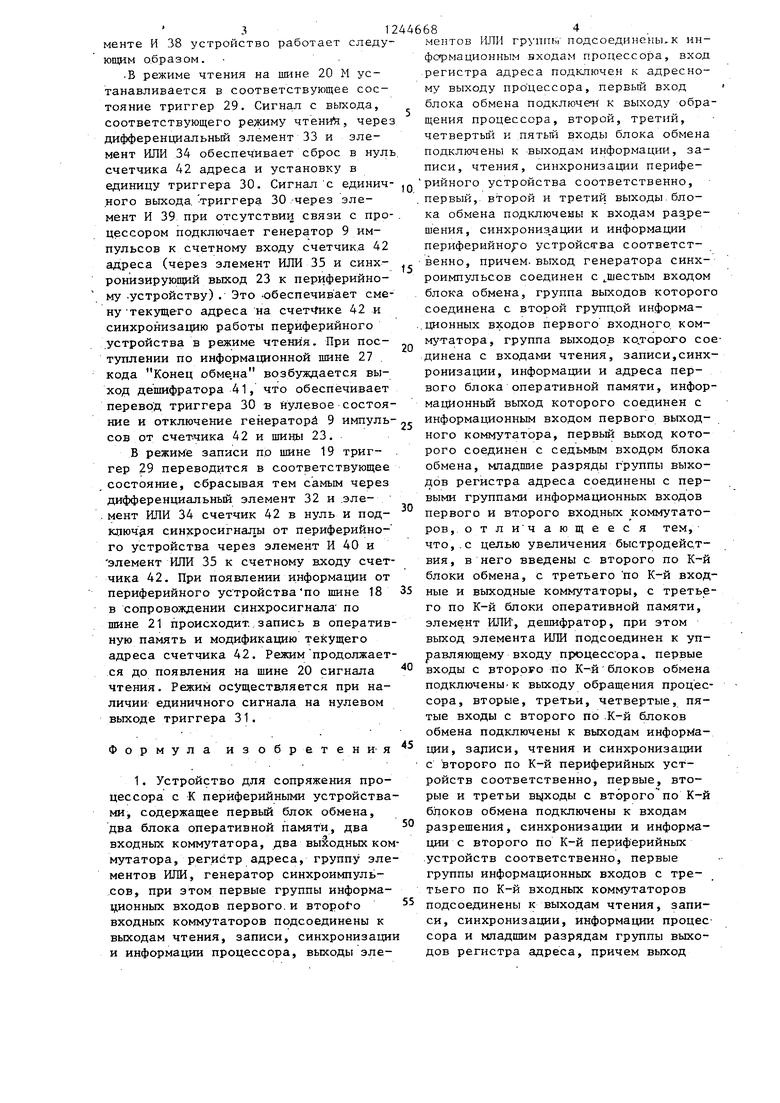

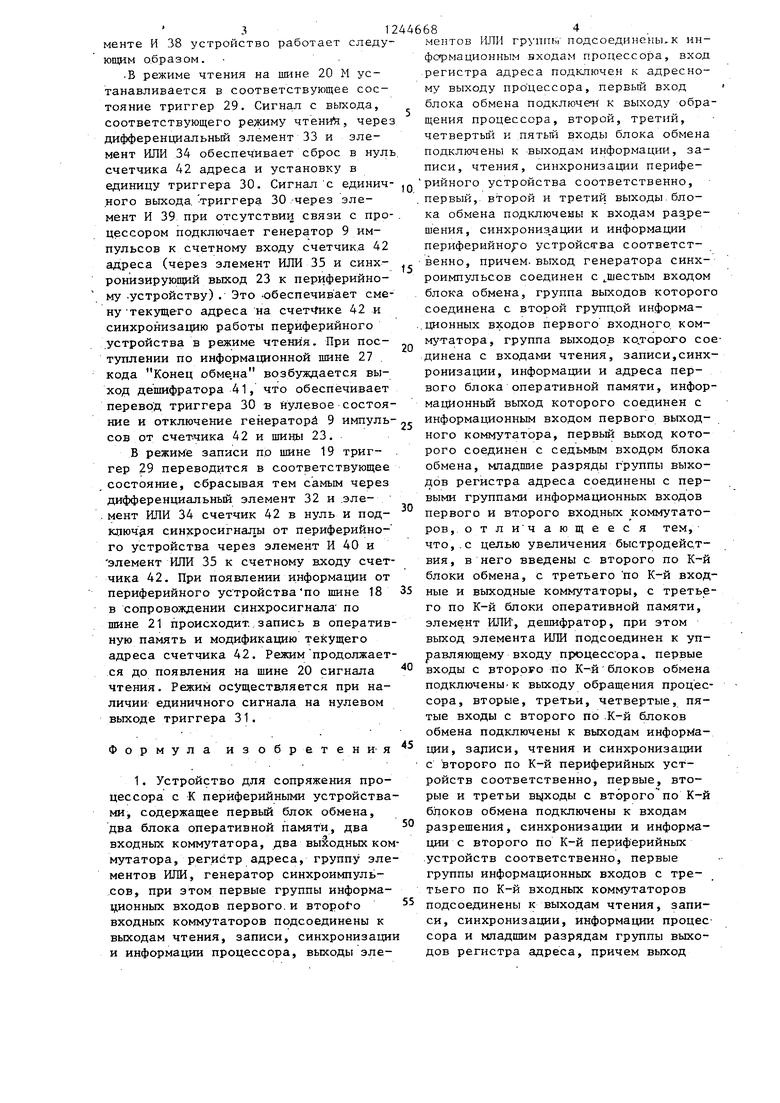

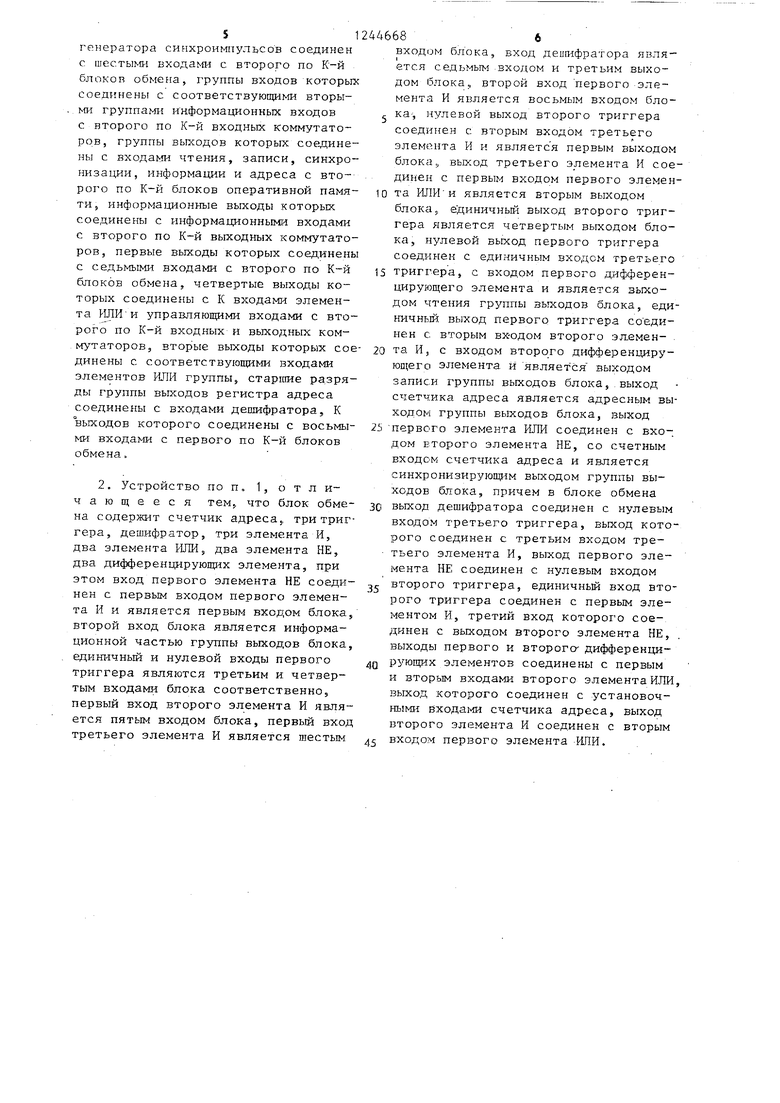

На фиг. 1 изображена структурная схема устройстваi на фиг. 2 - схема блока обмена. .

Устройство содержит элемент ИЛИ 1, группу элементов ИЛИ 2, выходные коммутаторы 3.1-3.К, блоки 4.1-4.К оперативной памяти, входные коммутаторы 5.1-5.К, регистр 6 адреса, дешифратор 7, блоки 8.1-8.К обмена, генератор 9 импульсов, управляющий выход 10 устройства, информационньш выход 11 устройства, входные шины чтения, записи, синхронизации, информации, адреса и обращения устройства, соответственно 12-17, входные шины информации, записи, чтения, синхронизации периферийных устройств, соответственно 18.1-18.К, 19,1-19.К, 20.1-20.К, 21.1-21.К, выходные шины управления синхронизации и информаци на периферийные устройства, соответственно 22.1-22.К, 23.1-23.К, 24.1- 24.К, выходные шины 25.1-25.К дешифратора, выходные шины 26.1-26.К блока обмена, управляющие выходы 27.1- 27.К блока обмена, информационные входные шины 28.1-28.К блока обмена. Блок обмена содержит (фиг. 2) первый, третий и второй триггеры 29, 30 и 31, второй и первый дифференцирующие элементы 32 и 33, второй и первый элементы ИЛИ 34 и 35, второй и, первьй элементы НЕ 36 и 37, первый третий и второй элементы И 38, 39 и 40, дешифратор 41, счетчик 42 адреса, выходные шины информации, чтения записи, адреса и синхронизации, соответственно 43, 44, 45, 46 и 47.

0

5

Устройство работает спецующцм образом.

Обмен информахщей происходит в селекторном режиме с приоритетом процессора. В ходе реализации обмена возможны два основных случая: наличие обращения к блоку оперативной памяти от процессора, отсутствие об- ращ(гния от процессора к блоку оперативной памяти.

При наличии обращения к блокам оперативной памяти от процессора (наличие сигнала на шине 17) по шине 16 поступает адрес обращения. Старшие

5 разряд1 1 адреса, распознаваясь на де- . шифраторе 7, возбуждают одну из-его выходных шин 25. М, соответствующую М-ому блоку оперативной памяти, с которым процессор вступает в обмен. Сигнал с дешифратора и шины 17 поступает в М-й блок обмена, где через элемент И 38 при отсутствии в данный момент времени обращения от периферийного устройства переводит триггер 31 в единичное состояние. Если же в данный момент времени идет цикл связи периферийного устройства со своим блоком памяти, о чем свидетельствует сигнал синхронизации на выходе элемента ИЛИ 35, то перевод триггера 31 в единичное состояние происходит после окончания передачи оче- .редкой информационной посылки между оперативной памятью и периферийным устройством. Единичные сигнал с еди ничного выхода триггера 31 по шине 28, через элемент ИЛИ 1 сигнализирует процессору о начале обмена С оперативной памятью, после чего процессор выставляет соответствующую информацию на шины чтения 12, записи 13, синхронизации 14, информации 15.. В это же время нулевой сигнал с нулевого выхода триггера 31 по щине 22 сигнализиру ет о приостановке связи периферийного устройства со своим блоком оперативной памяти. Таким образом, осуществляется взаимная синхронизация работы периферийных устройств и процессора с оперативной памятью. Остальные

периферийные устройства в этот момент продолжают обмен с соответствующими блоками 4 оперативной памяти через свои блоки обмена 8.

5 При отсутствии сигнала обращения от процессора по 17 или не совпадении его с сигналом от соответствующего выхода дешифратора 7 на эле0

0

5

3

1244 следу10.

15

20

25

енте И 38 устройство работает шим образом.

В режиме чтения на шине 20 М устанавливается в соответствующее состояние триггер 29. Сигнал с выхода, соответствующего режиму чтений, через дифференциальный элемент 33 и элемент ИЛИ 34 обеспечивает сброс в нуль счетчика 42 адреса и установку в единицу триггер-а 30. Сигнал с единичного вьпсода, -триггера 30 -через элемент И 39 при отсутствии связи с процессором подключает генератор 9 импульсов к счетному входу счетчик.а 42 адреса (через элемент ИЛИ 35 и синхронизирующий выход 23 к периферийному .устройству) , Это -обеспечивает смену текущего адреса на 42 и синхронизацию работы периферийного устройства в режиме чтения. При поступлении по информационной шине 27 . кода Конец обме.на возбуждается выход дешифратора 41, что обеспечивает перевод триггера 30 в нулевое состояние и отключение генератор 9 импульсов от счетчика 42 и шины 23.

Б режиме записи по шине 19 триггер 29 переводится в соответствующее состояние, сбрасывая тем самым через дифференциальньй элемент 32 и .эле- мент ИЛИ 34 счетчик 42 в нуль и под- синхросигналы от периферийно- го устройства через элемент И 40 и элемент ИЛИ 35 к счетному входу счетчика 42, При появлении информации от периферийного устройства по шине 18 35 в сопровождении синхросигнала по шине 21 происходит..запись в оперативную память и модификацию текущего адреса счетчика 42. Режим продолжается до появления на шине 20 сигнала ° чтения. Режим осуществляется при наличии единичного сигнала на нулевом выходе триггера 31.

Формула изобретени-я

1. Устройство для сопряжения процессора с К периферийными устройствами, содержащее первьй блок обмена, два блока оперативной памяти, два входных коммутатора, два выходных коммутатора, регистр адреса, группу элементов ИЛИ, генератор синхроимпульсов, при этом первые группы информационных входов первого.и BTopofo входных коммутаторов подсоединены к выходам чтения, записи, синхронизации и информации процессора, выходы эле30

244668 10.

15

20

25

з ь35

30

ментов ИЛИ гр )) подсоединены., к информационным в.ходам процессора, вход регистра адреса подключен к адресному выходу процессора, первый вход блока обмена подключе-м к выходу обращения процессора, второй, третий, четвертьш и пятьй входы блока обмена подключены к выходам информации, записи, чтения, синхронизации перифе- рийного устройства соответственно, .первый, второй и третий выходы.блока обмена подключены к входам шения, синхрониз,ации и информации пepифepийнo o устройства соответственно, причем, выход генератора синхроимпульсов соединен с шестым входом блока обмена, группа выходов которого соединена с второй групп,ой информа- .ционных входов первого входного, коммутатора, группа выходов Kojroporo соединена с входами чтения, записи,синхронизации, информации и адреса первого блока оперативной памяти, инфор- мационньй выход которого соединен с информационным входом первого выходного коммутатора, первый выход которого соединен с седьмым входрм блока обмена, мпадшие разряды группы выходов регистра адреса соединены с первыми группами информационных входов первого и второго входных коммутаторов, отли чающееся тем, что,.с целью увеличения быстродействия, в него введены с второго по К-й блоки обмена, с третьего по К-й входные и выходные коммутаторы, с третьего по К-й блоки оперативной памяти, элемент ИЛИ , дешифратор, при этом выход элемента ИЛИ подсоединен к управляющему входу процессора, первые входы с второго по К-й блоков обмена подключены-к выходу обращения процессора, вторые, третьи, четвертые, пятые входы с второго по .К-й блоков обмена подключены к выходам информации, зариси, чтения и синхронизации с второго по К-й периферийных устройств соответственно, первые, вторые и третьи вцходы с второго по К-й блоков обмена подключены к входам разрешения, синхронизации и информации с второго по К-й периферийных .устройств соответственно, первые группы информационных входов с третьего по К-й входных коммутаторов подсоединены к выходам чтения, записи, синхронизации, информации процес сора и младшим разрядам группы выходов регистра адреса, причем выход

генератора синхроимпульсов соединен с шесть ш входами с второго по К-й блоков обмена, группы входов которых соед1 нены с соответствующими вторыми группами информационных входов с второго по К-й входных коммутаторов, группы выходов которых соединены с входами чтения, записи, синхронизации, информации и адреса с второго по К-й блоков оперативной памяти, информационные выходы которых соединены с информационными входами с второго по К-й выходных коммутаторов, первые выходы которых соед,инены с седьмыми входами с второго по К-й блоков обмена, четвертые выходы которых соединены с К входам ч: элемента ИЛИ И управляющими входами с второго по К-й входных и выходных коммутаторов, вторь е выходы которых соединены с соответствующими )зходами элементов ШТИ группы, старшие разряды группы выходов регистра адреса соединены с входами дешифратора, К выходов которого соединены с восьмыми входами с первого по К-й блоков обмена.

2. Устройство по по 1, отличающееся тем., что блок обмена содержит счетчик адреса,, три триггера, дешифратор, три элемента И, два элемента ИЛИ, два элемента НЕ, два дифференцирующих элемента, при этом вход первого элемента НЕ соединен с первым входом первого элемента И и является первым входом блока второй вход блока является информационной частью группы выходов блока единичный и нулевой входы первого триггера являются третьим и четвертым входами блока соответственно, первый вход второго элемента И является пятым входом блока, первый вход третьего элемента И является шестым

входом блока, вход деиифратора явля-- ется седьмым входом и третьим выходом блока,, второй вход первого элемента И является восьмым входом бло- , ка, нулевой выход второго триггера соединен с вторым входом третьего элемента И и являетс я первым выходом блока, выход третьего элемента И соединен с первым входом первого элемен- 0 та ИЛИ И является вторым выходом блокаJ единичный выход второго триггера является четвертым выходом блока, нулевой выход первого триггера соединен с единичным входом третьего 5 триггера, с входом первого дифференцирующего элемента и является выходом чтения группы выходов блока, еди- ничньш выход первого триггера соединен с вторым вхюдом второго эл.емен0 та И, с входом второго дифференцирующего элемента И являемся выходом записи группы выходов блока,,выход счетчика адреса является адресным выходом группы выходов блока, выход

5 первого элемента ИЛИ соединен с входом второго элемента НЕ, со счетным входом счетчика адреса и является синхронизирующим выходом группы выходов блока, причем в блоке обмена

0 выход дешифратора соединен с нулевым входом третьего триггера, выход которого соединен с третьим входом третьего элемента И, выход первого элемента НЕ соединен с нулевым входом

J второго триггера, единичный вход второго триггера соединен с первым элементом И, третий вход которого соединен с выходом второго элемента НЕ, выходы первого и второго- дифференциQ рующих элементов соединены с первым и вторым входами второго элемента ИЛИ, выход которого соединен с установоч- р-шми входа1чи счетчика адреса, выход второго элемента И соединен с вторым

5 входом первого элемента ОТИ.

tf/

в.п

L

птгта

глпянгапи

ПГ

Hi

ЛП19./170.пг1./Г 22.Л21П Л /У

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для сопряжения в многотерминальной вычислительной системе | 1984 |

|

SU1166124A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

Изобретение относится к области автоматики и вычислительной техники, в частности к техническим средствам сбора и обработки информации, и может быть использовано для организации диалогового режима обмена информацией в системах коллективного пользования вычислительными ресзфсами, мультипрограммных вычислительных системах, комплексах и классах для автоматизированного обучения. Основной целью изобретения является повьшение быстродействия и расширение функциональных возможностей. Устройство содержит элемент ИЛИ, группу элементов ИЛИ, выходные коммутаторы, блоки оперативной памяти, входные коммутаторы, регистр адреса, дешифратор, блоки обмена, генератор импульсов. 1 з.п. ф-лы, 2 ил. с $ (Л ю 4; 4 Од О) 00

фив. I

/7 /5

27 28 Q О

-NK XXX

Т Ф

J

| 2

I 35 1 А ф

18 19 20 21

о от 9

Редактор Л.Повхан

Составитель С.Пестмал

Техред М.Ходанич Корректор О.Луговая

Заказ 3919/52Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

J f . О О

22 2 24

Фиг. 2

Авторы

Даты

1986-07-15—Публикация

1984-09-26—Подача