23

СП

4.

О

и

Изобретение относится к вычислительной технике, а именно к устройствам коррекции ошибок в запоминающем устройстве с последовательным досту- пом.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения кодирования информации.

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема адресного блока; на фиг. 3 структурная схема блока обращения; на фиг. 4 - структурная схема блока обнаружения ошибок; на фиг. 5 структурная схема блока сравнения .

Устройство для коррекции ошибок содержит блок 1 обнаружения ошибок, блок 2 памяти, блок 3 обращения, адт ресный блок 4, счетчик 5, блок б коррекции, блок 7 сравнения, шинный формирователь 8, первый 9, второй 10 и третий 11 коммутаторы, первый 12 и второй 13 сдвиговые регистры, входы 14-20, выходы 2t и 22, информационные входы/выходы 23 устройства,,

Адресный блок 4 (фиг. 2) содержит счетчик 24, коммутатор 25, элемент И 26.

Блок 3 обращения (фиг. 3) содержит (элементы И 27 и 28, коммутатор 29л (элемент ИЛИ-НЕ 30. элементы НЕ 31 и $2, элемент ИЛИ 33 элемент 3 задерж Ки, формирователь 35 импульсов обращения к блоку 2 памяти, который необходимо включить на выход коммутатора 29 для приема нестандартного сигнала по входу 17.

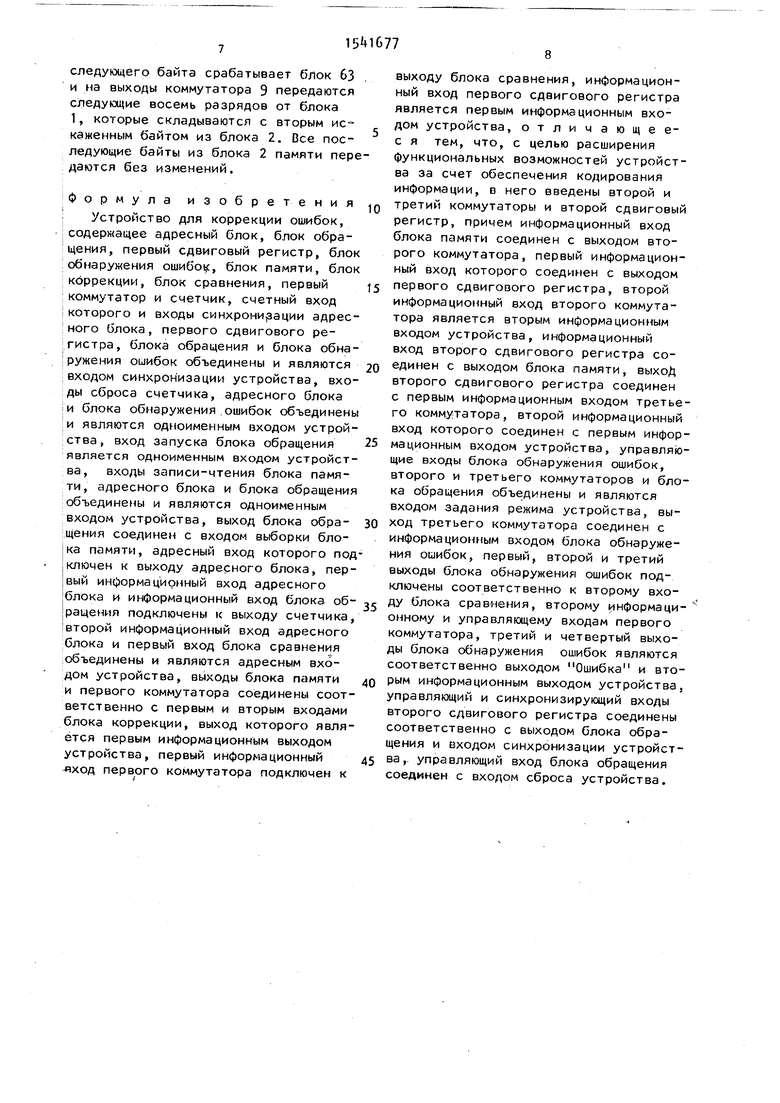

Блок 1 обнаружения ошибок (фиг. 4) содержит триггеры 3& 49, сумматоры SO - 54 по модулю два, элемент НЕ 55, Элемент И-ИЛИ 56, счетчик 57 триггер 58, элемент И 59, элемент ИЛИ 60 и умножитель 61. Блок реализует процедуры кодирования и декодирования на основе кода Оайра, задаваемого полиномом

Р(х) ()(х4+х +1).

Длина кода разрядов, количество проверочных разрядов 14. Код позволяет корректировать пакеты ошибок разрядностью 45 Количество триггеров Зб - 49 соответствует наибольшей степени х в полиноме Р(х). Сумматоры 50- 54 располагаются за триггерами, соот

0 5

0

0

5

0

5

ветствуюцими ненулевым степеням х в полиноме Р(х).

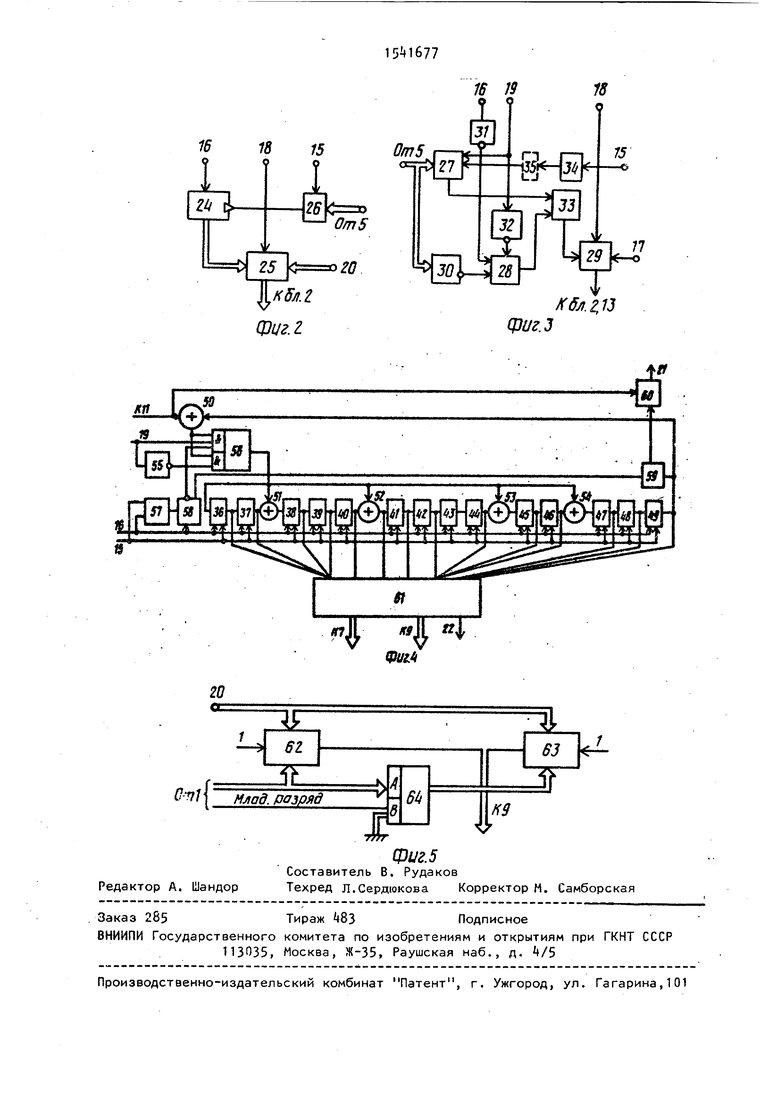

Блок 7 сравнения (фиг. 5) содержит два блока 62 и 63 сравнения и сумматор 64.

Устройство работает следующим образом.

Перед началом операций кодирования и декодирования производится сброс блоков 1, 4 и 5 по входу 1б устройства.

Операция кодирования информации включает в себя два этапа.

Первый этап. Прием в блок 2 памяти. На вход 19 подается управляющий сигнал, позволяющий информации по входам/выходам 23 через шинный формирователь 8 и коммутатор 10 поступать на информационные входы блока 2 памяти. Па вход 18 подают сигнал управления записью в блок 2 памяти. Затем, последовательно подавая коды адресов по входам 20 и синхронно с ними чисел по входам 23, а также сигнал обращения по входу 17, записывают блок информации в блок 2 памяти.

Второй этап. Кодирование информации в блоке 1. На входе 18 устанавливают сигнал управления считыванием из блока 2 памяти. Блок 1 и коммутатор 11 сигналом к входу 19 открыты для поступления информации с регистра 13. Предполагают, что блок 2 памяти хранит байтовые слова„ Па вход 17 подают сигнал, позволяющий информацию, записанную по первому адресу в блоке 2 памяти, переписать в параллельном коде в сдвиговый регистр 13. Затем подают синхросигналы на вход 15 устройства, и информация из регистра 13 через коммутатор 11 сдвигается и поступает в блок 1, откуда через элемент ИЛИ 60 она передается на внешний накопитель (на фиг. 1 и 4 не показан). При этом, после окончания каждого очередного восьмого импульса, поступающего по входу 15, в блоке 4 происходит изменение адреса, что позволяет обратиться к блоку 2 памяти по следующему адресу, а в блоке 3 обращения вырабатывается сигнал обращения к блоку 2 па- / мяти, что позволяет считать очередное байтовое слово и записать его в регистр 13. Так последовательно производится считывание всего блока информации из блока 2 памяти и прохождение его через регистр с обратной связью, образованный триггерами

и сумматорами по модулю два. После приема всей информации триггеры 36-49 содержат контрольные разряды кода, которые через элементы И J39 и ИЛИ 60 поступают на внешний накопитель.

Операция декодирования также включает два этапа.

Первый этап. Прием информации от внешнего накопителя в блок 2 памяти, обнаружение оыибок. На вход 19 подается управляющий сигнал, открывающий коммутатор 10 на передачу информации в блок 2 памяти из регистра 12, шинный формирователь 8 - на передачу информации из блока 2 памяти через блок 6 коррекции на выходы 23, коммутатор 11 - на передачу информации с входа 14 на вход блока 1, блок 1 - на декодирование информации. На вход 18 подают сигнал управления записью в блок 2 памяти. На вход 14 от внешнего наследующие 16 разрядов предстазляют собой чередование О и 1 в соответствии с тем, как искажена инфоомация;

последний разряд является индикатором и содержит 1 или О в зависимости от того, корректируемая или некорректируемая ошибка место.

Например, если на выходе умножителя

61 имеют 000101100000111110000001, это означает, что первым ошибочным байтом является байт; 1 в седьмом разряде означает, что ошибка захватывает и 6-й байт; пакет ошиб5 ки разрядностью пять бит исказил три последних разряда байт и два первых 6-го байта; ошибка корректируемая .

Второй этап. Коррекция ошибок.Этот

0 этап начинается подачей по входу 18 сигнала управления считыванием из блока 2 памяти. Наличие сигналов обращения от блока 3 и адресной информации на входах 20 обеспечивает выборку дан

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Устройство для коррекции ошибок в блоках памяти с последовательным доступом | 1987 |

|

SU1510014A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372366A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

Изобретение относится к вычислительной технике, а именно к устройствам коррекции ошибок в запоминающих устройствах (ЗУ) с последовательным доступом. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения кодирования информации при ее записи в ЗУ. Устройство для коррекции ошибок содержит блок 1 обнаружения ошибок, блок 2 памяти, блок 3 обращения, адресный блок 4, счетчик 5, блок 6 коррекции, блок 7 сравнения, шинный формирователь 8, первый 9, второй 10, третий 11 коммутаторы, первый 12 и второй 13 сдвиговые регистры. В устройстве совмещены функции кодирования и декодирования. 5 ил.

копителя в последовательном коде лода- 25ных из блока 2 памяти, поступающих на

ют информацию, сопровождаемую синхро-блок 6 коррекции, сигналами по входу 15. После каждого В каждом такте адрес очередного

восьмого импульса, поступающего побайта поступает на блок 7 сравнения,

входу 19, производится выработка сиг-Он состоит из двух блоков 62 и 63. На

нала обращения к блоку 2 памяти бло- 30входы первой группы каждого из них ком 3 обращения, и информация из сдвипоступает текущий адрес по входам 20, на входы второй группы - соответствен но адреса первого и второго ошибочных байтов, причем адрес второго ошибочгового регистра 12 через коммутатор 10 в параллельном коде записывается в блок 2 памяти. Затем в адресном блоке 4 производится изменение адреса наЗв ного байта формируется путем сложения следующий и так повторяется до техадреса первого ошибочного байта с со- -пор, пока весь блок информации не бу-деожимым седьмого разряда в суммато- дет принят в блок 2. Одновременно информация по входу 14 через коммутатор 11 поступает в блок 1 обнаружения оши-40 на коммутатор 9- Другие входы комму- бок. После того, как будут принятытатора 9 соединены с выходами блока 1

ре 64.

Сигналы с блоков 62 и 63 поступают

все 279 разрядов, на выходе умножителя 61 формируется следующая информация. Если при передаче информации ошибки не произошло, на выходах всех триггеров 36-49 - нули, на всех выходах умножителя 61 - нули. | Сели в принятой от внешнего накопителя информации содержится ошибка, после 279 тактов не все триггеры 36 - 49 содержат нули. На выходах умножителя 61 имеют:

первые семь разрядов определяют адреса ошибочных байтов, причем шесть

из них представляют собой адрес перво 55 лю два с байтом от коммутатора 9, в го ошибочного байта, а седьмой прини- котором три последних разряда являются дополнением к искаженным. На выходе блока 6 имеют скорректированную информацию. При поступлении адреса

мает решение О или 1 в зависимости от того, расположен ли пакет ошибок в одном или двух байтах;

входы первой группы каждого из них

поступает текущий адрес по входам 20, на входы второй группы - соответственно адреса первого и второго ошибочных байтов, причем адрес второго ошибочного байта формируется путем сложения адреса первого ошибочного байта с со- деожимым седьмого разряда в суммато- на коммутатор 9- Другие входы комму- татора 9 соединены с выходами блока 1

ре 64.

Сигналы с блоков 62 и 63 поступают

обнаружения ошибок (1б-ью информационными разрядами).

До тех пор, пока адрес считываемого байта не совпадает с номерами ошибочных байтов, информация от блока 2 памяти без изменения передается через шинный формирователь 8 на входы/выходы 23. При сравнении адреса очередного байта с номером первого ошибочного байта через коммутатор 9 на блок 6 коррекции передаются первые восемь разрядов. В результате искаженный байт из блока 2 складывается по модулю два с байтом от коммутатора 9, в котором три последних разряда являются дополнением к искаженным. На выходе блока 6 имеют скорректированную информацию. При поступлении адреса

следующего байта срабатывает блок 63 и на выходы коммутатора 9 передаются следующие восемь разрядов от блока 1, которые складываются с вторым искаженным байтом из блока 2. Все последующие байты из блока 2 памяти передаются без изменений.

Формула изобретения

Устройство для коррекции ошибок, содержащее адресный блок, блок обращения, первый сдвиговый регистр, блок обнаружения ошибок, блок памяти, блок коррекции, блок сравнения, первый коммутатор и счетчик, счетный вход которого и входы синхронизации адресного блока, первого сдвигового регистра, блока обращения и блока обнаружения оиибок объединены и являются входом синхронизации устройства, входы сброса счетчика, адресного блока и блока обнаружения ошибок объединены и являются одноименным входом устройства, вход запуска блока обращения является одноименным входом устройства, входы записи-чтения блока памяти , адресного блока и блока обращения объединены и являются одноименным входом устройства, выход блока обра- щения соединен с входом выборки бло- 1 ка памяти, адресный вход которого под iключей к выходу адресного блока, пер- |вый информационный вход адресного блока и информационный вход блока об- рацения подключены к выходу счетчика, второй информационный вход адресного блока и первый вход блока сравнения объединены и являются адресным входом устройства, выходы блока памяти и первого коммутатора соединены соответственно с первым и вторым входами блока коррекции, выход которого является первым информационным выходом устройства, первый информационный «ход первого коммутатора подключен к

выходу блока сравнения, информационный вход первого сдвигового регистра является первым информационным входом устройства, отличайте е- с я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения кодирования информации, в него введены второй и третий коммутаторы и второй сдвиговый регистр, причем информационный вход блока памяти соединен с выходом второго коммутатора, первый информационный вход которого соединен с выходом первого сдвигового регистра, второй информационный вход второго коммутатора является вторым информационным входом устройства, информационный вход второго сдвигового регистра соединен с выходом блока памяти, выход второго сдвигового регистра соединен с первым информационным входом третьего коммутатора, второй информационный вход которого соединен с первым информационным входом устройства, управляющие входы блока обнаружения ошибок, второго и третьего коммутаторов и блока обращения объединены и являются входом задания режима устройства, выход третьего коммутатора соединен с информационным входом блока обнаружения оиибок, первый, второй и третий выходы блока обнаружения ошибок подключены соответственно к второму входу блока сравнения, второму информационному и управляющему входам первого коммутатора, третий и четвертый выходы блока обнаружения ошибок являются соответственно выходом Ошибка и вторым информационным выходом устройства управляющий и синхронизирующий входы второго сдвигового регистра соединены соответственно с выходом блока обращения и входом синхронизации устройства, управляющий вход блока обращения соединен с входом сброса устройства.

$.

18 15

I

й От 5

20

K5fi.Z Фиг. 2.

Kit

п

р§ «ф

Фигл

15

77

фиг.З

Кбл.2,П

| Патент ША № 4216521, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372366A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-02-07—Публикация

1987-12-30—Подача