Изобретение относится к вычислительной технике, а именно к цифровым вычислительным устройствам для оп- ределения обратной величины числа, и может быть использовано в составе арифметико-логических устройств ЦВМ, а также в виде самостоятельного вычислительного устройства.

Цель изобретения - расширение функциональных возможностей за счет обработки операндов с плавающей запятой.

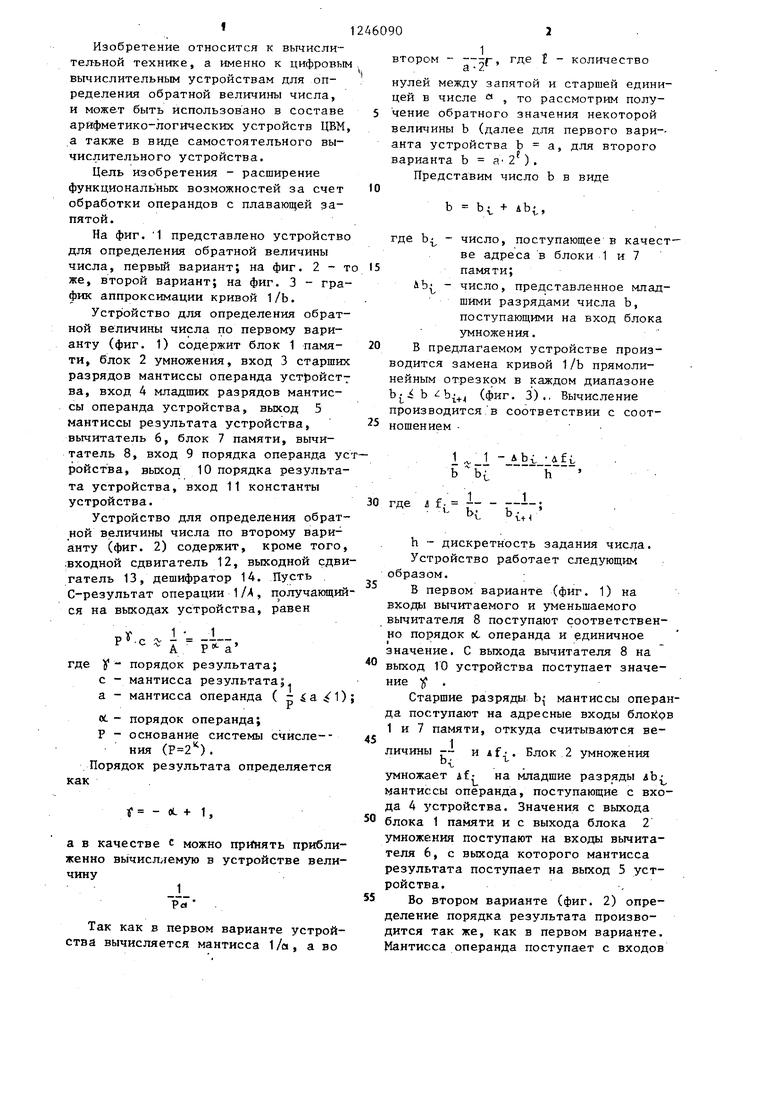

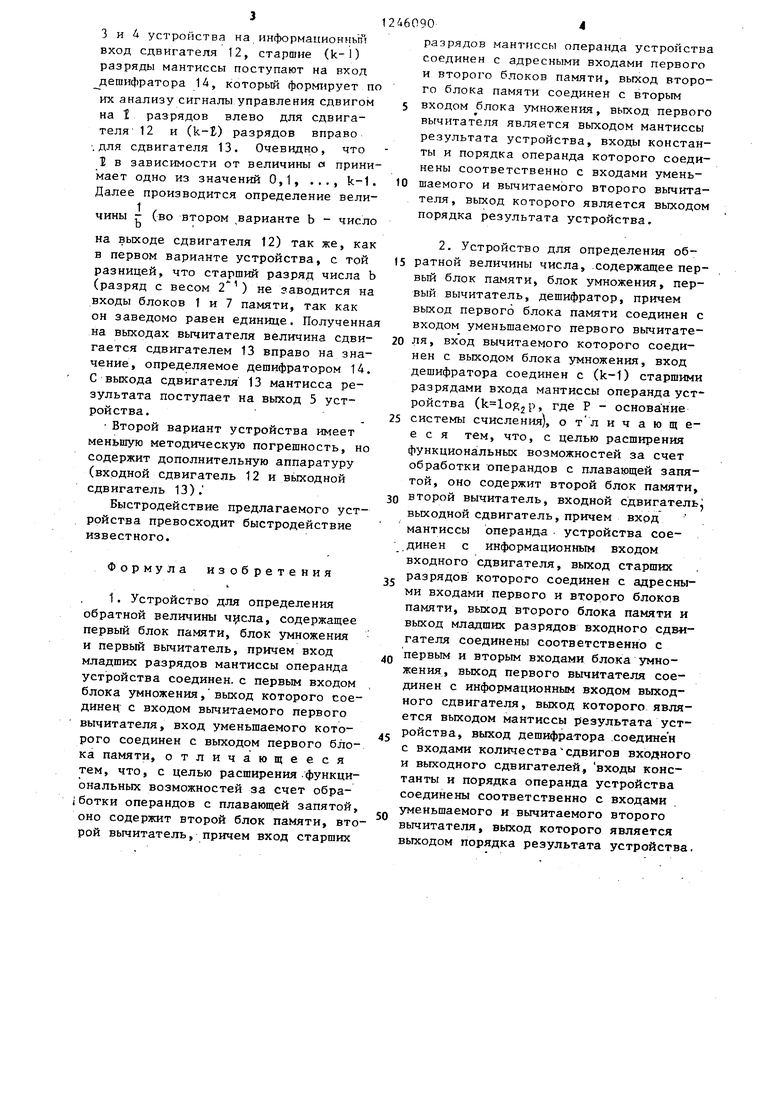

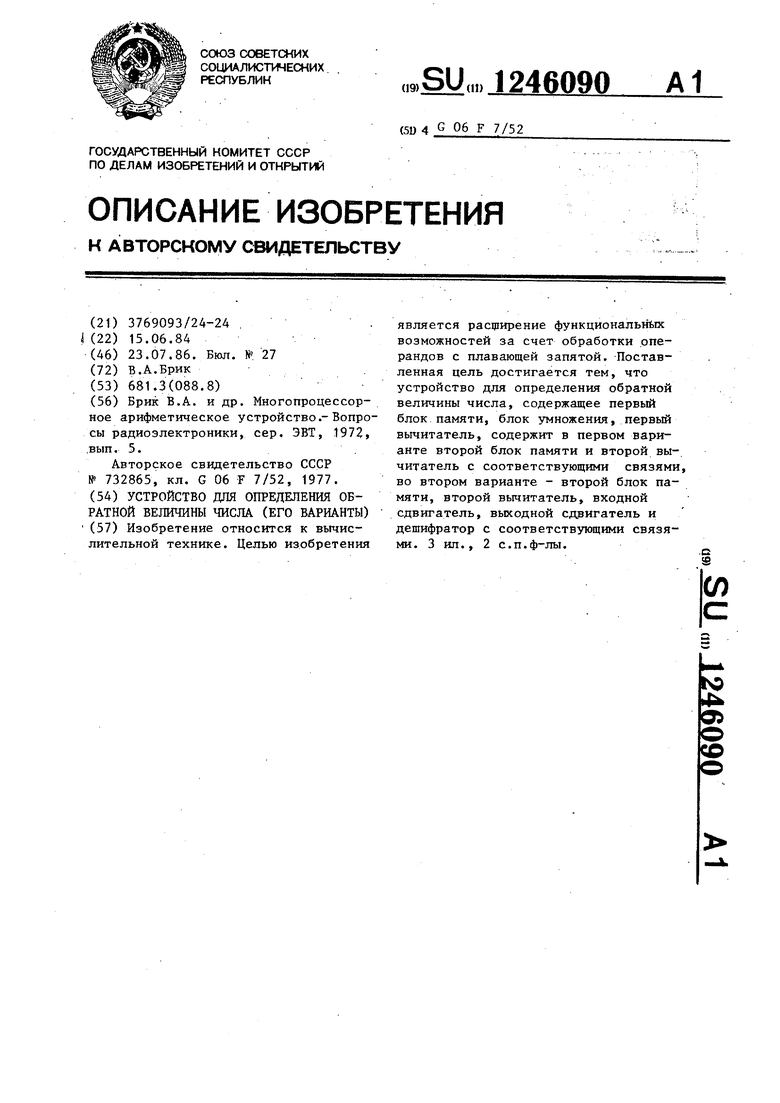

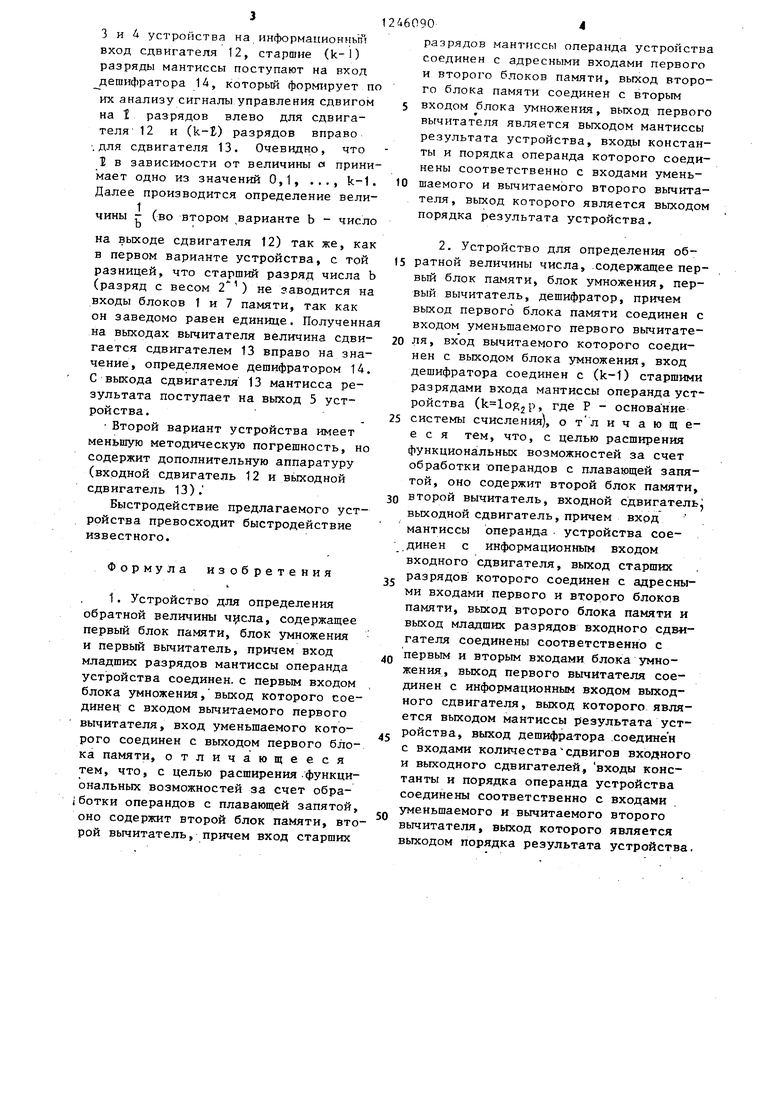

На фиг. 1 представлено устройство для определения обратной величины числа, первый вариант; на фиг. 2 - т же, второй вариант; на фиг. 3 - график аппроксимации кривой 1/Ь.

Устройство для определения обратной величины числа по первому варианту (фиг. 1) содержит блок 1 памяти, блок 2 умножения, вход 3 старших разрядов мантиссы операнда устройст7 ва, вход 4 младших разрядов мантиссы операнда устройства, выход 5 мантиссы результата устройства, вычитатель 6, блок 7 памяти, вычи- татель 8, вход 9 порядка операнда усройства, выход 10 порядка результата устройства, вход 11 константы устройства.

Устройство для определения обратной величины числа по второму варианту (фиг. 2) содержит, кроме того, .входной сдвигатель 12, выходной сдви гатель 13, дешифратор 14. Пусть С-результат операции 1 //, получающийся на выходах устройства, равен

где у- порядок результата; с - мантисса результата;

а - мантисса операнда ( - ia .1)

ос - порядок операнда;

Р - основание системы счисле-ния ().

Порядок результата определяется как

- ОС + 1,

а в качестве с можно принять приближенно вычисллемую в устройстве величину

1

Тс.

Так как в первом варианте устройства вычисляется мантисса 1 /а , а во

втором - --{-, где J - количество а -i.

нулей между запятой и старшей единицей в числе « , то рассмотрим полу- чение обратного значения некоторой величины b (далее для первого вари-- анта устройства b а, для второго варианта b а 2 ).

Представим число b в виде

b Ь + Ab|,,

где b

число, поступающее в качестве адреса в блоки 1 и 7 памяти;

4Ь| - число, представленное младшими разрядами числа Ь, поступающими на вход блока умножения.

в предлагаемом устройстве производится замена кривой 1/Ь прямолинейным отрезком в каждом диапазоне bj b (фиг. 3)., Вычисление производится в соответствии с соот

ношением

b %i

А b ъ

h

где л f/ f- - --1-; b{, b,

h - дискретность задания числа.

Устройство работает следующим образом. ;

В первом варианте (фиг. 1) на входы вычитаемого и уменьшаемого вычитателя 8 поступают соответственно порядок DC операнда и единичное I - значение, С выхода вычитателя 8 на выход 10 устройства поступает значение .

Старшие разряды Ь{ мантиссы операнда поступают на адресные входы

1 и 7 памяти, откуда считываются ве- I

личины -- и Af-. Блок 2 умножения

i. Л . умножает Af- на младшие разряды лЬ

мантиссы операнда, поступающие с входа 4 устройства. Значения с выхода

блока 1 памяти и с выхода блока 2 умножения поступают на входы вычитателя 6, с выхода которого мантисса результата поступает на выход 5 устройства.,

Во втором варианте (фиг. 2) определение порядка результата производится так же, как в первом варианте. Мантисса операнда поступает с входов

31246090

3 и 4 устройства на инфopмaциoн b п вход сдвигателя 12, старшие (k-1) разряды мантиссы поступают на вход

дешифратора 14, который формирует по их анализу сигналы управления сдвигом на t разрядов влево для сдвигателя 12 и (k-t) разрядов вправо

для сдвигателя 13. Очевидно, что Б в зависимости от величины ct приниает одно из значений 0,1, ..., k-1. алее производится определение велирасо и го 5 вх вь ре ты не ша те по

10

1 ,.

чины г (во втором варианте Ь - число

Ь

на выходе сдвигателя 12) так же, как в первом варианте устройства, с той разницей, что старший разряд числа b (разряд с весом 2) не заводится на входы блоков 1 и 7 памяти, так как он заведомо равен единице. Полученная на выходах вьгчитателя величина сдвигается сдБигателем 13 вправо на значение, определяемое дешифратором 14. С выхода сдвигателя 13 мантисса результата поступает на выход 5 устройства.

Второй вариант устройства имеет меньшую методическую погрешность, но содержит дополнительную аппаратуру (входной сдвигатель 12 и вьпсодной сдвигатель 13).

Быстродействие предлагаемого устройства превосходит быстродействие известного.

Формула изобретения

1. Устройство для определения обратной величины , содержащее первый блок памяти, блок умножения и первый вычитатель, причем вход младших разрядов мантиссы операнда устройства соединен, с первым входом блока умножения, выход которого соединен с входом вычитаемого первого

вычитателя, вход уменьшаемого которого соединен с выходом первого блока памяти, отличающееся тем, что, с целью расширения функциональных возможностей за счет обработки операндов с плавающей запятой, оно содержит второй блок памяти, второй вычитатель, причем вход старших

разрядов мантиссы операнда устройства соединен с адресными входами первого и второго блоков памяти, выход второго блока памяти соединен с вторьгм входом блока умножения, выход первого вьгчитателя является выходом мантиссы результата устройства, входы константы и порядка операнда которого соединены соответственно с входами уменьшаемого и вычитаемого второго вьгчитателя, выход которого является выходом порядка результата устройства.

2. Устройство для определения обратной величины числа, .содержащее первый блок памяти, блок умножения, первый вычитатель, дешифратор, причем выход первого блока памяти соединен с входом уменьшаемого первого вычитателя, вход вычитаемого которого соединен с выходом блока умножения, вход дешифратора соединен с (k-1) старшими разрядами входа мантиссы операнда устройства (k log2p, где Р - основа ние

системы счисления), о т л и ч а ю щ е- е с я тем, что, с целью расширения функциональньк возможностей за счет обработки операндов с плавающей запятой, оно содержит второй блок памяти,

второй вычитатель, входной сдвигатель выходной сдвигатель, причем вход мантиссы операнда устройства соединен с информационным входом входного сдвигателя, выход старших разрядов которого соединен с адресными входами первого и второго блоков памяти, выход второго блока памяти и выход младших разрядов входного сдвигателя соединены соответственно с первым и вторым входами блока умножения, выход первого вычитателя соединен с информационным входом выходного сдвигателя, выход которого является выходом мантиссы результата устройства, выход дешифратора соединен с входами количества сдвигов входного и выходного сдвигателей, входы константы и порядка операнда устройства соединены соответственно с входами уменьшаемого и вычитаемого второго вычитателя, выход которого является выходом порядка результата устройства.

II 9

Л 9

3

W

L

Д

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1984 |

|

SU1273921A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для вычисления косинуса числа | 1988 |

|

SU1522197A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ СОВМЕСТНО ХРАНИМЫХ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497179C1 |

| Арифметическое устройство | 1978 |

|

SU809169A1 |

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1290300A1 |

Изобретение относится к вычислительной технике. Целью изобретения является расширение функциональных возможностей за счет обработки операндов с плавающей запятой. Поставленная цель достигается тем, что устройство для определения обратной величины числа, содержащее первый блок памяти, блок умножения, первый вычитатель, содержит в первом варианте второй блок памяти и второй вы-, читатель с соответствующими связями, во втором варианте - второй блок памяти, второй вычитатель, входной сдвигатель, выходной сдвигатель и дешифратор с соответствующими связями. 3 ил., 2 с.п.ф-лы.

юу 6

Фиг Т

Фиг.З

Составитель В. Клюев Редактор Н. Тупица Техред Н.Бонкало Корректор Л. Пилипенко

Заказ 4002/42

Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5 .

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

VIO

Фиг. 2

Подписное

| Брик В.А | |||

| и др | |||

| Многопроцессорное арифметическое устройство.-Вопросы радиоэлектроники, сер | |||

| ЭВТ, 1972, .вып | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для деления | 1977 |

|

SU732865A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-23—Публикация

1984-06-15—Подача