1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, работанвдим в составе микропроцессорной системы.

Цель изобретения - расширение области применения устройства за счет увеличения числа хранимых в устройстве сервисных программ.

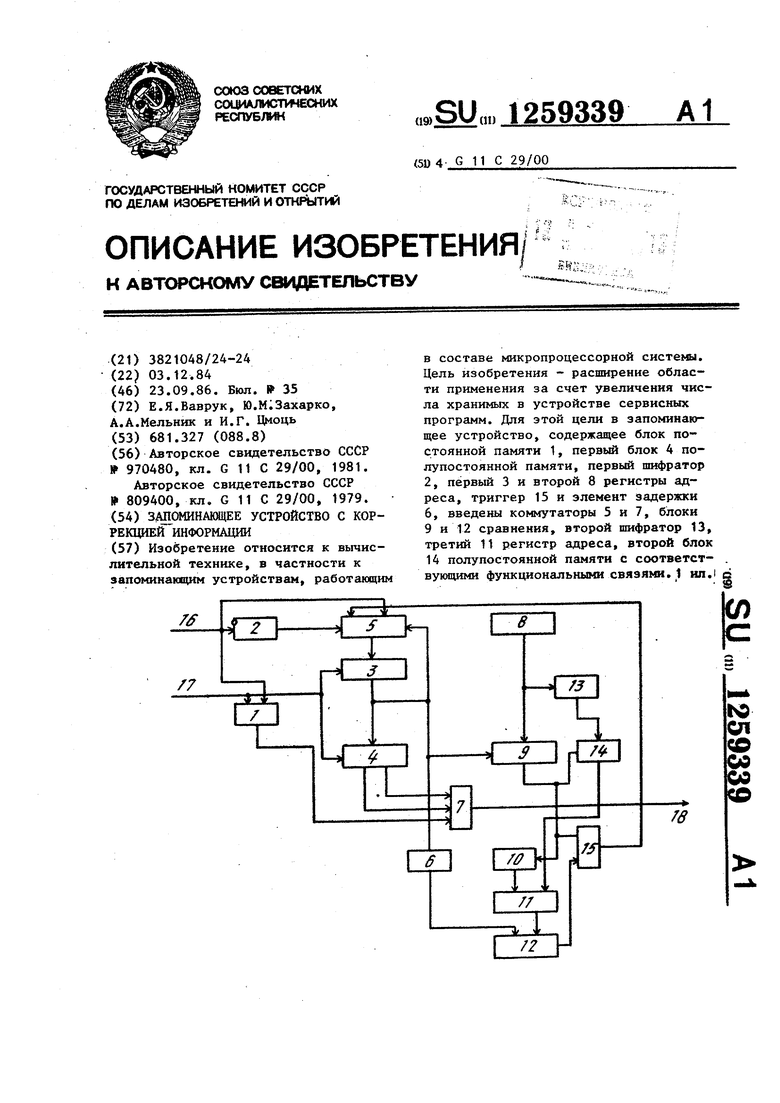

На чертеже приведена структурная схема предлагаемого устройства.

Запоминающее устройство с коррекцией информации содержит блок 1 постоянной памяти, первьш шифратор 2, первый регистр 3 адреса, первый блок 4 полупостоянной памяти, первый коммутатор 5, первый элемент 6 задержки второй коммутатор 7, второй 8 адреса, первый блок 9 сравнения, второй элемент 10 задержки, третий регистр 11 адреса, второй блок 12 сравнения, второй шифратор 13, второй блок 14 полупостоянной памяти и триггер 15. На чертеже обозначены также информационный 16 и управляющий 17 входы и выход 18 устройства. Разрядность блока 4 на единицу больше разрядности блока 1.

Устройство работает следующим образом.

Предварительно в шифратор 2 записывается таблица преобразования адресов блока 1, в которых имеются неисправности, и адресов начала про- гpaм, которые необходимо заменить на сервисные, в адреса блока 4. Объем блока 4 значительно меньше, чем объем блока 1 постоянной памяти. В блок 4 записывается исправленная информация и сервисные программы, Во второй шифратор 13 записьшается таблица преобразования начальных адресов сервисных программ в адреса блока 14. В блок 14 записываются конечные адреса сервисных программ. Триггер 15 и регистр 11 устанавливаются в нулевое состояние (цепи предварительной записи и установки не показаны).

По входу 16 устройства поступает код адреса, который после шифрации на шифраторе 2 через коммутатор 5 поступает на входы регистра 3 и непосредственно на адресные входы блока 1. Одновременно по входу 17 поступают сигнал считывания блока 1 и блока 4 и сигнал записи адреса на регистр 3. При наличии ошибки по некоторому адресу в блоке 1 выбирается

93392

соответствующий адрес блока 4, по которому записана правильная .информация. О наличии скорректированной информации свидетельствует единич5 HbL4 сигнал на выходе старшего информационного разряда блока 4, который открывает коммутатор 7, т.е. на выход блока 18 поступает информация с блока 4 о

0 Если по адресам блока 1 записана правильная информация, на выходе шифратора 2 формируется код фиксированного адреса по котородчу записана нулевая информация в старшем разря 5 де, т.е. на выход 18 поступает информация с блока 1.

При необходимости работы с сервисными программами или замены одной программы другой, начальный адрес

20 программы записывается в регистр 8 (в коде адреса блока 4). При поступлении адреса начала программы на вход блока 4 поисходит аналогично описанному случаю считывание информации из

25 этого блока. Одновременно данный адрес поступает на входы блока 9 сравнение, в котором происходит сравнение текущего адреса с адресом,установлен- ныт-1 на регистре 8.Сигнал сравнения

30 устанавливае г в единичное состояние триггер 15, который разрё шает работу коммутатора 5.

На шифраторе 13 происходит преобразование адреса начала программы в

35 адрес блока 14. Сигнал сравнения с выхода блока 9 сравнения разрешает выборку конечного адреса программы, записанного в блоке 14, и запись его в регистр 11 (по сигналу сравне40 ния из блока 9 сравнения, задержанному на элементе 10 задержки).

При последовательной обработке программь, записанной в блоке 4,, по входу 17 поступает сигнал +1 на

5 регистр 3.

При ветвлении этой программы признаки ветвления (например, признаки переполнения, переноса, перехода по знаку) поступают по входу 16

50 на одни из входов коммутатора 5,, на другие входы которых поступает код текущего адреса.

Последняя команда программы сервисной обработки - команда перехода

55 ка основную программу. Адрес этой команды с задержкой на элементе 6 задержки поступает на блок 12 сравнения, где сравнивается с адресом.

записанным в регистре 1 1. CHPHajE сравнения устанавливает в нулевое положение триггер 15, нулевой выход которого разрешает работу коммутатора 5.

С помощью регистра 3 и коммутатора 5 возможно реализовать ветвление программы в блоке 4.

Формула изобретения

Запоминающее устройство с коррек- циейГ информации, содержащее блок постоянной памяти, первый блок полупостоянной памяти, первый шифратор, первый и второй регистры адреса, триггер и элементы задержки, отличающееся тем, что, с целью расширения области применения за счет увеличения числа хранимых в устройстве сервисных программ, в него введены коммутаторы, блоки сравнения, второй шифратор, третий регистр адреса и второй блок полупостоянной памяти, причем выход пер- Бого коммутатора подключен к инфор- мационпому входу первого регистра адреса, выход которого соединен непосредственно с адресным входом первого блока полупостоянной памяти и первым входом первого блока сравнения и через первьш элемент задержки с первым входом второго блока сравнения, второй вход которого прдклюСоставитель В.Рудаков Редактор А.Ворович Техред М.Ходанич Корректор М.Максимишинец

Заказ 5128/50 Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

394

чен к выходу третьего регистра адреса, а выход - к одному из входов триггера, выход которого соединен с управляющим входом первого коммутатора, выход второго регистра адреса соединен с входом второго шифратора и вторым входом первого блока сравнения, выход которого подключен непосредственно к управлякицему входу второго блока полупостоянной памяти и другому входу триггера и через второй элемент задержки - к управляющему входу третьего регистра адреса, информационный вход которого соединен с выходом второго блока полупостоянной памяти, вход которого подключен к выходу второго шифратора, один из информационных входов первого коммутатора, вход первого шифратора и адресный вход первого блока памяти являются информационным входом устройства, другие информационные входы первого коммутатора подключены соответственно к выходам первого шифратора и первого регистра адреса, выходы первого.блока полупостоянной памяти и блока постоянной памяти соединены с входами второго коммутатора, выход которого является выходом устройства, управляющим входом которого являются управляющие входы блока постоянной памяти, первого регистра адреса и первого блока полупостоянной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1985 |

|

SU1273939A1 |

| Процессор | 1985 |

|

SU1280378A1 |

| Запоминающее устройство с коррекцией программы | 1986 |

|

SU1347097A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

| Устройство для коррекции программ | 1982 |

|

SU1092514A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Программируемый контроллер | 1990 |

|

SU1714599A1 |

Изобретение относится к вычислительной технике, в частности к запоминанщим устройствам, работанщим в составе микропроцессорной системы. Цель изобретения - расширение области применения за счет увеличения числа хранимых в устройстве сервисных программ. Для этой цели в запоминающее устройство, содержащее блок постоянной памяти 1, первый блок 4 полупостоянной памяти, первый шифратор 2, первый 3 и второй 8 регистры адреса, триггер 15 и элемент задержки 6, введены коммутаторы 5 и 7, блоки 9 и 12 сравнения, второй шифратор 13, третий 11 регистр адреса, второй блок 14 полупостоянной памяти с соответствующими функциональными связями. 1 ип.1 ел ю СП 09 00 D

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970480A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-09-23—Публикация

1984-12-03—Подача