СЛ

10

15

20

25

30

Изобретение относится к вычислительной технике и может быть использовано для построения устройств контроля блоков буферной памяти систем обработки информации.

Цель изобретения - повьшение достоверности контроля.

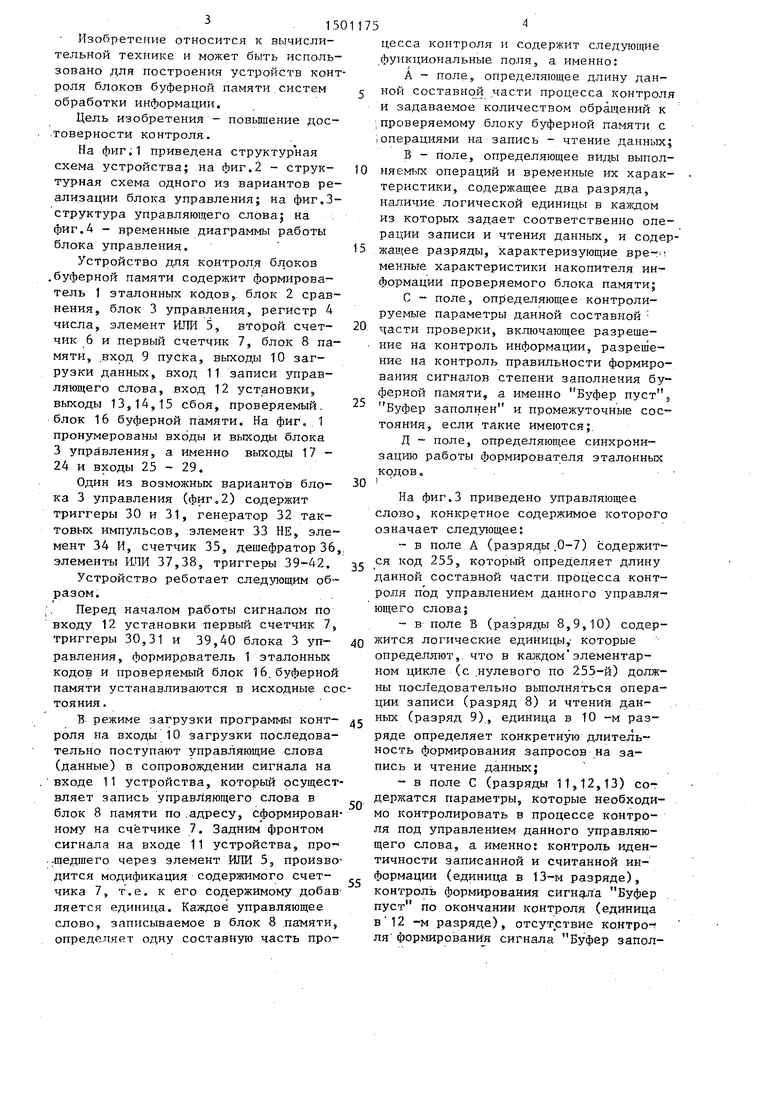

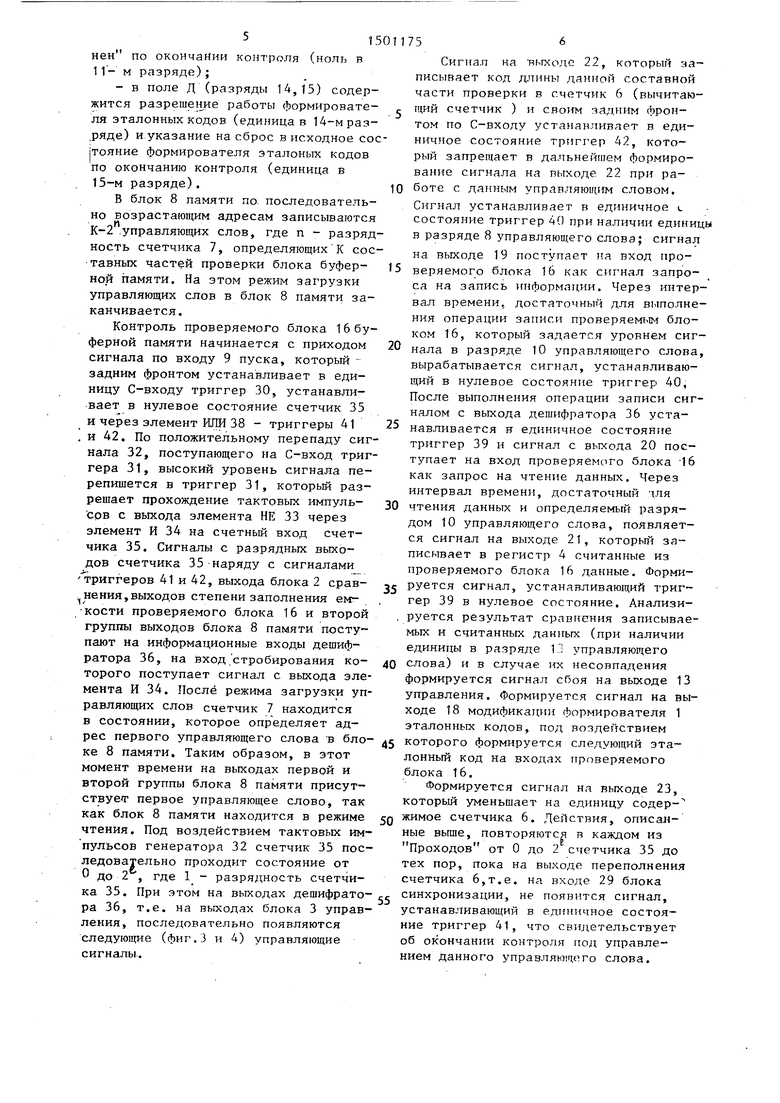

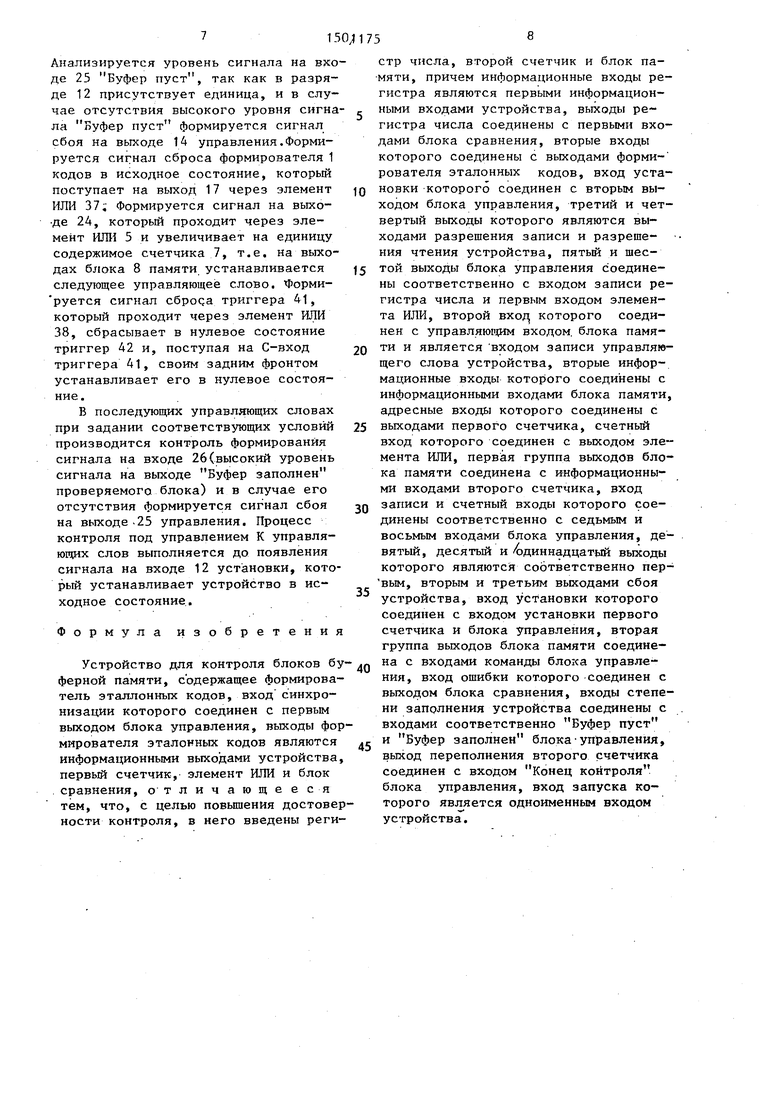

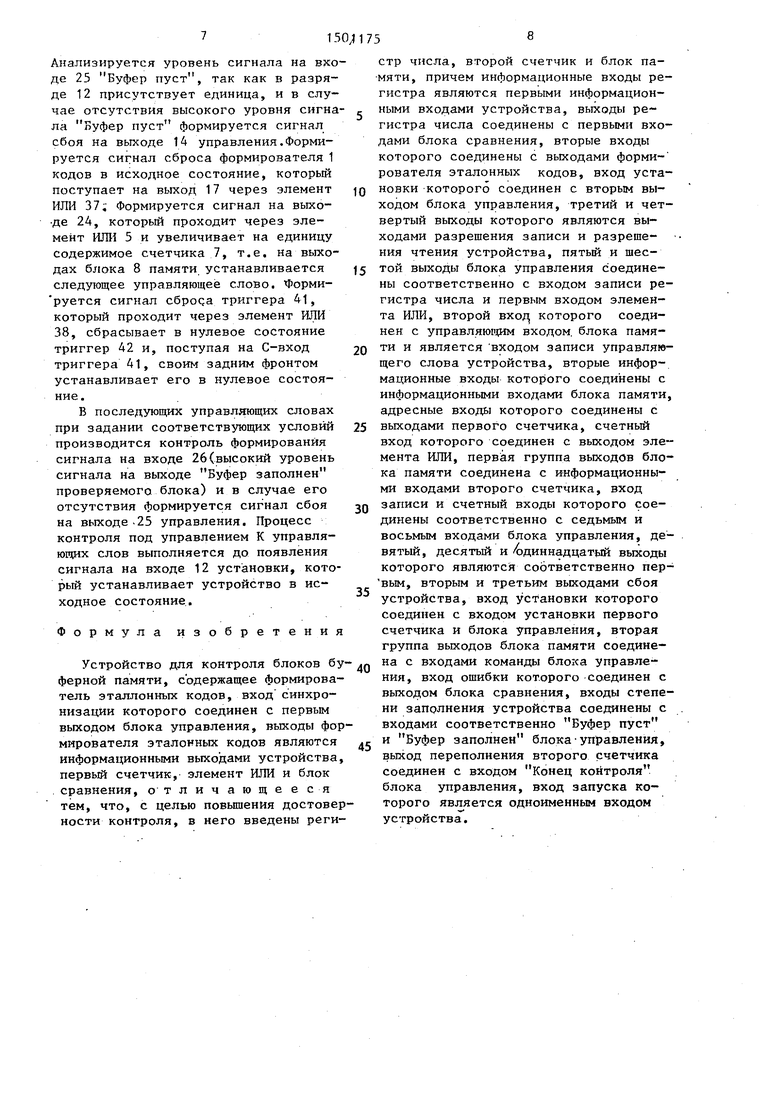

На фиг;1 приведена структурная схема устройства; на фиг.2 - структурная схема одного из вариантов реализации блока управления; на фиг.З- структура управляющего словаj на фиг.4 - временные диаграммы работы блока управления.

Устройство для контроля блоков буферной памяти содержит формирователь 1 эталонных кодов, блок 2 срав нения, блок 3 управления, регистр 4 числа, элемент ИЛИ 5, второй счетчик 6 и первый счетчик 7, блок 8 памяти, вход 9 пуска, выходы 10 загрузки данных, вход 11 записи управляющего слова, вход 12 установки, выходы 13,14,15 сбоя, проверяемый. блок 16 буферной памяти. На фиг. 1 пронумерованы входы и выходы блока 3 управления, а именно выходы 17 - 24 и входы 25-29.

Один из возможных вариантов блока 3 управления (фиг,2) содержит триггеры 30 и 31, генератор 32 тактовых импульсов, элемент 33 НЕ, элемент 34 И, счетчик 35, дешефратор 36,, элементы Ш1И 37,38, триггеры 39-42.

Устройство реботает следующим образом.

Перед началом работы сигналом по входу 12 установки -первый счетчик 7, триггеры 30,31 и 39,40 блока 3 управления, формирователь 1 эталонных кодов и проверяемый блок 16.буферной памяти устанавливаются в исходные состояния .

В режиме загрузки программы конт- д5 роля на входы 10 загрузки последовательно поступают управляющие слова (данные) в сопровождении сигнала на входе 11 устройства, который осуществляет запись управляющего слова в блок 8 памяти по .адресу, сформированному на счётчике 7. Задним фронтом сигнала на входе 11 устройства, про .-щедшего через элемент ИЛИ 3, производится модификация содержимого счет- чика 7, т .е. к его содержимому добавляется единица. Каждое управляющее слово, записываемое в блок 8 памяти, определяет одну составную часть про40

,г

цесса контроля и содержит следующие функциональные по.пя, а именно:

А - поле, определяющее длину данной составной частк процесса контроля и задаваемое количеством обращений к :проверяемому блоку буферной памяти с ; операциями на запись - чтение данных;

В - поле, определяющее виды выпол- няемт гх операций и временные их характеристики, содержащее два разряда, наличие логической единицы в каждом из которых задает соответственно операции записи и чтения данных, и содержащее разряды, характеризующие вре-- . менные характеристики накопителя информации проверяемого блока памяти;

С - поле, определяющее контролируемые параметры данной составной части проверки, включающее разреще- ние на контроль информации, разрешение на контроль правильности формирования сигналов степени заполнения буферной памяти, а именно Буфер пуст Буфер заполнен и промежуточные сос- тоян-ия, если такие имеются;.

Д - поле, определяющее синхронизацию работы формирователя эталонных кодов.5

0

На фиг.З приведено управляющее слово, конкретное содержимое которого означает след-ующее:

-в поле А (разряды .0-7) содержит- г ся код 255, который определяет длину

данной составной части процесса контроля под управлением данного управляющего слова;

-в поле В (разряды 8,9,10) содержится логические единицы,- которые определяют,, что в каждом элементарном цикле (с .нулевого по 255-й) должны посл едовательно выполняться операции записи (разряд 8) и чтения данных (разряд 9)., единица в 10 -м разряде определяет конкретную длитель- ность формирования запросов на запись и чтение данных;

-в поле С (разряды 11,12,13) содержатся параметры, которые необходимо контролировать в процессе контроля под управлением данного управляющего слова, а именно: контроль идентичности записанной и считанной информации (единица в 13-м разряде), контроль формирования сигнала Буфер пуст по окончании контроля (единица в 12 -м разряде), отсутствие ко.нтро- ля формирования сигнала Буфер запол5150

нен по окончании контроля (ноль в 11- м разряде);

- в поле Д (разряды 14,15) содержится разрешение работы формирователя эталонных кодов (единица в 14-мраз- .ряде) и указание на сброс в исходное сос- |тояние формирователя эталоных кодов по окончанию контроля (единица в 15-м разряде).

В блок 8 памяти по последовательно возрастающим адресам записываются К-2 .управляющих слов, где п - разрядность счетчика 7, определяющих К сос15

20

25

30

тавных частей проверки блока буферной памяти. На этом режим загрузки управляющих слов в блок 8 памяти заканчивается.

Контроль проверяемого блока 16 буферной памяти начинается с приходом сигнала по входу 9 пуска, которьй - задним фронтом устанавливает в единицу С-входу триггер 30, устанавливает в нулевое состояние счетчик 35 и через элемент ИЛИ 38 - триггеры 41 и 42, По положительному перепаду сигнала 32, поступающего на С-вход триггера 31, высокий уровень сигнала перепишется в триггер 31, который разрешает прохождение тактовых импуль- срв с выхода элемента НЕ 33 через элемент И 34 на счетный вход счетчика 35. Сигналы с разрядных выходов счетчика 35 наряду с сигналами триггеров 41 и 42, выхода блока 2 срав- нения,выходов степени заполнения ем- кости проверяемого блока 16 и второй группы выходов блока 8 памяти посту™ пают на информационные входы дешифратора 36, на вход стробирования которого поступает сигнал с выхода элемента И 34. После режима загрузки управляющих слов счетчик 7 находится в состоянии, которое определяет адрес первого управляющего слова в бло- АС ке 8 памяти. Таким образом, в этот момент времени на выходах первой и второй группы блока 8 памяти присутствует первое управляющее слово, так как блок 8 памяти находится в режиме чтения. Под воздействием тактовых импульсов генератора 32 счетчик 35 последовательно проходит состояние от

35

40

50

О

до 2 , где 1 - разрядность счетчика 35. При этом на выходах дешифрато- ра 36, т.е. на выходах блока 3 управления, последовательно появляются следующие (фиг.З и 4) управляющие сигналы.

0

5

0

5

0

С

5

0

0

е

756

Сигнал на TibrxoAe 22, который записывает код длины данной составной части проверки в счетчик 6 (вычитающий счетчик ) и своим задним фронтом по С-входу устанавливает в единичное состояние триггер 42, который запрещает в дальнейшем формирование сигнала на выходе 22 при работе с да11ным управляюи1им словом, Сигнал устанавливает в единичное (. состояние триггер 40 при наличии единицы в разряде 8 управляющего слова; сигнал на выходе 19 поступает на вход проверяемого блока 16 как сигнал запроса на запись информации. Через интервал времени,, достаточный для выполнения операции записи проверяемым блоком 16, который задается уровнем сигнала в разряде 10 управляющего слова, вырабатывается сигнал, устанавливающий в нулевое состояние триггер 40, После выполнения операции записи сигналом с выхода дешифратора 36 устанавливается в единичное состояние триггер 39 и сигнал с выхода 20 поступает на вход проверяемого блока 16 как запрос на чтение данных. Через интервал времени, достаточный лля чтения данных и определяемый разрядом 10 управляющего слова, появляется сигнал на выходе 21, которьй зя- писывает в регистр 4 считанные из проверяемого блока 16 данные. Формируется сигнал, устанавливающий триггер 39 в нулевое состояние. Анализируется результат сравнения записываемых и считанных данных (при наличии единицы в разряде 13 управляющего слова) и в случае их несовпадения формируется сигнал сбоя на выходе 13 управления. Формируется сигнал на выходе 18 модификации формирователя 1 эталонных кодов, под воздействием которого формируется следующий эталонный код на входах гтроверяемого блока 16.

Формируется сигнал на выходе 23, который уменьшает на единицу содер- жимое счетчика 6. Действия, описал- ные вьш1е, повторяются в каждом из Проходов от О до 2 счетчика 35 до тех пор, пока на выходе переполнения счетчика 6,т.е. на входе 29 блока синхронизации, не появится сигнал, устанавливающий в единичное состояние триггер 41, что свидетельствует об окончании контроля под управлением данного управляю цого слова.

Анализируется уровень сигнала на входе 25 Буфер пуст, так как в разряде 12 присутствует единица, и в случае отсутствия высокого уровня сигнала Буфер пуст формируется сигнал сбоя на выходе 14 управления.Формируется сигнал сброса формирователя 1 кодов в исходное состояние, который поступает на выход 17 через элемент ИЛИ 37; Формируется сигнал на выходе 24, который проходит через элемент ИЛИ 5 и увеличивает на единицу содержимое счетчика 7, т.е. на выходах блока 8 памяти устанавливается следующее управляющее слово. Форми- руется сигнал сброда триггера 41, который проходит через элемент ИЛИ 38, сбрасывает в нулевое состояние триггер 42 и, поступая на С-вход триггера 41, своим задним фронтом устанавливает его в нулевое состояние.

В последующих управляющих словах при задании соответствующих условий производится контроль формирования сигнала на входе 26(высокий уровень сигнала на выходе Буфер заполнен проверяемого блока) и в случае его отсутствия формируется сигнал сбоя на выходе.25 управления. Процесс контроля под управлением К управляющих слов выполняется до появления сигнала на входе 12 установки, который устанавливает устройство в исходное состояние.

Формула изобретения

Устройство для контроля блоков буферной памяти, содержащее формирователь эталлонных кодов, вход синхронизации которого соединен с первым выходом блока управления, выходы формирователя эталонных кодов являются информационными выходами устройства первый счетчик, элемент ИЛИ и блок сравнения, отличающееся тем, что, с целью повышения достоверности контроля, в него введены регистр числа, второй счетчик и блок па- мяти, причем информационные входы регистра являются первыми информационными входами устройства, выходы регистра числа соединены с первыми входами блока сравнения, вторые входы которого соединены с выходами форми- рователя эталонных кодов, вход установки которого соединен с вторьм выходом блока управления, третий и четвертый выходы которого являются выходами разрешения записи и разрешения чтения устройства, пятый и шестой выходы блока управления соединены соответственно с входом записи регистра числа и первым входом элемента ИЛИ, второй вхо которого соединен с управляю1чим входом, блока памяти и является входом записи управляющего слова устройства, вторые информационные входы которого соединены с информационными входами блока памяти, адресные входы которого соединены с

выходами первого счетчика, счетный вход которого соединен с выходом элемента ИЛИ, перв&я группа выходов блока памяти соединена с информационными входами второго счетчика, вход

записи и счетный входы которого соединены соответственно с седьмым и восьмым входами блока управления, девятый, десятый и Одиннадцатый выходы которого являютсй соответственно пер- вым, вторым и третьим выходами сбоя устройства, вход установки которого соединен с входом установки первого счетчика и блока управления, вторая группа выходов блока памяти соединена с входами команды блока управления, вход ошибки которого соединен с выходом блока сравнения, входы степени заполнения устройства соеда1нены с входами соответственно Буфер пуст и Буфер заполнен блокауправления, выход переполнения второго счетчика соединен с входом Конец контроля блока управления, вход запуска которого является одноименным входом устройства.

isа

и аа 1)14 fJttijfiaaff

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249583A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1236550A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Устройство для сопряжения | 1985 |

|

SU1278861A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения устройств контроля блоков буферной памяти систем обработки информации. Целью изобретения является - повышение достоверности контроля. Устройство для контроля блоков буферной памяти содержит формирователь эталонных кодов 1, блок сравнения 2, блок управления 3, элемент ИЛИ 5, первый счетчик 7, регистр числа 4, второй счетчик 6 и блок памяти 8. Устройство обеспечивает контроль аппаратных средств слежения за степенью заполнения информационной емкости буферной памяти. 4 ил.

Paspsffb/ 0123

55189 10 11 11 1$ 14 15

Ф1Я.1

tt а

| Авторское свидетельство СССР 754483, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков буферной памяти | 1984 |

|

SU1293761A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-08-15—Публикация

1987-03-14—Подача