1

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ и цифровых устройствах автоматики.

Цель изобретения - упрощение сумматора.

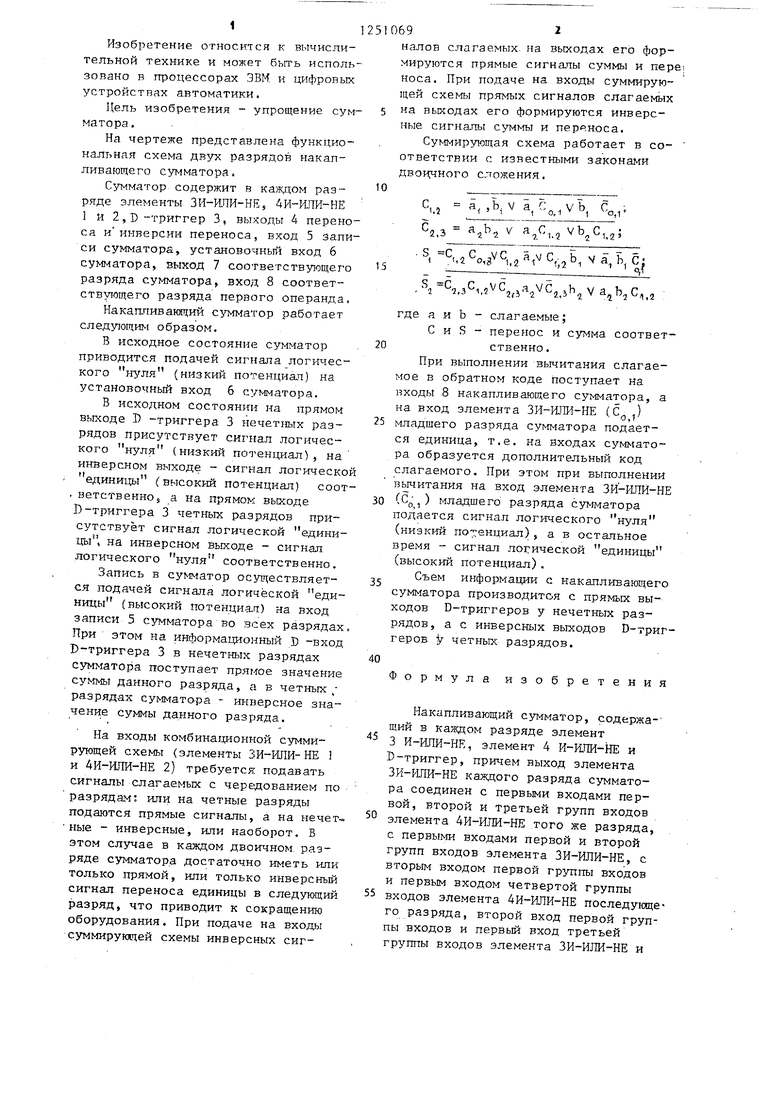

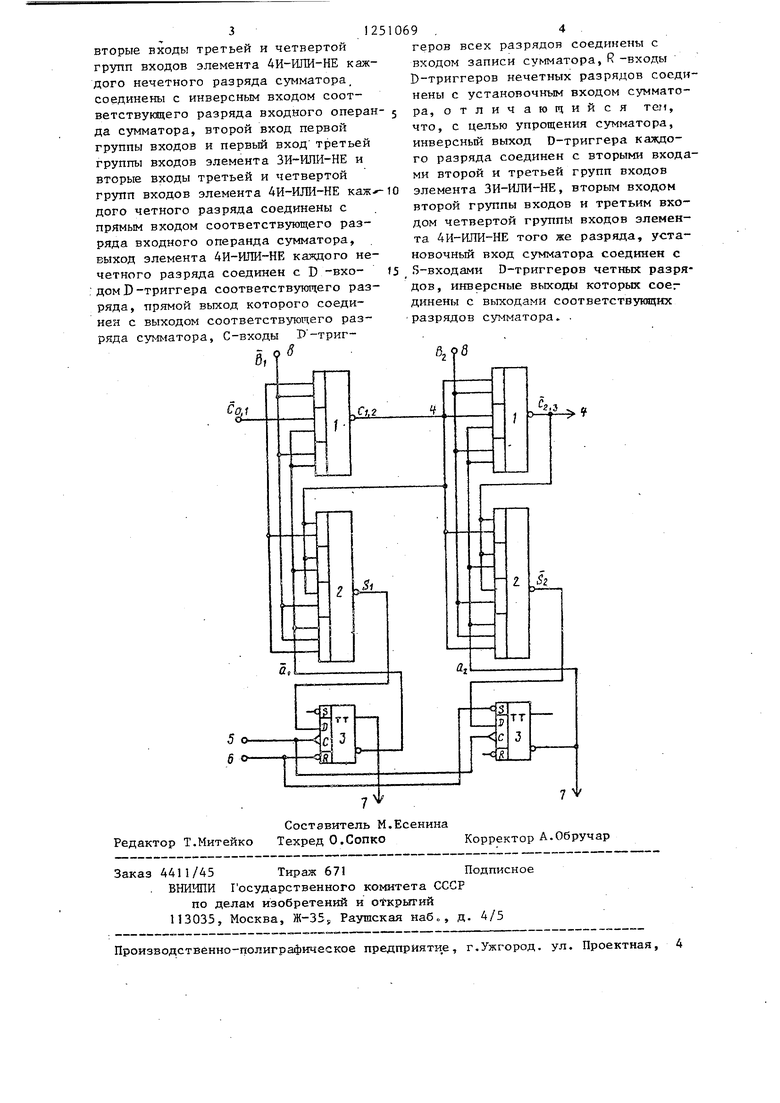

На чертеже представлена функциональная схема двух разрядов накапливающего сумматора.

Сумматор содержит в каждом разряде элементы ЗИ-КПИ-НЕ, 4И-ИЛИ-НЕ 1 и 2,D -триггер 3, выходы 4 переноса и инверсии переноса, вход 5 записи сумматора, установочньй вход 6 сумматора, выход 7 соответствующего разряда сумматора, вход 8 соответствующего разряда первого операнда.

Накапливагадий сумматор работает следзлощим образом.

В исходное состояние сумматор приводится подачей сигнала логического нуля (низкий потендиап) на установочный вход б сумматора.

В исходном состоянии на прямом выходе D -триггера 3 нечетных разрядов присутствует сигнал логического нуля (низкий потенциал), на инверсном выходе - сигнал логическо единицы (высокий потенциал) соот . ветственно, а на прямом выходе J)-триггера 3 четньгх разрядов присутствует сигнал логической едини- ЦЬ1, на инверсном выходе - сигнал логического нуля соответственно.

Запись в сумматор осуществляется подачей сигнала логической единицы (высокий потенциа-я) на вход записи 5 сумматора во всех разрядах При этом на информационный D -вход D-триггера 3 в нечетных разрядах сумматора поступает прямое значение суммы данного разряда, а в четных;/ разрядах сумматора - инверсное значение суммы данного разряда.

На входы комбинационной суммирующей схемы (элементы ЗИ-ИЛИ-НЕ 1 и 4И-ИЛИ-НЕ 2) требуется подавать сигналы слагаемых с чередованием по разрядам: или на четные разряды подаются прямые сигналы, а на нечет ные - инверсные, или наоборот. В этом случае в каждом двоичном, разряде сумматора достаточно иметь или только прямой, или только инверсный сигнал переноса единицы в следующий разряд, что приводит к сокращению оборудования. При подаче на входы суммирующей схемы инверсных сиг51069

налов слагаемых, на выходах его формируются прямые сигнапы суммы и nepei носа. При подаче на входы суммирующей схемы прямых сигналов слагаемых 5 на выходах его формируются инверсные сигналы суммы и переноса.

Суммирующая схема работает в соответствии с известными законами двои;чного сложения.

i, ,b. V

V

nVb, С

о,Г

7.1. ,,;

15

S. 2 0, I Cbabi l .,3Ci,.VC ,,,,C,,,

где a и b - слагаемые;

С и S - перенос и сумма соответственно.

При выполнении вычитания слагаемое в обратном коде поступает на нходы 8 накапливающего сумматора, а на вход элемента ЗИ-РШИ-НЕ (С )

младщего разряда сумматора подается единица, т.е. на входах ра образуется дополнительный код слагаемого. При этом при выполнений вычитания на вход элемента ЗИ -ИЛИ-НЕ

-Сд, ) младшего разряда cy мaтopa подается сигнал логического нуля (низкий по7:енциал), а в остальное время - сигнал логической единицы (высокий потенциал).

Съем информации с накапливающего сумматора производится с прямых выходов D-триггеров у нечетных разрядов, а с инверсных выходов D-триггеров четных разрядов.

Формула изобретения

Накапливающий сумматор, содержа- щий в каждом разряде элемент

3 И-ИЛИ-НЕ, элемент 4 И-К1Ш-НЕ и Г-триггер, причем выход элемента ЗИ-ИЛИ-НЕ каждого разряда сумматора соединен с первыми входами первой, второй и третьей групп входов элемента 4И-ИЛИ-НЕ того же разряда, с первыми входами первой и второй групп входов элемента ЗИ-ИЛИ-НЕ, с вторым входом первой группы входов и первым входом четвертой группы

входов элемента 4И-ИЛИ-НЕ последующего разряда, второй вход первой группы входов и первый вход третьей группы входов элемента ЗИ-ИЛИ-НЕ и

вторые входы третьей и четвертой групп входов элемента 4И-ИЛИ-НЕ каждого нечетного разряда сумматора, соединены с инверсным входом соответствующе го разряда входного операн да сумматора, второй вход первой группы входов и первый вход третьей группы входов элемента ЗИ-ИЛИ-НЕ и вторые входы третьей и четвертой групп входов элемента 4И-ИЛИ-НЕ каждого четного разряда соединены с прямым входом соответствующего разряда входного операнда сумматора, выход элемента 4И-ИЛИ-НЕ каждого нечетного разряда соединен с D -входом D -триггера соответствующего разряда, прямой выход которого соединен с выходом соответствуютчего разряда сумматора, С-входы Р -трига,

10

- 5

51069 ,4

геров всех разрядов соединены с входом записи сумматора,R -входы D-триггеров нечетных разрядов соединены с установочным входом сумматора, отличающийся теп, что, с целью упрощения сумматора, инверсный выход D-триггера каждого разряда соединен с вторыми входами второй и третьей групп входов элемента ЗИ-ИЛИ НЕ, вторым входом второй группы входов и третьим входом четвертой группы входов элемента 4И-ИЛИ-НЕ того же разряда, установочный вход сумматора соединен с S-входами D-триггеров четных разрядов, инверсные выходы которых соег динены с выходами соответствуннцих разрядов сумматора. .

15

Составитель М.Есенина

Редактор Т.Митейко Техред 0.Сопке

Заказ 4411/45 Тираж 671Подписное

ВНИИПИ Г осударственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-ЗЗ, Раушская наб, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

Корректор А.Обручар

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для умножения | 1974 |

|

SU608156A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Цифровой функциональный преобразователь | 1987 |

|

SU1444758A1 |

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для определения максимальной гармоники спектра Уолша | 1984 |

|

SU1211751A1 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ и цифровых устройствах автоматики. Цель изобретения - упрощение сумматора. Накапливающий сумматор содержит в каждом разряде элемент ЗИ-ИЛИ-НЕ, элемент 4И-ИПИ-НЕ и D-триггер. В исходном состоянии на прямых выходах D-триггера нечетных разрядов присутствует сигнал логического нуля, на инверсных - сигнал логической единицы. Запись в сумматор осуществляется подачей логической единицы на . вход записи накапливающего сумматора. При этом на D-вход D-триггера в нечетньтх разрядах сумматора поступает прямое значение суммы данного разряда, в четных разрядах сумматора - инверсные значения суммы данного разряда. Съем информации с накапливающего сумматора производится с прямых выходов D-триггеров в нечетных разрядах и с инверсных выходов D-триггеров - в четных разрядах сумматора. 1 ил . % (Л

| Комбинационный двухразрядный сумматор | 1976 |

|

SU627478A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Тарабрин Б.В | |||

| и др | |||

| Справочник по интегральньтм микросхемам | |||

| М.: Энергия, 1981, с,741, рис.5-250. | |||

Авторы

Даты

1986-08-15—Публикация

1984-12-19—Подача