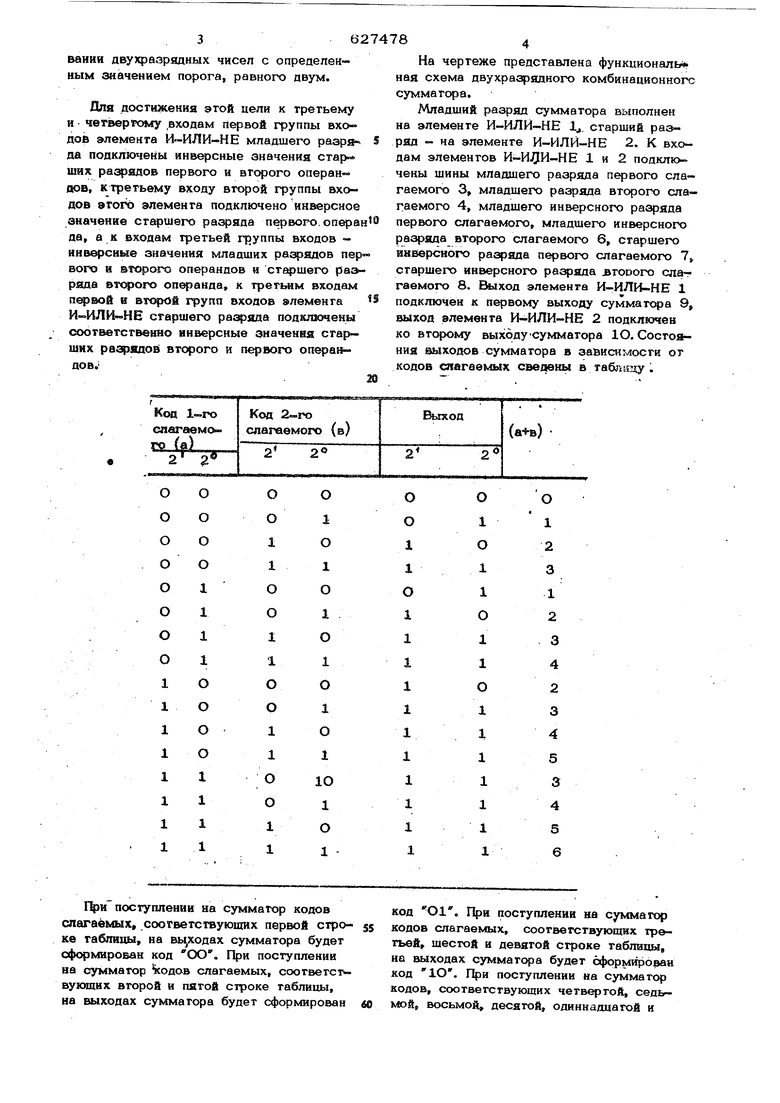

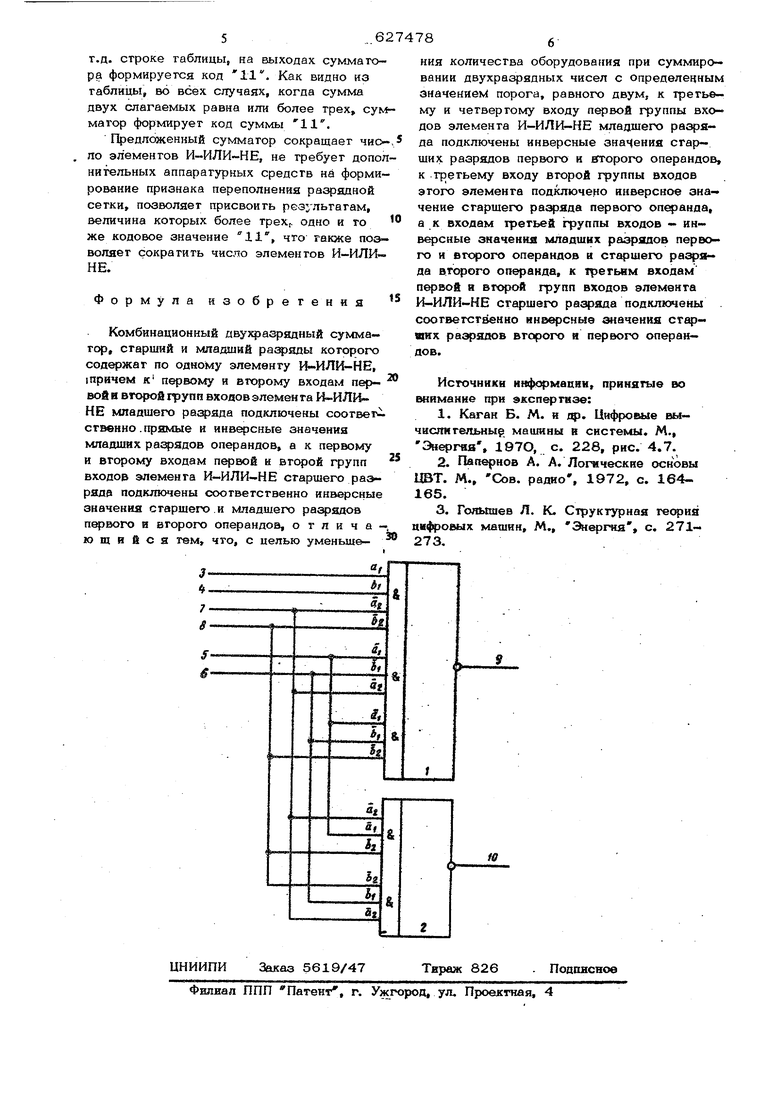

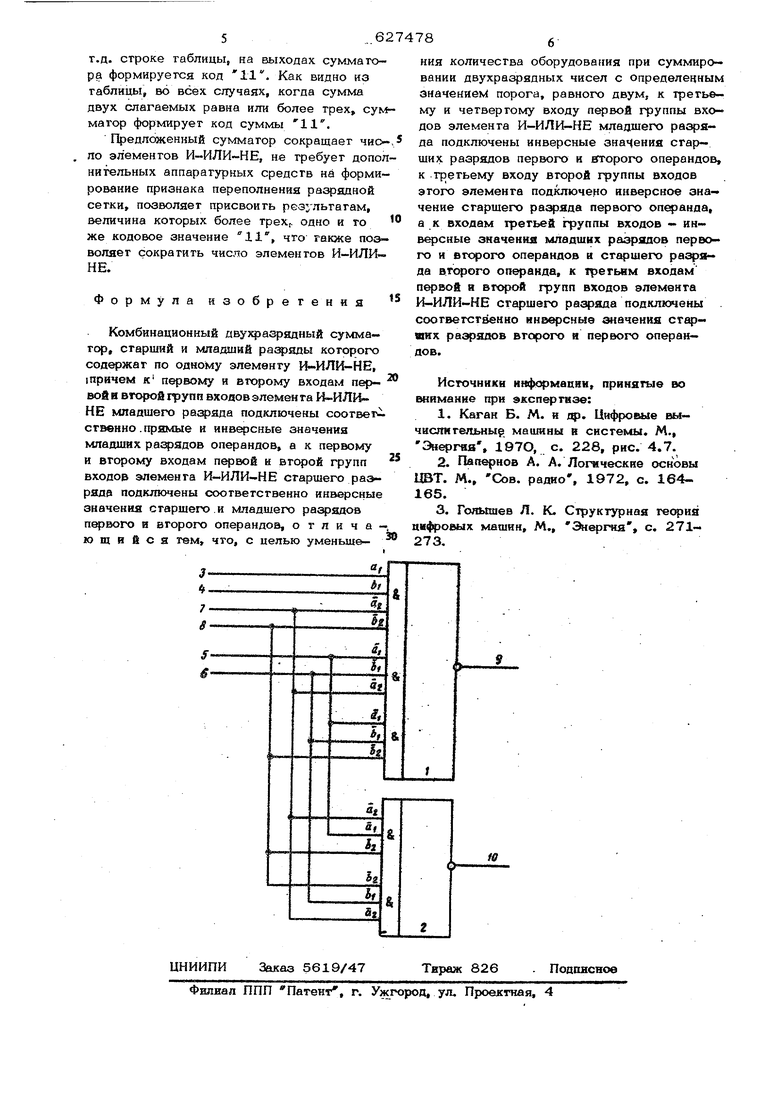

Изобретение огноситса к цифровой вь числигельной технике и может быгь испол зовано в специализированных вычислительных устройствах. Известны комбинационные, сумматоры собранные на элементах И-ИЛИ-НЕ, содер жащие пора ШЕ1ые узлы суммирования чи сел. Каждый -ый узел имеет выход j-г разряда кода суммы и цепь переноса в i +1 разряд, а входами каждого узла я лаются цепи i -ых реизрядов кодов слагае мых и веаь переноса от (t -1)-го узла сумматсч а . В этих сумматорах время формирования кода суммы зависит от числа разрадов в коде слагаемых. Известны быстродействующие сумматЧ ры с одновременным формированием переноса во всех разрядах сумматора 2 . Количество элементов И-ИЛИ-НЁ« по фс мнрованию переноса в таких сумматорах растет от младшего разряда к старшему. Но даже в сумматорах с одновременным формированием переноса содержится не менее трех ступеней элементов И-ИЛИ- НЕ, участвующих в формировании любого раунда кода суммы, кроме самого младшего, что приводит к увеличению времени формирования кода суммц. Кроме того, такие сумматоры обладают болыиим количеством оборудования. Наиболее близким аналогом по технической сущности к изобретению явлаегся комбинационный двухразрядный сумматор, старший и младший разряды которого содержат по одному элементу И-ИЛИ-НЕ, причем к первому и второму входам первой и второй группы входов элемента И- ИЛИ-НЕ старшего разряда подключены соответственно инверсные значения старшего и младшего разрядов первого и второго операндов з . Недостатком такого сумматора являет ся то, что при суммировании )авухзаряд- ных чисел с определенным значением порога (например, равного двум) часть оборудования в нем оказывается избыточной. Целью изобретения является уменьше- ние количества-оборудования при суммирб вании двухраэряшных чисел с опрепеленным значением порога, равного двум. Для постижения этой цели к третьему и чегвергому входам первой группы входов элеменга И-ИЛИ-НЕ младшего рааря да подключены инверсные значения стар ших разрядов первого и второго операндов, к третьему входу второй группы вхо дов этого элемента подключено инверсное значение старшего разряда первого, опера да, а к входам третьей группы входов инверсные значения младших разрядов пер вого и второго операндов и старшего раэ ряда операнда, к третьим входам первой н групп входов элемента старшего подключены соответственно инверсные значения старших резрядоё второго и первого опера дов. 6 84 На чертеже представлена функциональ ная схема двухра ядного комбинационного сумматора. Младший разряд сумматора выполнен на элементе И-ИЛИ-НЕ Ij. старший разряд на элементе И-ИЛИ-НЕ 2. К входам элементов И-И71И-НЕ 1 и 2 подключены шины младшего разряда первого слагаемого 3, младшего разряда второго слагаемого 4, младшего инверсноххэ разряда первого слагаемого, младшего инверсного разряда второго слагаемого 6, старшего инверсного разряда первого слагаемого 7 старшего инверсного jaTOooro спа гаемого 8. элемента И-ИЛИ-НЕ 1 подключен к первому выходу сумматора 9, выход элемента И-ИЛИ-НЕ 2 подключен ко второму выходуСумматора 1О. Состояния выходов сумматора в зависимости от кодов сяагаекоах свалены в табл- ду i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения @ -разрядных чисел | 1986 |

|

SU1374217A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Арифметическое устройство | 1985 |

|

SU1305662A2 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Устройство для суммирования двоично-десятичных кодов | 1977 |

|

SU684542A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1108440A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

При поступлении на сумматор кодов слагаемых, соответствующих первой строке таблицы на вцходах сумматора будет сформирован код ОО. При поступлении на сумматор Чкодов слагаемых, соответс вуюших второй и пятой строке таблицы, на выходах сумматора будет сформирован

код О1. При поступлении на сумматс кодов слагаемых. Соответствующих третьейг шестой и девятой строке таблицы, на выходах сумматора будет сформирован код Ю. При поступлении на сумматор кодов, соответствующих четвертой, сед1 мой, восьмой, десятой, одиннадцатой и т.д. строке таблицы, на выходах сумматора формируется код 11. Как видно из таблицы, во всех случаях, когда сумма двух слагаемых равна или более трех, сум магор формирует код суммы 11. Предложенный сумматор сокращает чнспо элементов И-., не требует допол нительных аппаратурных средств на формирование признака переполнения разрядной сетки, позволяет присвоить результатам, величина которых более TpeXj. одно и го же кодовое значение 11, что гаюке позволяет сократить число элементов И-ИЛИНЕ. Формула йзобрегениа Комбинационный двухра ядный сумматор, старший и младший которого содержат по одному элементу И-ИЛИ-НЕ, Iпричем к первому и второму входам первой и агорой групп входов элемен га И-ИЛИНЕ младшего подключены соотвег сгвенно .пр51мые и инверсные значения младших рафядов операндов, а к первому и второму входам первой н второй групп входов элемента И-ИЛИ-НЕ старшего раэрядэ подключены соответственно инверсные значения старшего и младшего разрядов и второго операндов, о т л и ч а - ю ш R и с я тем, что, с целью уменьше- 6 786 кия количества оборудования при суммировании двухразрядных чисел с определенным значением порога, равного двум, к третьему и четвертому входу первой группы входов элемента И-ИЛИ-НЕ младшего разряда подключены инверсные значения старших разрядов первого и второго операндов, к третьему входу второй группы входов этого элемента подключено инверсное значение старшего раунда первого операнда, а к входам третьей группы входов - инверсные значениа младших разрядов первого и второго операндов и старшего разряда второго операнда, к третьем входам первой и второй групп входов элемента И-ИЛИ-НЕ старшего решала подключены . соответственио инверсные значения старших разрядов второго я первого операндов. Источники ннформасин, принятые во вкиманке при экспертизе: 1.Каган Б. М. и /ф. Цифровые вычислительны машины R системы. М., , 197О, с. 228, рис. 4.7. 2.ГЬпериов А. А. Логические основы ЦВТ. М., Сов. радио , 1972, с. 164165. 3.Голышев Л. К. Структурная теория машин, М., Энергия, с. 271273.

Авторы

Даты

1978-10-05—Публикация

1976-09-16—Подача