Oiiik 4 U СП 00

Изобретение относится к вычислительной технике и может быть использовано для вычисления сложных математических функций в быстродействующих специализированных процессорах.

Цель изобретения - расширение области применения цифрового функционального преобразователя за счет дополнительного воспроизведения моно- тонне возрастающих чётных и нечетных функций.

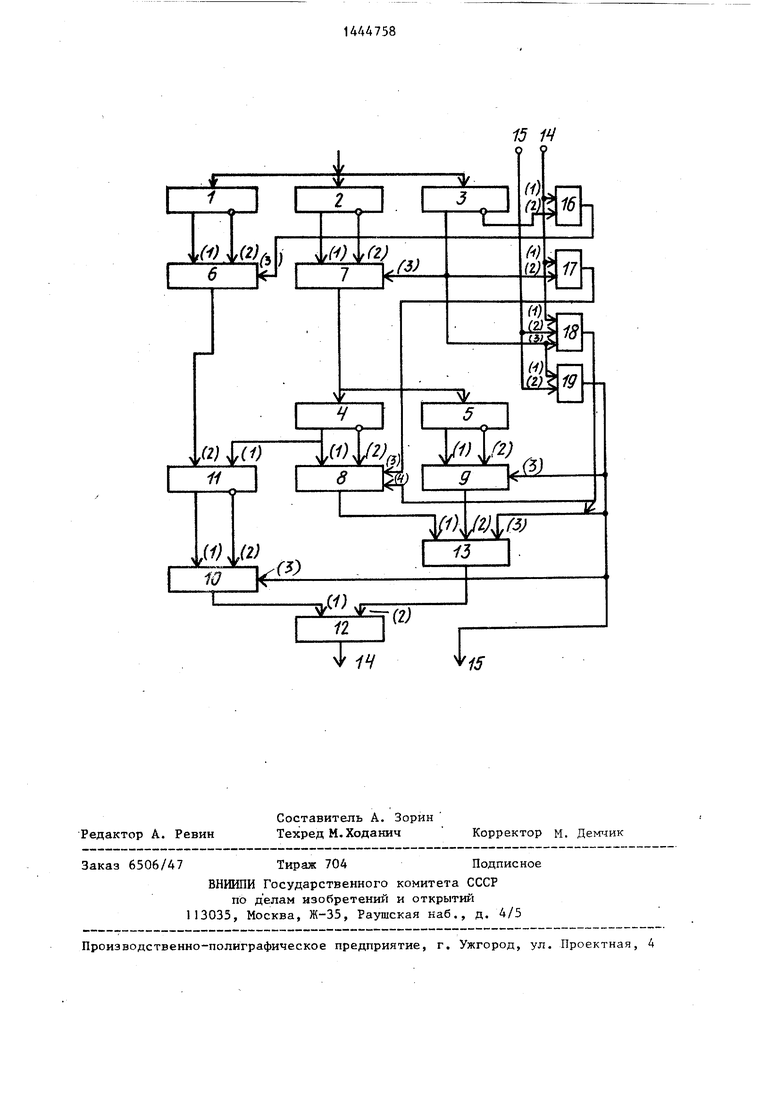

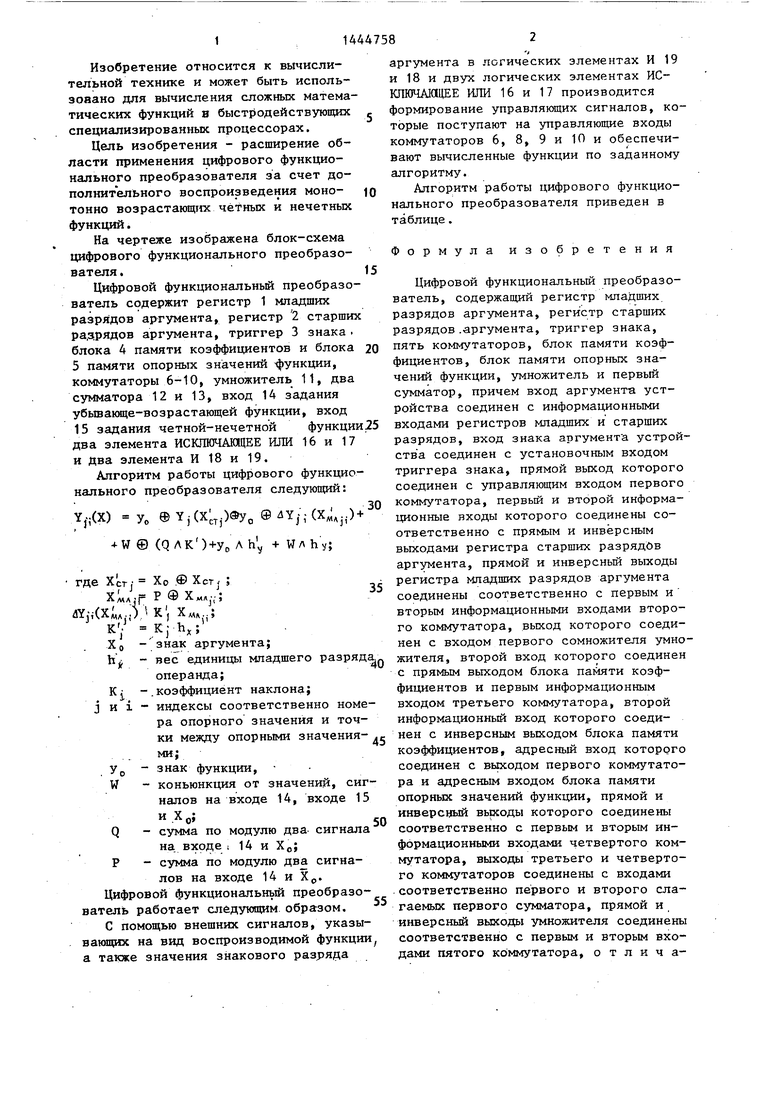

На чертеже изображена блок-схема цифрового функционального преобразователя.

Цифровой функциональньй преобразователь содержит регистр 1 младших разрядов аргумента, регистр 2 старших разрядов аргумента, триггер 3 знака. блока 4 памяти коэффициентов и блока 5 памяти опорных значений функции, коммутаторы 6-10, умножитель 11, два сумматора 12 и 13, вход 14 задания убьшающе-возрастающей функции, вход 15 задания четной-нечетной функции два элемента ИСКШНАЩЕЕ ИЛИ 16 и 17 и два элемента И 18 и 19.

Алгоритм работы цифрового функционального преобразователя следующий:

Yj-i(X) у, ®Yj(x;,j)®y @4Yj;(X;,j.)+ -i-W © (q ЛК )+Ур л h + Ил hy;

35

40

45

де X cTj Хо .® Хсг. ;

XMAJJ Р ®

{i(X|i,A..; К) XMK.. К / К|Ь,; Хо - знак аргумента; hj - вес единицы младшего разряда

операнда; К; -.коэффициент наклона; j и i - индексы соответственно номера опорного значения и точки между опорными значениями;

Ур - знак функции, W - коньюнкция от значений, сигналов на входе 14, входе 15 и Q - сумма по модулю два сигнала

на. входе i 14 и Хо; Р - сумма по модулю два сигналов на входе 14 и Х,,. Цифровой функциональньй преобразователь работает следующим образом.

С помощью внешних сигналов, указывающих на вид воспроизводимой функции, а также значения знакового разряда

55

0 5

°

5

0

5

5

аргумента в логических элементах И 19 и 18 и двух логических элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 16 и 17 производится формирование управляющих сигналов, которые поступают на управляющие входы коммутаторов 6, 8, 9 и 10 и обеспечивают вычисленные функции по заданному алгоритму.

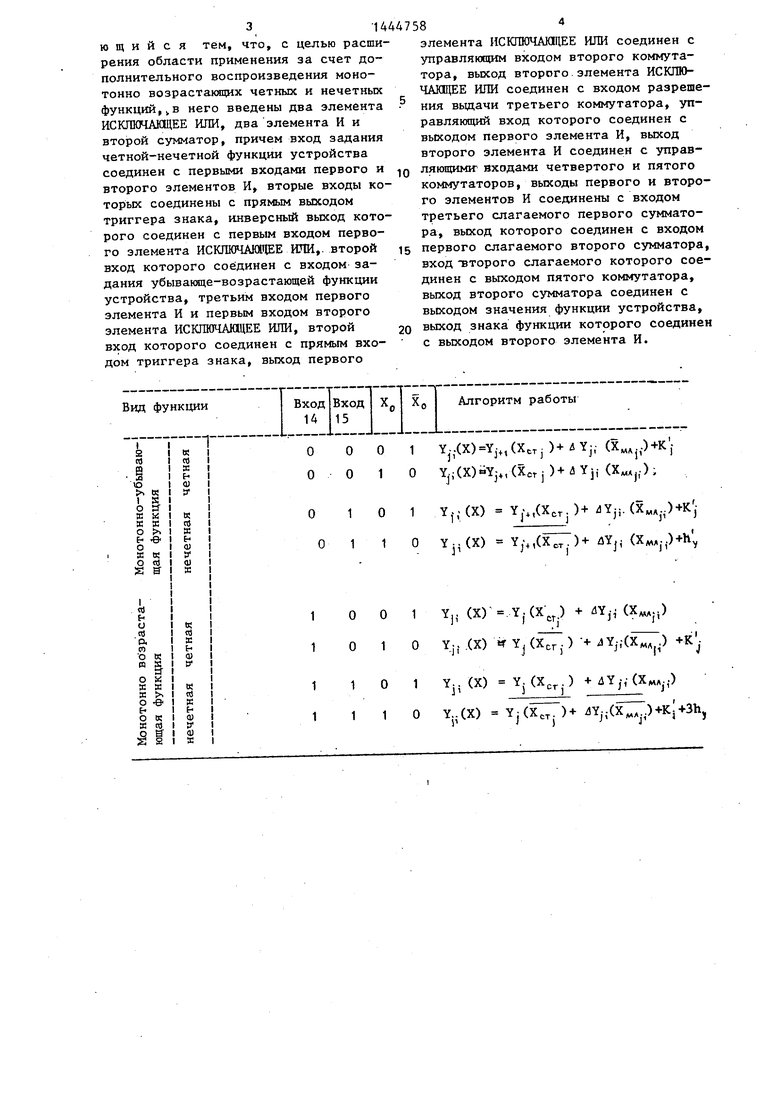

Алгоритм работы цифрового функционального преобразователя приведен в таблице.

Формула изобретения

Цифровой функциональный преобразователь, содержащий регистр младших. разрядов аргумента, регистр старшргк разрядов .аргумента, триггер знака, пять коммутаторов, блок памяти коэффициентов, блок памяти опорных значений функции, умножитель и первый сумматор, причем вход аргумента устройства соединен с информационными входами регистров младших и старших разрядов, вход знака аргумента устройства соединен с установочным входом триггера знака, прямой выход которого соединен с управляющим входом первого коммутатора, первый и второй информационные входы которого соединены соответственно с прямым и инверсным выходами регистра старших разрядов аргумента, прямой и инверсньй выходы регистра младших разрядов аргумента соединены соответственно с первым и вторым информационными входами второго коммутатора, выход которого соединен с входом первого сомножителя умножителя, второй вход которого соединен с прямым выходом блока памяти коэффициентов и первым информационным входом третьего коммутатора, второй информационный вход которого соединен с инверсным выходом блока памяти коэффициентов, адресный вход которого соединен с вькодом первого коммутатора и адресным входом блока памяти опорных значений функции, прямой и инверсный вькоды которого соединены соответственно с первым и вторым информационными входами четвертого коммутатора, выходы третьего и четвертого коммутаторов соединены с входами соответственно первого и второго слагаемых первого сумматора, прямой и инверсный выходы умножителя соединены соответственно с первым и вторым входами пятого коммутатора, о т л и ч аю щ и и с я тем, что, с целью расширения области применения за счет дополнительного воспроизведения монотонно возрастакицих четных и нечетньк функций,в него введены два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента И и второй сумматор, причем вход задания четной-нечетной функции устройства соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с прямым выходом триггера знака, инверсный выход которого соединен с первым входом первого элемента ИСКЛЮЧАКХЧЕЕ ИЛИ,, второй вход которого соединен с входом задания убыванлце-возрастающей функции устройства, третьим входом первого элемента И и первым входом второго элемента ИСКПЮЧАК1ЦЕЕ ИЛИ, второй вход которого соединен с прямым вхо- дом триггера знака, выход первого

элемента ИСКЛЮЧАИЦЕЕ ИЛИ соединен с управляющим входом второго коммутатора, выход второго.элемента ИСКЛЮ- ЧАЖЩЕ ИЛИ соединен с входом разрешения вьщачи третьего коммутатора, управляющий вход которого соединен с выходом первого элемента И, выход второго элемента И соединен с управ- ляющими входами четвертого и пятого коммутаторов, выходы первого и второго элементов И соединены с входом третьего слагаемого первого сумматора, выход которого соединен с входом первого слагаемого второго сумматора, вход твторого слагаемого которого соединен с выходом пятого коммутатора, выход второго сумматора соединен с выходом значения функции устройства, выход знака функции которого соединен с выходом второго элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Функциональный преобразователь | 1988 |

|

SU1541629A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1001092A1 |

| Функциональный преобразователь | 1988 |

|

SU1501021A1 |

| Устройство для вычисления функций | 1987 |

|

SU1472901A1 |

| Цифровой генератор гармонических функций | 1983 |

|

SU1156044A1 |

Изобретение относится к области вычислительной техники и может быть использовано для вычисления сложньпс математических функций в быстродействующих специализированных процессорах во многих Ьбластях народного хозяйства. Целью изобретения является расширение области применения за счет дополнительной возможности воспроизведения монотонно возрастающих четных и нечетных функций. Цифровой функциональный преобразователь состоит из регистров младших и старших разрядов аргумента, триггера знакового разряда аргумента, блока памяти коэффициентов, блока памяти опорных значений функции, пяти коммутаторов, умножителя, двух сумматоров, двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и двух элементов И. 1 ил. 1 табл. о (Л

| Цифровой функциональный преобразователь | 1982 |

|

SU1027732A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-07-01—Подача