10

1251187

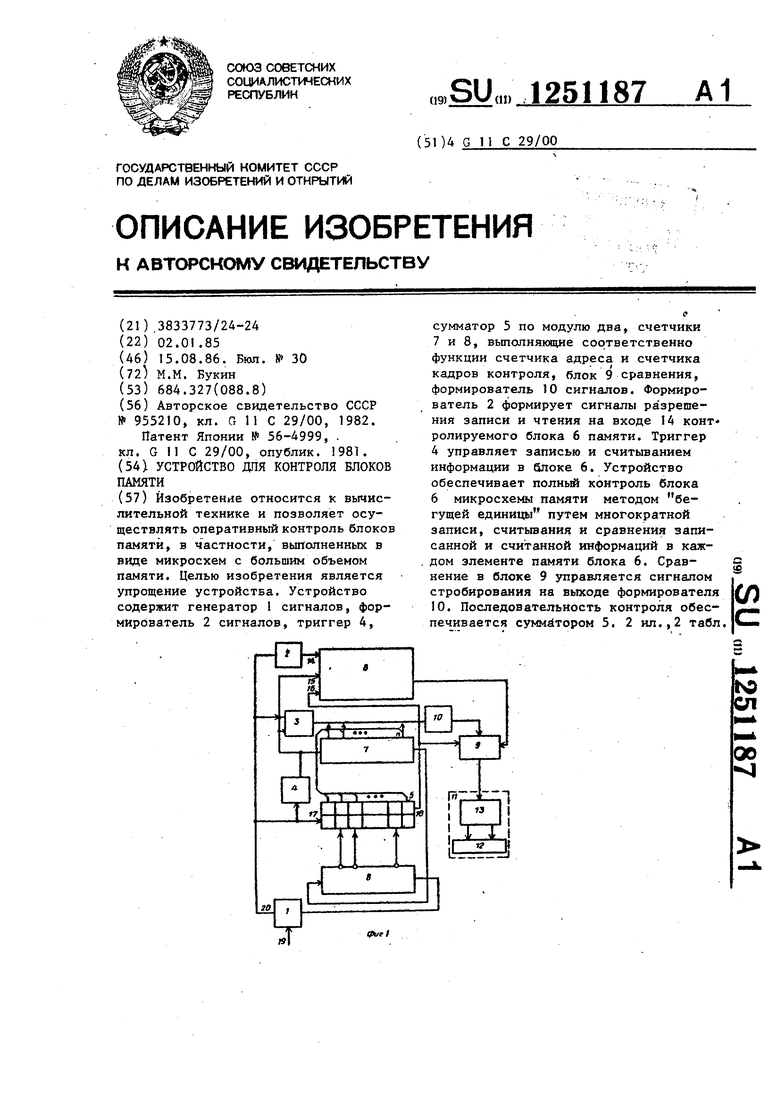

Изобретение относится к вычислиельной технике и может быть испольовано для оперативного контроля локов памяти, в частности, выполенных в виде микросхем с большим бъемом памяти.

Цель изобретения - упрощение стройства.

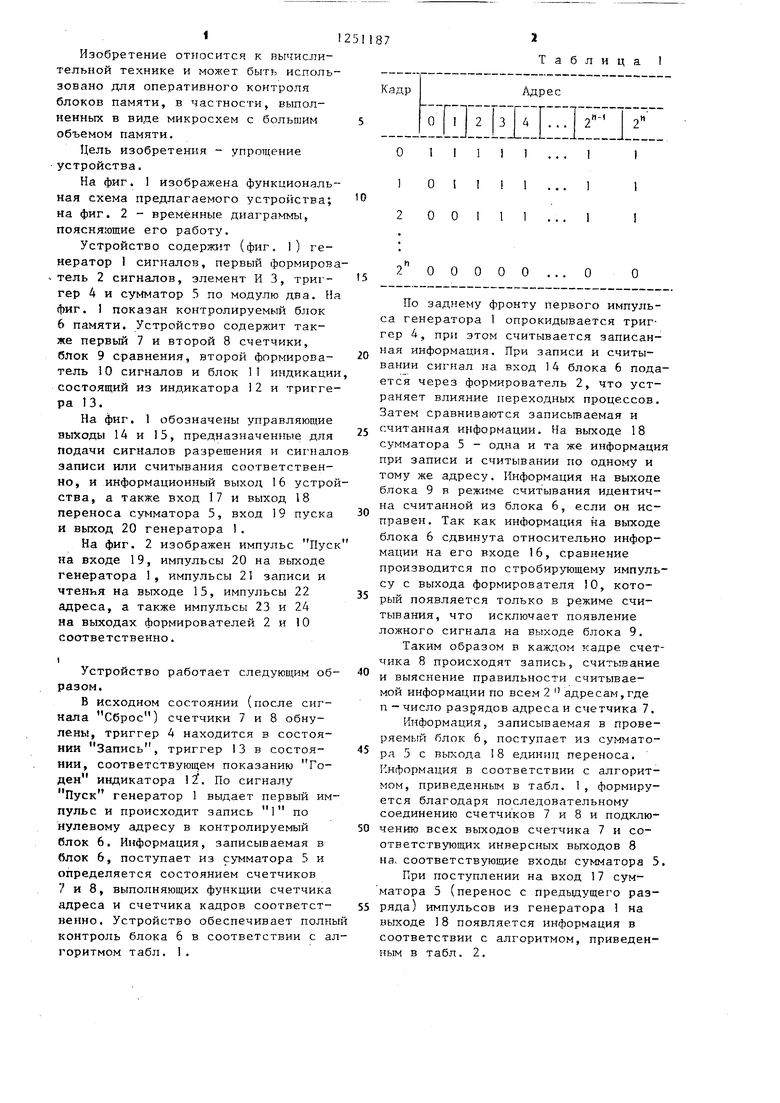

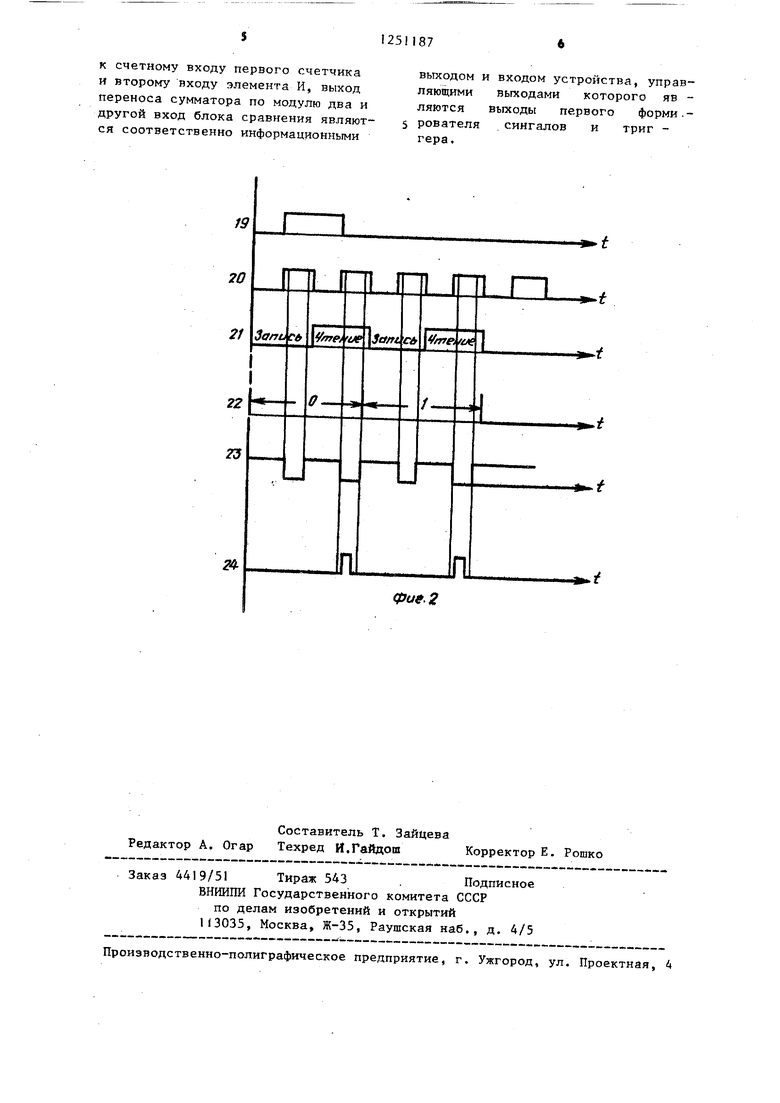

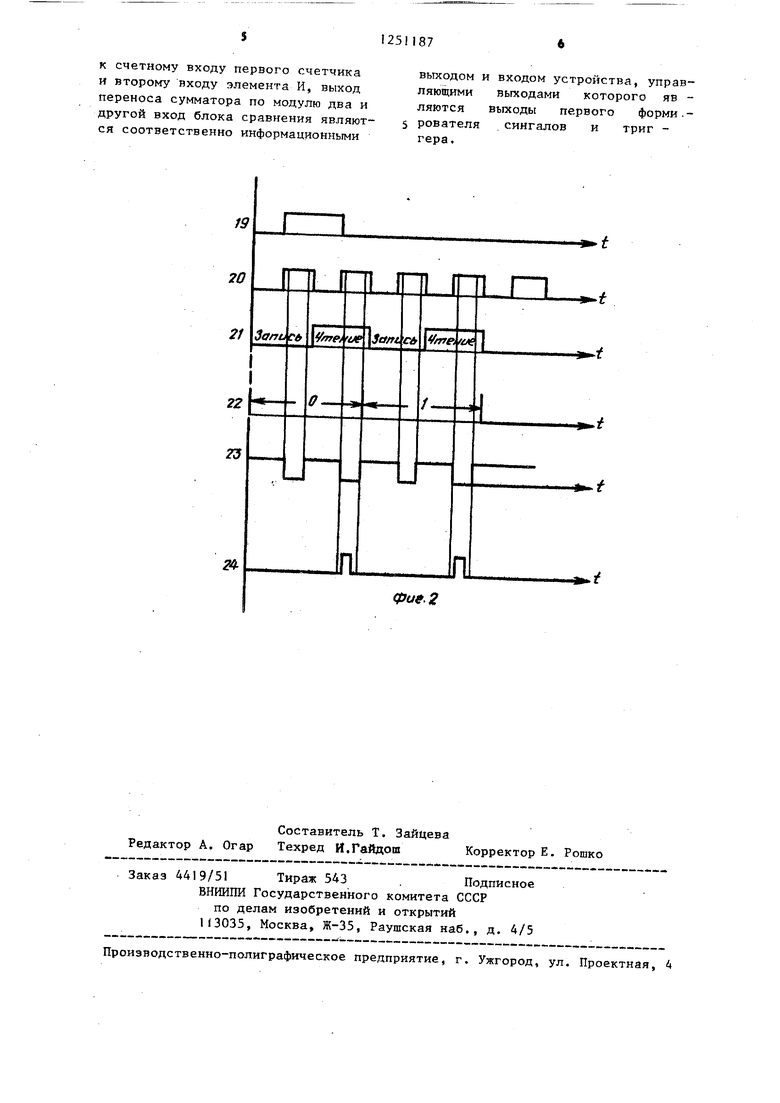

На фиг. изображена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содержит (фиг. 1) генератор 1 сигналов, первый формирова- тель 2 сигналов, элемент И 3, триггер 4 и сумматор 5 по модулю два. На фиг. показан контролируемый блок 6 памяти. Устройство содержит также первый 7 и второй 8 счетчики, блок 9 сравнения, второй формирователь 10 сигналов и блок 11 индикации, состоящий из индикатора 12 и триггера 13.

На фиг. 1 обозначены управляющие выходы 1А и 15, предназначенные для подачи сигналов разрешения и сигналов записи или считывания соответствен15

20

25

с ге на ва ет ра сч су пр то н п м п с т л

НО, и информационный выход 16 устройства, а также вход 17 и выход 18 переноса сумматора 5, вход 19 пуска и выход 20 генератора 1.

На фиг. 2 изображен импульс Пуск на входе 19, импульсы 20 на выходе генератора 1, импульсы 21 записи и чтенья на выходе 15, импульсы 22

адреса, а также импульсы 23 и 24 на выходах формирователей 2 и 10 соответственно.

Устройство работает следующим образом.

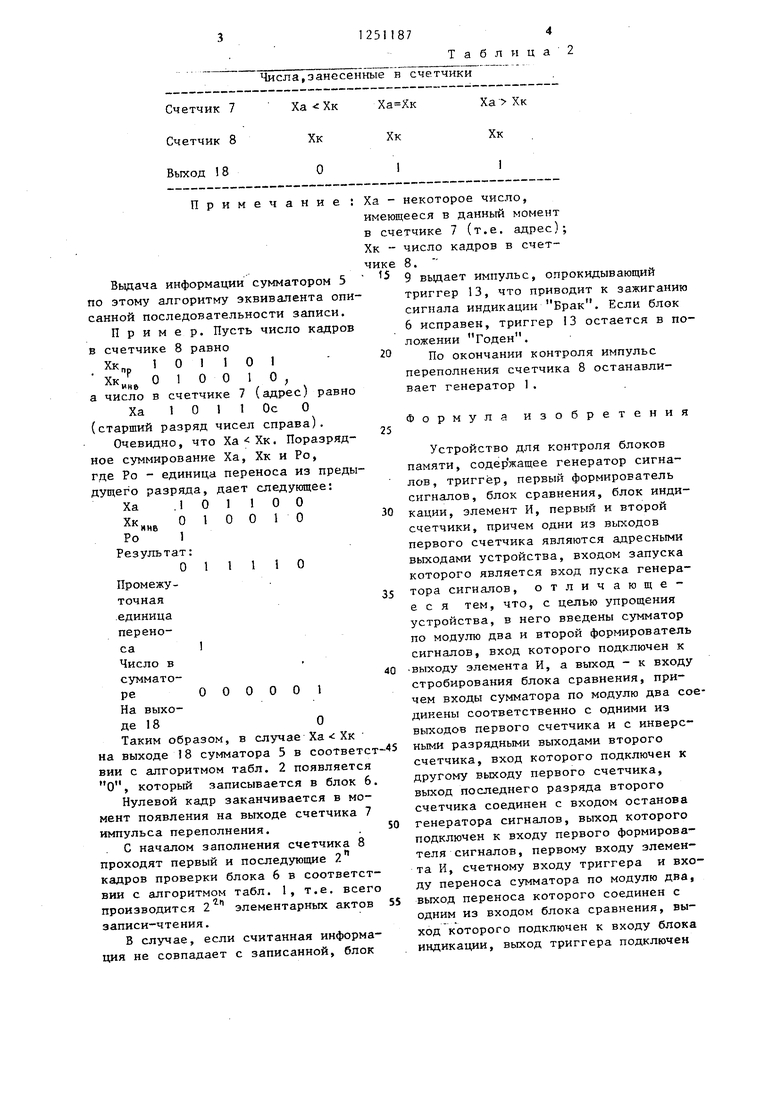

В исходном состоянии (после сигнала Сброс) счетчики 7 и 8 обнулены, триггер 4 находится в состоянии Запись, триггер 13 в состоянии, соответствующем показанию Годен индикатора 12f. По сигналу Пуск генератор 1 выдает первый импульс и происходит запись 1 по нулевому адресу в контролируемый блок 6. Информация, записываемая в блок 6, поступает из сумматора 5 и определяется состоянием счетчиков 7 и 8, выполняющих функции счетчика адреса и счетчика кадров соответственно. Устройство обеспечивает полны контроль блока 6 в соответствии с алгоритмом табл. 1.

Таблица 1

2

00000

О

О

По заднему фронту первого импульса генератора 1 опрокидывается триггер 4, при этом считывается записанная информация. При записи и считывании сигнал на вход 14 блока 6 подается через формирователь 2, что устраняет влияние переходных процессов. Затем сравниваются записываемая и считанная информации. На выходе 18 сумматора 5 - одна и та же информация при записи и считывании по одному и тому же адресу. Информация на выходе блока 9 в режиме считывания идентична считанной из блока 6, если он исправен. Так как информация на выходе блока 6 сдвинута относительно информации на его входе 16, сравнение производится по стробирующему импульсу с выхода формирователя 10, который появляется только в режиме считывания, что исключает появление ложного сигнала на выходе блока 9.

Таким образом в каждом кадре счетчика 8 происходят запись, считывание и выяснение правильности считываемой информации по всем 2 адресам,где п число разрядов адреса и счетчика 7.

Информация, записываемая в проверяемый блок 6, поступает из сумматора 5 с выхода 18 единиц переноса. Информация в соответствии с алгоритмом, приведенным в табл. 1, формируется благодаря последовательному соединению счетчиков 7 и 8 и подключению всех выходов счетчика 7 и соответствующих инверсных выходов 8 на, соответствующие входы сумматора 5.

При поступлении на вход 17 сум- матора 5 (перенос с предыдущего разряда) импульсов из генератора на выходе 18 появляется информация в соответствии с алгоритмом, приведенным в табл. 2.

Примечание

Вьщача информации сумматором 5 по этому алгоритму эквивалента описанной последовательности записи.

Пример. Пусть число кадров в счетчике 8 равно

Хк,

Хк.

1 О

пне а число в

01

1О ,

7 (адрес) равно 1 Ос О

01 1

100 счетчике

Ха 1 О 1 (старший разряд чисел справа).

Очевидно, что Ха i Хк. Поразрядное суммирование Ха, Хк и Ро, где Ро - единица переноса из преды дущег о разряда, дает следующее: 1100 0010

Ха Хк

мне

О 1

11110

.1

О

Ро 1 Результат О

Промежуточная.единица переноса

Число в сумматоре

На выходе 18

Таким образом, в случае на выходе 18 сумматора 5 в соответс ВИИ с алгоритмом табл. 2 появляется О, который записывается в блок 6 Нулевой кадр заканчивается в момент появления на выходе счетчика 7 импульса переполнения.

С началом заполнения счетчика 8 проходят первый и последующие 2 кадров проверки блока 6 в соответствии с алгоритмом табл. 1, т.е. всег гг

000001

о

элементарных актов

производится 2 записи-чтения.

В случае, если считанная информация не совпадает с записанной, блок

Таблица2

Ха - некоторое число, имеющееся в данный момент в счетчике 7 (т.е. адрес); Хк - число кадров в счетчике 8. 9 выдает импульс, опрокидывающий

триггер 13, что приводит к зажиганию сигнала индикации Брак. Если блок 6 исправен, триггер 13 остается в положении Годен.

По окончании контроля импульс переполнения счетчика 8 останавливает генератор 1.

Формула изобретения

Устройство для контроля блоков памяти, содер жащее генератор сигналов, триггер, первый формирователь сигналов, блок сравнения, блок индикации, элемент И, первый и второй счетчики, причем одни из выходов первого счетчика являются адресными выходами устройства, входом запуска которого является вход пуска генера- тора сигналов, отлич ающе- е с я тем, что, с целью упрощения устройства, в него введены сумматор по модулю два и второй формирователь сигналов, вход которого подключен к выходу элемента И, а выход - к входу стробирования блока сравнения, причем входы сумматора по модулю два соединены соответственно с одними из выходов первого счетчика и с инверсными разрядными выходами второго счетчика, вход которого подключен к другому выходу первого счетчика, выход последнего разряда второго счетчика соединен с входом останова генератора сигналов, выход которого подключен к входу первого формирователя сигналов, первому входу элемента И, счетному входу триггера и входу переноса сумматора по модулю два, выход переноса которого соединен с одним из входом блока сравнения, выход которого подключен к входу блока индикации, выход триггера подключен

к счетному входу первого счетчика и второму входу элемента И, выход переноса сумматора по модулю два и другой вход блока сравнения являются соответственно информационными

Составитель Т. Зайцева Редактор А. Огар Техред Й.Гайдош Корректор Е. Рошко

Заказ 4419/51 Тираж 543 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий П3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфипеское предприятие, г. Ужгород, ул. Проектная, 4

выходом и входом устройства, управляющими выходами которого яв - ляются выходы первого форми.- 5 рователя сингалов и триг - гера.

фи9-2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки графической информации | 1988 |

|

SU1674222A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для контроля интегральных микросхем оперативной памяти | 1984 |

|

SU1249588A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1981 |

|

SU1043731A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1325571A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1357998A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1647655A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

Изобретение относится к вычислительной технике и позволяет осуществлять оперативный контроль блоков памяти, в частности, выполненных в виде микросхем с большим объемом памяти. Целью изобретения является упрощение устройства. Устройство содержит генератор 1 сигналов, формирователь 2 сигналов, триггер 4, сумматор 5 по модулю два, счетчики 7 и 8, вьшолняющие соответственно функции счетчика адреса и счетчика кадров контроля, блок 9 сравнения, формирователь 10 сигналов. Формирователь 2 формирует сигналы разрешения записи и чтения на входе 14 конт ролируемого блока 6 памяти. Триггер 4 управляет записью и считыванием информации в блоке 6. Устройство обеспечивает полньй контроль блока 6 микросхемы памяти методом бегущей единицы путем многократной записи, считьгаания и сравнения записанной и считанной информации в каждом элементе памяти блока 6. Сравнение в блоке 9 управляется сигналом стробирования на выходе формирователя 10. Последовательность контроля обеспечивается сумматором 5. 2 ил.,2 табл. SS СО С

| Устройство для контроля блоков памяти | 1981 |

|

SU955210A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для избирательного управления с одного конца однопроводной линии несколькими реле | 1918 |

|

SU981A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-02—Подача